(54) МНОГОРАЗРЯДНСе УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1979 |

|

SU922728A1 |

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство для суммирования | 1979 |

|

SU868750A1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

| Одноразрядный сумматор | 1977 |

|

SU734681A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1129636A1 |

| Ассоциативный процессорный модуль | 1981 |

|

SU1015390A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

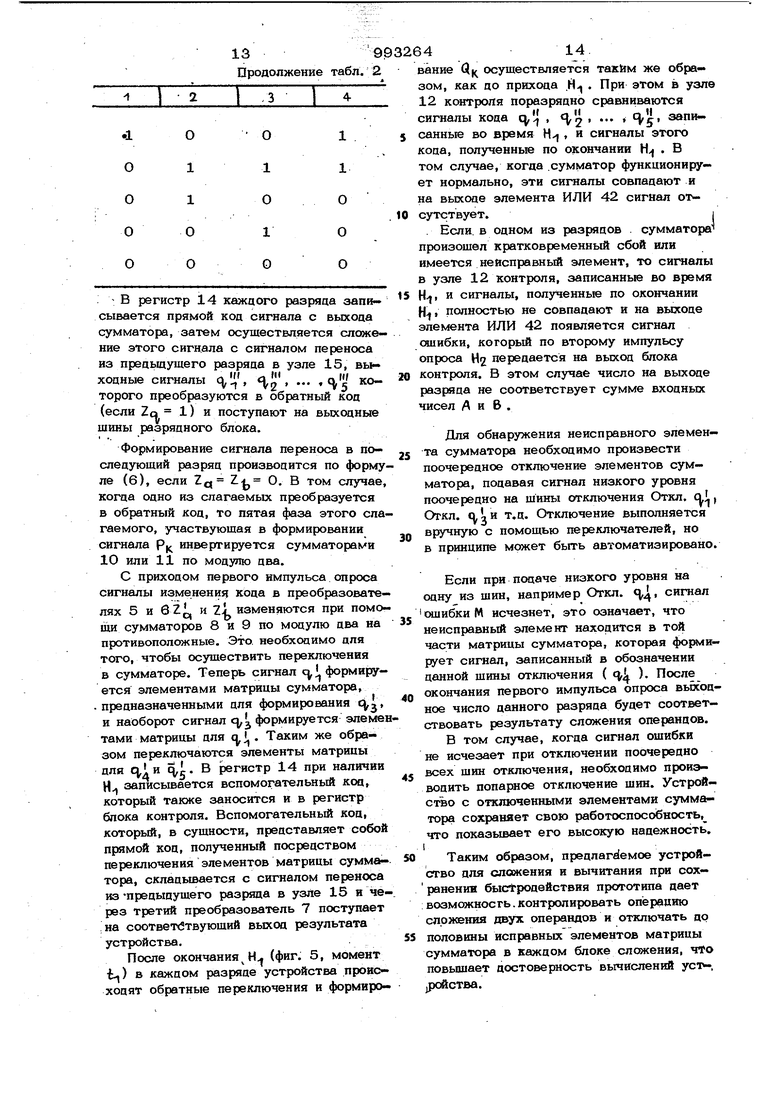

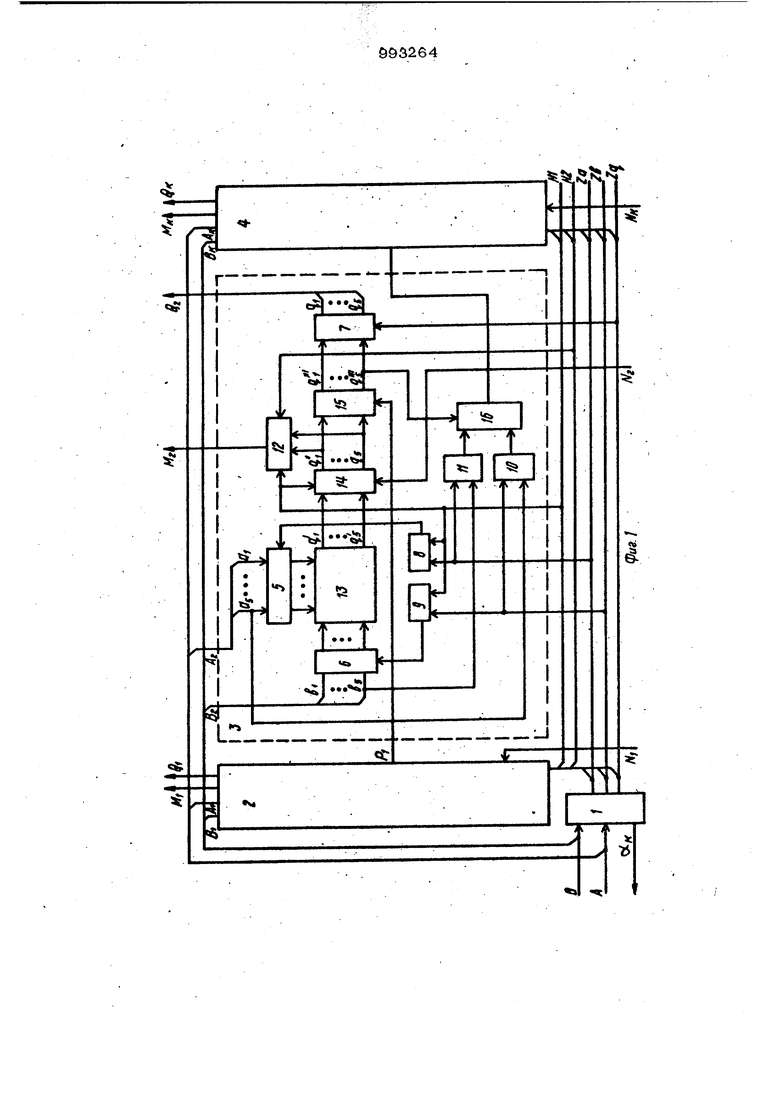

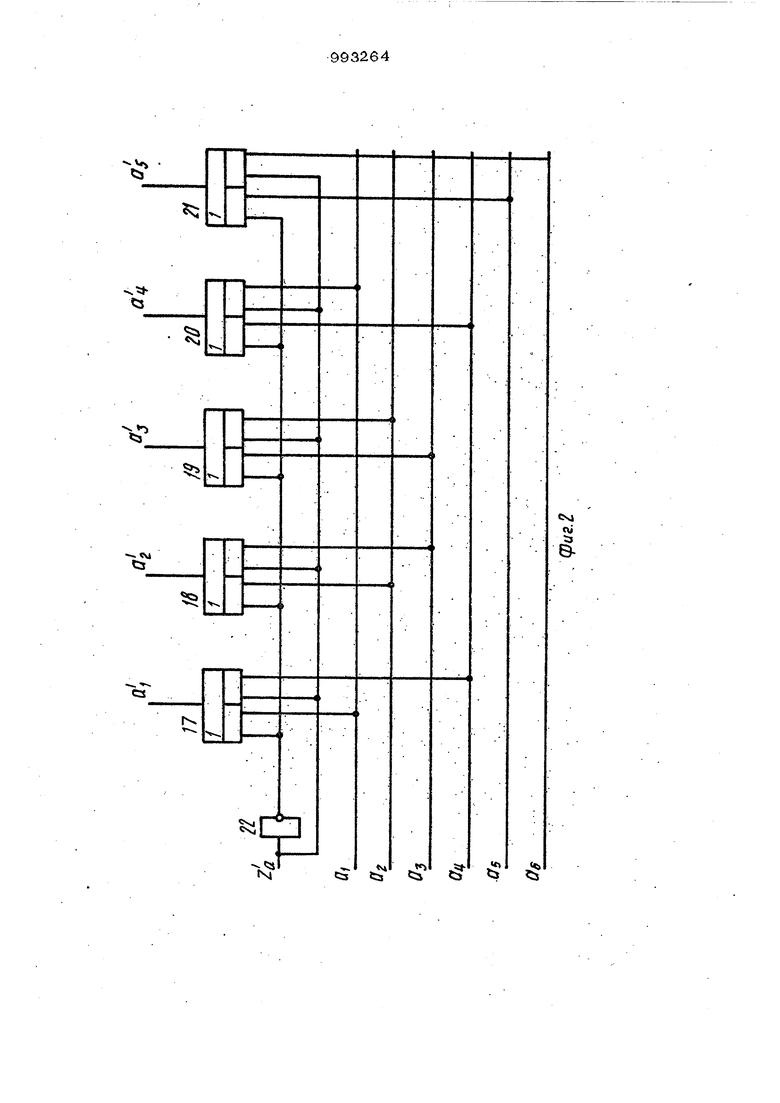

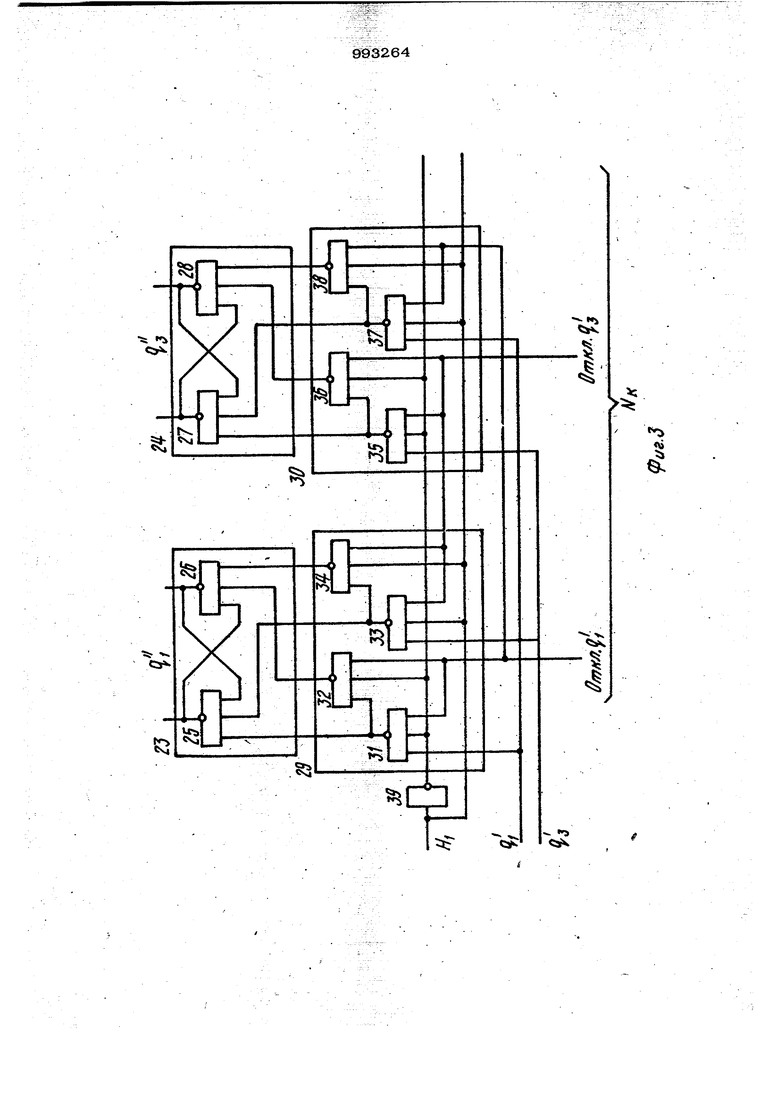

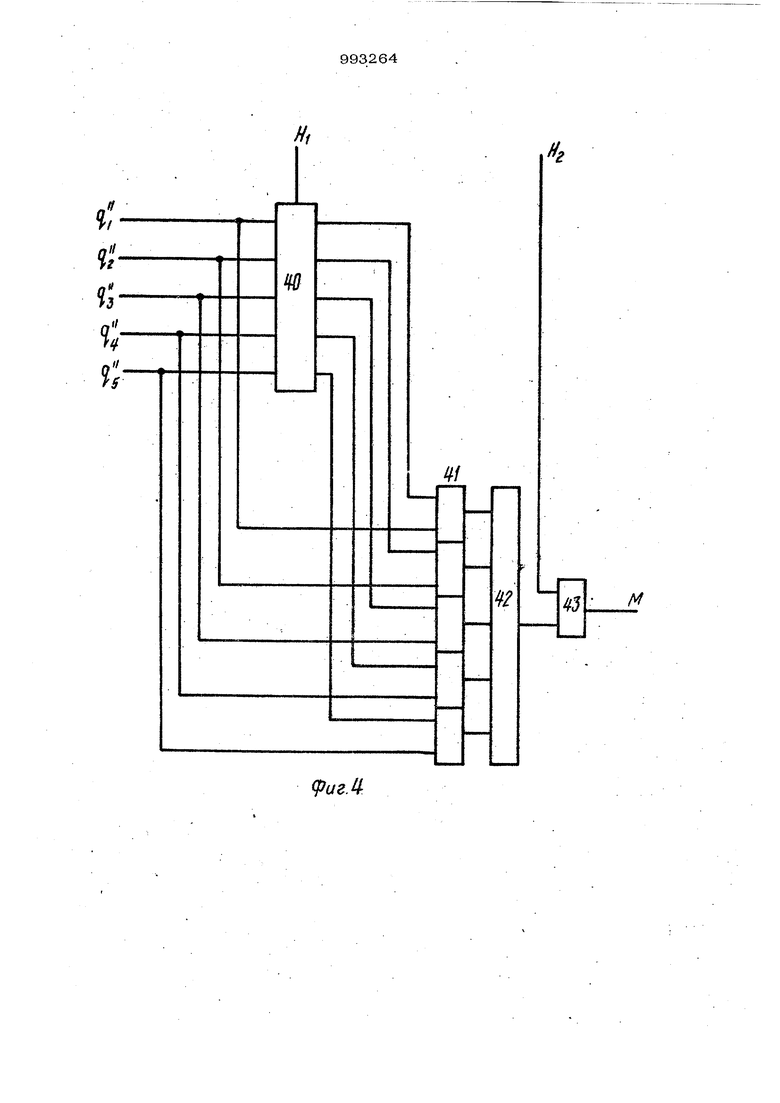

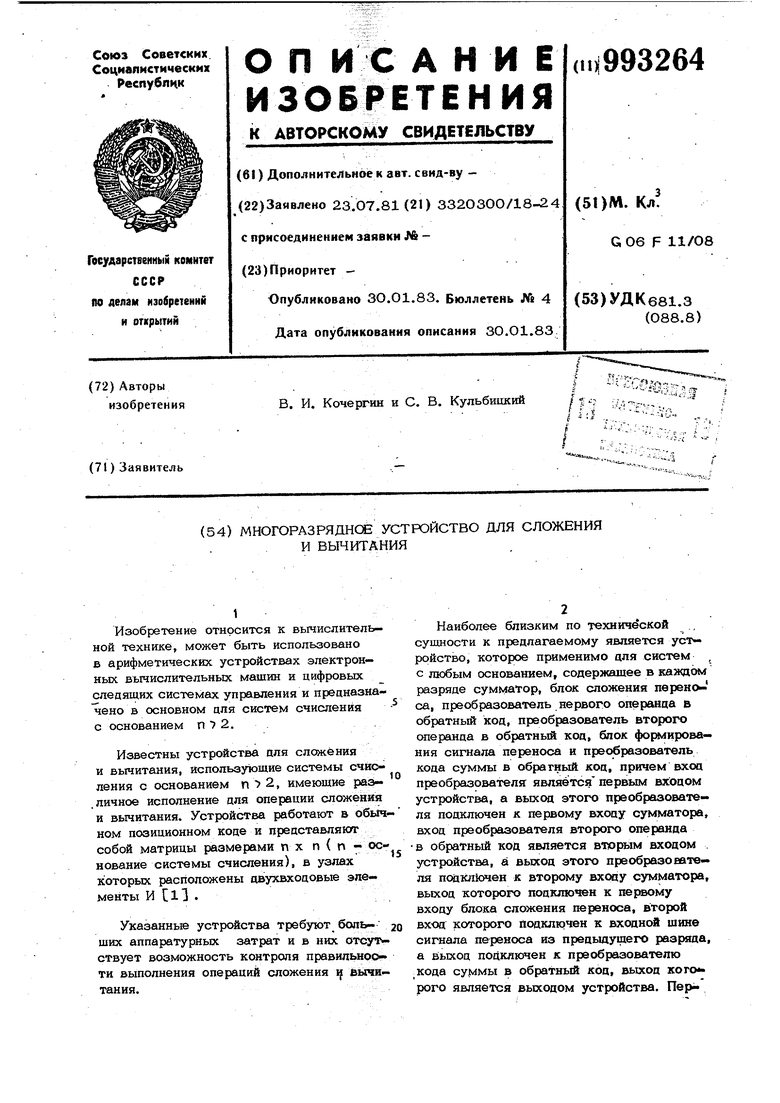

Изобретение относится к вычислительной технике, может быть использовано в арифметических устройствах электронных вычислительных машин и цифровых следящих системах управления и прецназначено в основном для систем счисления с основанием п 7 2. .. Известны устройства для сложения и вычитания, использующие системы счисления с основанием п 2, имеющие раз- .личное исполнение для операции сложения и вычитания. Устройства работают в обыч ном позиционном коде и представляют собой матрицы размерами п х п ( п - основание системы счисления), в узлах которых расположены двухвходовые элементы И 11 . Указаннью устройства требуют больщих аппаратурных затрат и в них отсутствует возможность контроля правильности выполнения операций сложения щ вычнтания. Наиболее близким по технической сущности к предлагаемому является уст ройство, которое применимо для систем с любым основанием, содержащее в каждом разряде сумматор, блок сложения парено са, преобразователь нервого операнда в обратный код, преобразователь второго сшеранда в обратный код, блок формирования сигнала переноса и преобразователь кода суммы в обратный код, причем вход преобразователя является первым входом устройства, а выход этого преобразователя подключен к первому входу сумматора, вход преобразователя второго операнда в обратный код явл$ются вторым входом . устройства, а выход этого преобразователя подкл1очен к второму входу сумматора, выход которого подключен к первому входу блока сложения переноса, второй вход которого йодключен к входной шине сигнала переноса из предыдущего разряда, а выход подключен к преобразователю кода суммы в обратный код, выход кого рого является выходом устройства. Пер. вый, второй и третий входы блока формирования переноса подключены к вьсходным шинам соответственно преобразователей первого и второго операнда в обратный код и блока сложения переноса, а выход блока формирования переноса подклю чен к выходной шине сигнала переноса в последующий разряд. Формирование сигналов Z,, Zai подаваемых на управля ющие входы соответственно преобразователей кода первого, второго операнда и ) кода суммы в обратный код, осуществляется блоком сравнения операндов 2 . Известное устройство для сложения и вычитания не позволяет осуществлять контроль правильности вЬшолнения операций сложения и вычитания, быстро обнаруживать и отключать вышедшие из строя элементы сумматора. Цель изобретения - повышение достоверности вычислений. Поставленная цель достигается тем, что в многоразрядное устройство для сложения и вычитания, содержащее блок сравнения операндов и К блоков сложения, каждый из которых содержит сумматор, три преобразователя прямого кода в обратный, формирователь сигнала пере носа, узел сложения переноса, причем входы блока сравнения операндов являются входами первого и второго операндов устройства, входы первых преобразователей прямого кода в обратный :Всех блоков сложения соединены с входами соответст вующих разрядов первого операнда устрой ства, входы вторых преобразователей прямого кода в обратный всех блоков сложения соединены с входами соответст вующих разрядов второго операнда устро ства, выходы третьих преобразователей прямого кода в обратный всех блоков сложения являются выходами результата устройства, в каждом блоке сложения первая и вторая группы входов сумматора соединены с группами выходов первого и второго преобразователей прямого коца в обратный соответственно, группа входов третьего преобразователя прямого кода в обратный соединена с группой выходов узла сложения переноса, старший разряд группы вьрсоцов узла сложения переноса соединен с первым входом формирователя сигнала переноса, первый выход блока сравнения операндов соедине с входами третьих преобразователей прямого кода в обратный всех блоков сложения, второй выход блока сравнения операндов является выходом знака результата устройства, выход формирователя сигнала переноса i -го блока сложения (1 1 К-1) соединен с входом узла сложения переноса ( i + 1)-го блока сложения, введены в каждый блок сложения регистр, узел контроля и четыре сумматора по модулю два, причем в каждом блоке сложения выходы первого и второго сумматоров по модулю два соединены с входами первого и второго преобразователей прямого кода в обратный соответственно, выходы третьего и четвертого сумматоров по модулю два соединены соответственно с вторым и третьим входами формирователя сигнала переноса, группа выходов сумматора соединена с первой группой входов регистра, группа выходов которого соединена с группами входов узла контроля и узла сложения переноса, третий выход блока сравнения операндов соединен с первыми входами первого и третьего сумматоров по модулю два всех блоков сложения, четвертый выход блока сравнения операндов соединен с первыми входами второго и четве{ того сумматоров по модулю два всех блоков сложения, в каждом блоке сложения вторые входы третьего и четвертого сумматоров по модулю два соединены с входами старших разрядов группы входов первого и второго преобразователей прямого кода в обратньй соответственно, первый вход устройства соединен с вторыми входами первого и второго сумматоров по модулю два, входами регистров и первыми входами узлов контроля всех блоков сложения, второй вход устройства соединен с вторыми входами узлов контроля всех блоков сложения, вторые группы входов регистров всех блоков сложения являются управляющими входами устройства, выходы узлов контроля всех разрядных блоков сложения являются выходами неисправности устройства. Кроме того, узел контроля содержит регистр, группу сумматоров по модулю два, элемент ИЛИ, элемент И, причем первые входы сумматоров по модулю два группы соединены с входами данных соответствующих разрядов регистра и образуют группу входов узла контроля, выходы регистра соединены с вторыми входами соответствующих сумматоров по модулю ава группы, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого является выходом узла контроля, управляющий вход регистра и второй вход элемента И являются соотве ственно первым и вторым входами узла контроля. Устройство может функционировать в любом коде и системе счисления с лю- бым основанием В качестве примера удобнее рассматривать работу устройства в многофазном коде, поскольку этот код обладает высокой контролеспособностью и возможностью исправления ошибок любого арифметического или логического устройства. Эти свойства многофазного кода связаны с его структурой. Примем основание системы fr- равным десяти (пятифазный код). На фиг. 1 изображена ст гктурная схема устройства; на фиг. 2 - функциональная схема преобразователя прямого пятифазного кода в обратньй; на фиг. 3 - функциональная схема двух разрядов ре- гистра; на фиг. 4 - функциональная схе- ма узла контроля; на фиг. 5 - временная диаграмма работы узла контроля. Устройство содержит блок 1 сравнения операндов, блоки 2 - 4. сложения, преобразователи 5-7 прямого (пятифазно- го) кода в обратный, сумматоры 8 11 . по модулю два, узел 12 контроля, сумма тор 13, регистр 14, узел 15 сложения переноса, формирователь 16 сигнала пе- реноса. Преобразователь прямого пятифазного кода в обратный содержит элементы 2И-ИЛИ 17 - 21 и элемент ИЛИг-НЕ 22. Два разряда регистра 14 содержат два f S-триггера 23 и 24, состоящие из элементов И-НЕ 25 - 28, два узла 29 и ЗО управления, состоящие из элементов И-НЕ 31-38, и элемент ИЛИ-НЕ 39. Узел 12 контроля содержит регистр 4О, группу 41 сумматоров по модулю два, элемент ИЛИ 42, элемент И 43. Блок сложения содержит сумматор 13, . на входы которого через преобразователи 5 и 6 прямого пятифазного кода в обратный подаются операнды Л В представленные в пятифазном коде. На выходе сумматора установлен регистр 14, который управляется первьгм импульсом опроса Н, , поступающим с первого входа устройства. При отсутствии Ни в триггеры . регистра записьшаются сигналы 2 2 - 1 Я- Я2° tj, 4,5 Р наличии Н в регистр записывается вспомогательный код. На выходе регистра расположен узел 15 сложения переноса, осуществляющий сложение выходных сигналов регистра 14 и сигнала переноса Pjt.H3 предьщущего разрядного блока. Результат сложения , , ... .(Ц подается на входы третьего преобразователя 7 прямого пяти-фазнЪго кода в обратный, выход когорого является выходом результата цантэго разряда устройства. Формирователь 16 сигнала переноса вырабатьшает сигнал переноса РК а .по- ., следующий разряд. Для этого на его входы подаются сигналы пятых фаз опервнцов и сигнал пятой фазы узла 15 сложения переноса. В каждом блоке сложения устройства установлены четыре сумматора 8-11 по модулю два. Сумматоры 8 и 9 по модулю два управляют сменой кодов в пре- образователях 5 и 6 соответственно, для чего на их первые входы подаются сигналы 2дИ Z третьего и второго выходов блока 1 сравнения операндов, который на первом выходе формирует также сигнал Zq .управляющий работой третьего преобразователя 7 прямого кода в обрат- хй, а на вторые входы, сумматоров 8 и 9 по модулю два подается первый им пульс опроса Н . Сумматоры 10 и ll по модулю два управляютработой форМи- рователя 16 сигнала переноса, суммируя по модулю 2 соответственно сигналы 2 и а, . bj. Узел 12 контроля подключен к выходу регистра 14 и управляется первым и вторым импульсами опроса, которые поступают с первого и второго входов устройства соответственно. По первому импульсу опроса в узле 12 контроля осуществдаются поразрядное сравнение сигнала с выхода сумматора 13 , S-S сигнала, преобразованного во вспомогательный код. С приходом второго импульса опроса результат этого сравнения поступает на выход узла 12 контроля в виде сигнала М , который несет информацию о правильности вьшолнения операции суммирования операндов Л | и В . Общий цля всех блоков сложения блок 1 сравнения операндов формирует сигналы ZQ , 2|, Zo и знак выходного числа ain. На его входы подаются сигналы операндов А и & сигналы знаков операндов ct. Блоки 2 - 4 сложения имеют входные шины операндов А« и Q, щины отключения t и выходные щины результата сложения 79 сигнала контроля М . Разряцы соединены между собой по шинам переноса. Рассмотрим более подробно принципы построения и работу отдельных блоков устройства. Контролируемым узлом кажа го блока .сложения устройства является сумматор 13. Необходимость первоочер ного контроля именно сумматора обьяс- няется тем, что он наиболее сложен и требует самых больших из всех узлов устройства аппаратурных затрат. Связь между цифрами десятичного кода и сигналами фаз пятифазного кода выражается следующим образом: . ...v5, .,,vb; ...y7-, ... v8 5vGv...v9.(Я Логические выражения сигналов.фаз ре- зультата сложения будут иметь следующ вид:. ..-.-- . т - . з%«з V Vb b o vljjb 01 vKfega vb bd V Яг2-ЧЧ Vs ЧЧ 5 V Ъ- 2 4V3 ЧЧ«2 W-. Vs V5VV.«3

%. Ч«2 Ч%

,-44V 2V3 3V2 4V-l

,,-.

-t %

«2

-m-i m-2- «m

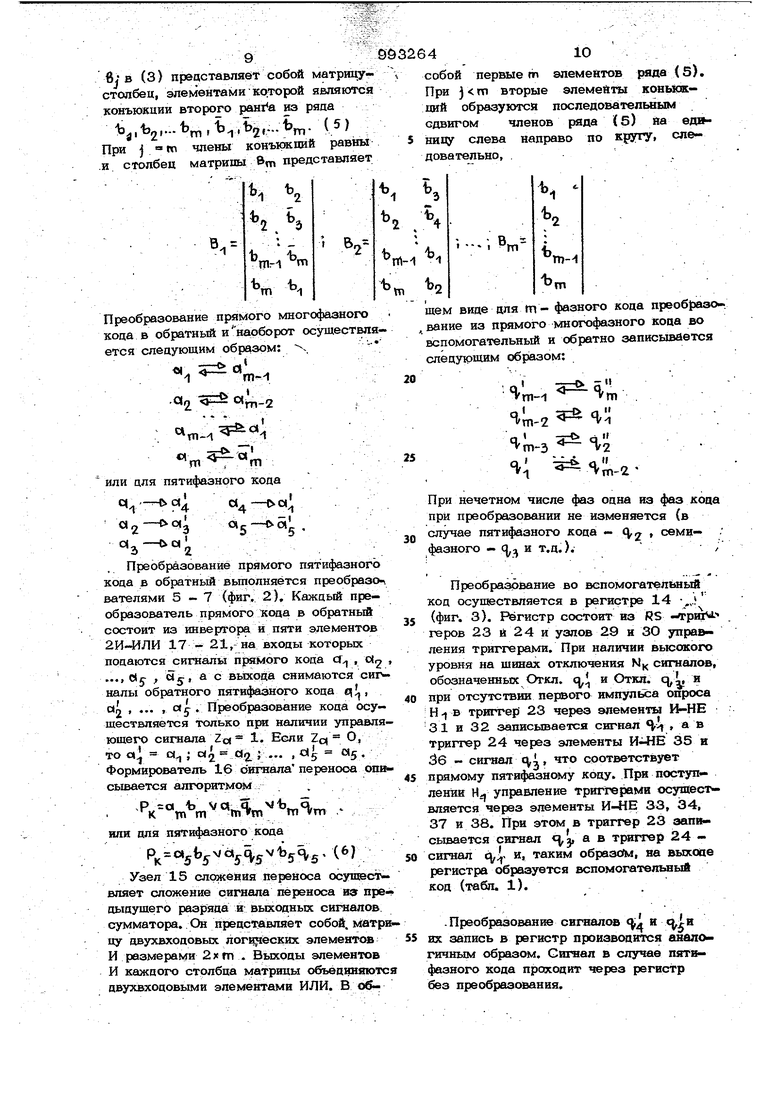

При 1 1 строки каждой последующей матрицы образуются сдвигом на единицу вторых элементов конъюкций в строках предьщущей матрицы слева направо по кругу. Тогда 8 , . Из логических выражений (2) очевиц- на реализация принципиальной схемы сумматора, работающего в многофазном Такой сумматор представляет собой . матрицу размерами п х т,в узлах которой расположены трехвходовые элементы И, на входы которых подаются сигналы фаз операндов А и В или их инверсии. Выходы элементов И каждого столбца матрицы объединяются с помощью десятивходовых элементов ИЛИ. Логическое выражение результата сложения чисел А и В в многс)фазном коде с любым основанием можно представить в матричной форме записи i f,2,...,m; НА,М ,2,...,m, где Ai - квадратная матрица размерами - 1л.ОС( А джмл 1- ..-.W. f.f элементами которой являются онъюкции второго ранга из ряда т.«ш-1.-Л,,-1.-.1- При i -1 элементы конъюкций равны и первая строка матрицы Л представляет собой первые ш элементов ряда (4). Последующие строки матрицы Л образуются сдвигом на единицу элементов ряда (4) слева направо по кругу, следовательно, 99&3 в; в (3) представляет собой матрицустолбец, элементами конторой являются конъюкции второго из ряда .,,..b. (5) При j № члены конъкждий равны .и столбец матрицы Вт представляет

; Вп,rt-1 ч

П) 2в4 собой первые m элементов ряда (5). При вторые элемейтъ конькжций образуются последовательным сдвигом членов ряда (5) на едв5 ницу слева направо по кругу, следовательно,.

Преобразование прямого многофазного кода в обратный и наоборот осуществляется следующим образом: .. Л

0

.

тм

.01 П±

,

«

а

«.

m или для пятифазнрго кода

щем виде для т- фазного кода преоб|разо-. ванне из прямого многофазного кода во вспомогательный и обратно записывается следующим образом:

20

m-2

Vm-s i

25

«VS,тп-2

«i

а.

о-З

г

Преобразование прямого пятифазного кода в обратный выполняется преобразо вателями 5-7 (фиг, 2), Каждьй преобразователь прямого кода в обратный состоит из инвертора и пяти элементов 2И-ИЛИ 17 - 21,- на входы которых подаются сигналы прямого кода а , dn ..., dr S, ас вь1хода снимаются сигналы обратного пятифазного кода q,, «2 , ... cfj . Преобразование кода осуществляется только прж наличии управля.юшего сигнала Zee 1. Если 2с( О,

то о « ; с«2 ... , с «5.

Формирователь 16 сигнала переноса опвсьшается алгоритмом

.Р а Ъ К гт m

или для пятифазного кода

fV Узел 15 слрже1вгя переноса осуществляет сложение сигнала переноса ess пре- дыдущего разряда И: выходных сигналов. сумматора. Он Представляет собой, матри- цу двухвходовых лоп ёских элементов 55 И размерами 2хт . Выходы элементов И каждого столбца матрицы объединяются двухвходовыми элементами ИЛИ. В обПри нечетном числе фаз одна из фаз кода при преобразовании не изменяется {в случае П5ггифазного кода - V семи- фазного - ( и т.д.).,

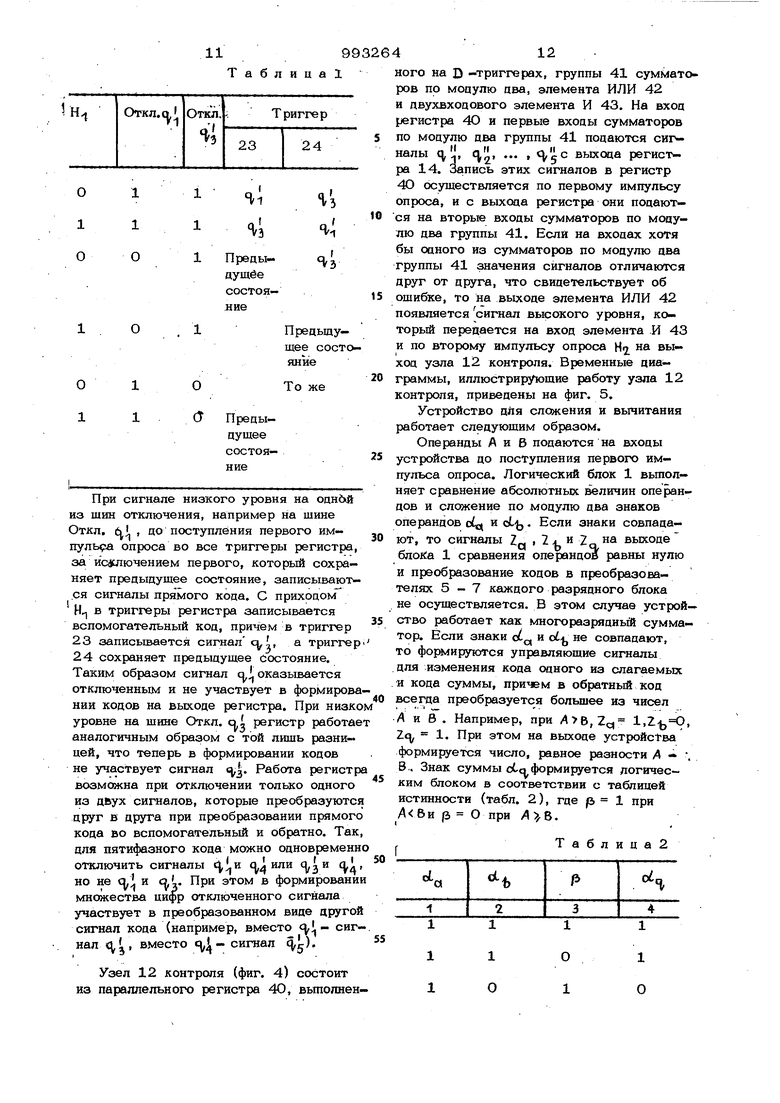

Преобразование во вспомогательнзый код осуществляется в регистре 14 „.

(фиг. 3). Регистр состоит из Rs геров 23 и 24 и узлов 29 и 30 управления триггерами. При наличии вьюокого уровня на шинах отключения Ы сигналов, обозначенных Откл. cj и Откп. q,a. и

при отсутствии первого импульса опроса : Н -1 в триггер 23 через элементы И-НЕ 31 и 32 записывается сигнал V триггер 24 через элементы 35 и

36- сигнал ц, , что соответствует

прямому пятифазному коду. При поступлений Н,, управление триггерами осутцествляется через элементы И-НЕ 33, 34,

37и 38. При этом в триггер 23 записывается сигнал а в триггер 24 сигнал . и, таким образам, на выхоое регистра образуется вспомогательный код (табл. 1). .Преобразование сигналов 1 и их запись в регистр производится аналогичньш образом. в случае пятнфазного кода проходит через регистр без преобразования. Таблица Прецьщущее состо. яние Препы- аущее состояниеПри сигнале низкого уровня на однбй из шин отключения, например на шине Откл. , до поступления первого импульра опроса во все триггеры регистра, за исключением первого, который сохраняет предыдущее состояние, записываются сигналы прямого кода. С приходом Н в триггеры регистра записывается вспомогательный код, причем в триггер 23записывается сигнал а триггер. 24сохраняет предыдущее состояние. Таким образом сигнал о оказывается , отключенным и не участвует в формирова- Г-, НИИ кодов на выходе регистра. При низком уровне на шине Откл. cj,l регистр работает аналогичным образом с той лшиь разницей, что теперь в формировании кодов не участвует сигнал . Работа регистра возможна при отключении только одного из двух сигналов, которые преобразуются друг в друга при преобразовании прямого кода во вспомогательный и обратно. Так, для пятифазного кода можно одновременно отключить сигналы Ц,|,и с или , но не ai и сз, При этом в формировании множества цифр отключенного сигнала участвует в преобразованном виде другой сигнал кода (например, вместо сигнал ц,, вместо с -сигнал ). Узел 12 контроля (фиг. 4) состоит из параллельного регистра 40, вьшолненкого на D -триггерах, группы 41 сумматоров по модулю два, элемента ИЛИ 42 и двухвхоцового элемента И 43. На вход регистра 4О и первые входы сумматоров по модулю два группы 41 подаются сигналы ц,J, , ... , «VjC выхода регистра 14. Запись этих сигналов в регистр 4О осуществляется по первому импульсу опроса, и с выхода регистра они подаются на вторые входы сумматоров по модулю два группы 41. Если на входах хотя бы одного из сумматоров по модулю два группы 41 значения сигналов отличаются друг от друга, что свидетельствует об ошибке, то на выходе элемента ИЛИ 42 появляется сигнал высокого уровня, которьй передается на вход элемента И 43 и по второму импульсу опроса Н на выход узла 12 контроля. Временнью диаграммы, иллюстрирующие работу узла 12 контроля, приведены на фиг. 5. Устройство для сложения и вычитания работает следующим образом. Операнды А и В подаются на входы устройства до поступления первого импульса опроса. Логический блок 1 вьшодняет сравнение абсолютных величин операндов и сложение по модулю два знаков операндов da и ci-b Если знаки совпадают, то сигналы ZQ 2 и Zo на выходе блока 1 сравнения операндов равны нулю и преобразование кодов в преобразователях 5-7 каждого разрядного блока не осуществляется. В этом случае устрой- ство работает как многоразрядньй сумма ° а « совпадают, то формируются управляющие сигналы для изменения кода одного из слагаемых и кода суммы, причем в обратный код F г-i всегда преобразуется большее из чисел : - - Например, при ,2с( 1,, 2:с 1. При этом на выходе устройства формируется число, равное разности А В.. Знак суммы оСо формируется логическим блоком в соответствии с таблицей истинности (табл. 2), где /а 1 при |3 О при . Таблида2 Продолжение табл. : В регистр 14 каждого разряда запи- сывается прямой код сигнала с выхода сумматора, затем осуществляется сложение этого сигнала с сигналом переноса из предыдущего разряда в узле 15, выходные сигналы , , ... ,q, которого преобразуются в обратный код (если ZQ 1) и поступают на выходные шины разрядного блока. Формирование сигнала переноса в последующий разряд производится по форму ле (6), если Z0 Z. О. В том случае когда одно из слагаемых преобразуется в обратный код, то пятая фаза этого сла гаемого, участвующая в формировании сигнала р, инвертируется сумматорами 10 или 11 по модулю два. С приходом первого импульса опроса сигналы изменения кода в преобразователях 5 и в Z и Zjj изменяются при помо щи сумматоров 8 и 9 по модулю два на противоположные. Это необходимо для того, чтобы осуществить переключения в сумматоре. Теперь сигнал формируется элементами матрицы сумматора, . предназначенными для формирования cj, и наоборот сигнал cj, формируется элеме тами матрицы для { 1. Таким же образом переключаются элементы матрицы для и . В регистр 14 при наличии . записьшается вспомогательный код, который также заносится и в регистр блока контроля. Вспомогательный код, который, в сущности, представляет собой прямой код, полученный посредством переключения элементов матрицы сумматора, складывается с сигналом переноса из -предыдущего разрвда в узле 15 и не рез третий преобразователь 7 поступает на соответствующий выход результата устройства. После окончаниями (фиг. 5, момент t,) в каждом разряде устройства происходят обратные переключения и формиро94 ванне CJli осуществляется таким же обра- зом, как до прихода Н, . При этом в узле 12 контроля поразрядно сравниваются иваю сигналы кода С{, , 2 Vs г 3 санные во время Ни , и сигналы этого по окончании . В кода, полученные том случае, когда .сумматор функционирует нормально, эти сигналы совпадают и на выходе элемента ИЛИ 42 сигнал от сутствует. . Если, в одном из разрядов сумматора произошел кратковременный сбой или имеется неисправный элемент, то сигналы в узле 12 контроля, записаннью во время и сигналы, полученные по окончании Н;., полностью не совпадают и на выходе элемента ИЛИ 42 появляется сигнал схиибки, который по второму импульсу опроса Н2 передается на выход блока контроля. В этом случае число на выходе разряда не соответствует сумме входных чисел А и В . Для обнаружения неисправного элемента сумматора необходимо произвести поочередное отключение элементов сумматора, подавая сигнал низкого уровня поочередно на щины отключения Откл. , Откл. 1аИ т.д. Отключение выполняется вручную с помощью переключателей, но в принципе может быть автоматизировано. Если при подаче низкого уровня на одну из щин, например Откл. 4 сяиибки М исчезнет, это означает, что неисправный элемент находится в той части матрицы сумматора, которая формирует сигнал, записанный в обозначении данной щины отключения ( ). После окончания первого импульса опроса вьйсодное число данного разряда будет соответствовать результату сложения операндов. В том случае, когда сигнал ошибки не исчезает при отключении поочередно всех щин отключения, необходимо производить попарное отключение шин. Устройство с отключенными элементами сумматора сохраняет свою работоспособность, что показывает его высокую надежность. Таким образом, предлагаемое устройсгтво для сложения и вычитания при сох ранения быстродействия прсутотипа дает возможность.контролировать операцию сложения двух операндов и отключать до половины исправных элементов матрицы сумматора в каждом блоке сложения, повьпиает достоверность вычислений уст. jpoficTBa. 15 и 3 о б Формула р в т е н и я 5 1. Многоразрядное устройство для сложения и вьиитания, содеркащее блок сравнения операндов и К блоков сложения, каждый из которых содержит сумматор, три преобразователя прямого кода в обратный, формирователь сигнала переноса, узел сложения переноса, прячем входы блока сравнения операндов являются входами первого ивторого операндов устрой- ства, входы первых преобразователей прямого кода в обратный всех блоков сложения соединены с входами соответствующих разрядов первого операнда устройства, входы вторых преобразователей прямого кода в обратный всех блоков сложения соединены с входами соответствующих разрядов второго операнда устройства, выходы третьих преобразователей прямого кода в обратный .всех блоков сложения являются выходами результата устройства, в каждом блоке сложения первая и вторая группы входов сумматора соединены с группами выходов первого и второго преобразователей прямого кода в обратный соответственно, группа входов третьего преобразователя прямого кода в обратньй соединена с группой выходов узла сложе- ния переноса, старший разряд группы выходов узла сложения переноса соединен с первым входом формирователя сигнала переноса, первый выход блока сравнения операндов соединен с входами третьих преобразователей прямого кода в обратны всех блоков сложения, второй выход блока .сравнения операндов является выходом знака результата устройства, выход форьмирователя сигнала переноса -го блока сложения (14 i К-1 ) соединен с входом узла сложения переноса {i + 1)го блока сложения, отл. и чающее с я тем, что, с яелью повьщдения достоверности вычислений, в каждый блок сложения введены регистр, узел контроля и четыре сумматора по модулю два, причем в к.аждом блоке сложения выходы первого и второго сумматоров по модулю два соединены с входами первого и второго преобразователей прямого кода в обратный соответственно, выходы третьего и четЕиертого сумматоров по модулю два соединены соответственно с вторым и третьим входами- формирователя сигнала переноса, группа выходов сумматора соеЙ534 динена с первой группой вхоцов регистра, группа выходов которого соединена с группами входов узла контроля и узла сложения переноса, третий выход блока сравнения операндов соединен с первыми входами первого и третьего сумматоров по модулю два всех блоков сложения, четвертый выход блока сравнения операндов соединен с первыми входами второго и четвертого сумматоров по модулю два всех блоков сложения, в каждом блоке сложения вторые входы третьего и четвертого сумматоров по модулю два соединены с входами старших разрядов группы |Входов первого и второго преобразователей прямого кода в обратный соответственно, первьй вход устройства соединен с вторыми входами первого и второго сумматоров по модулю два, входами регистров и первыми входами узлов контроля всех блоков сложения, второй вход устройства соединен с вторыми входами узлов контроля всех блоков сложения, вторые группы входов регистров всех блоков сложения являются управляющими входами устройства, выходы узлов контроля всех блоков сложения являются выходами неисправности устройства. 2. Устройство по п, 1, о т л и ч а ю щ е е с я тем, что узел контроля содер жит регистр, группу сумматоров по модулю два, элемент ИЛИ, элемент И, причем первые входы сумматоров по модулю два группы соединены с входами данных соответствующих разрядов регистра и образуют группу входов узла контроля, выходы регистра соединены с вторыми входами соответствующих сумматоров по модулю два группы, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого является выходом узла контроля, управляющий вход ргистра и второй вход элемента И являются соответственно первым и вторым входами узла контроля. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 739530, кл. G, 06 F 7/385, 1978. 2.Авторское свидетельство СССР по заявке № 2981297/18-24, кл. G 06 F 7/50, 1980 (прототип).

«

у/

.4

Н,

2

/

«J

М,

.f

сриг.5

Авторы

Даты

1983-01-30—Публикация

1981-07-23—Подача