Предложенный универсальный логический эле.мент относится к области авто.матики и вычислительной техники. На его основе могут быть .построены вычислительные, среды и запоминающие устройства.

Известны универсальные логические элементы, содержащ.ие логические схемы и запоминающие элементы. Однако в известных схемах невозможно проводить настройку части вычислительной среды без разрушения настроечной информации в другой ее части.

П-редложен-ный универсальный логический элемент, содержащий два многоэмитгерных транзистора и выходной транзистор р-п-/ проводимости, многоэмиттерный транзистор л-р-«.-проводимости и запоминающий элемент, выполненный на диоде с S-образной характеристикой, отличается тем, что коллекторы двух многоэмиттерных транзисторов .противоположного типа .проводимости объединены и соединены с запоминающим элементом и одним из эммиттеров третьего многоэмиттерного транзитора, другие эммитеры которого подключены к логическим входам элемента, а эмиттеры первых двух м.ногоэмиттерных транзисторов подсоединены ко входам установки в «нуль и «единицу, база многоэмиттерного транзистора п-р-«-проводимости через резистор подключена к шине отдельного источника питания.

Это позволяет расширить логические возможности элемента.

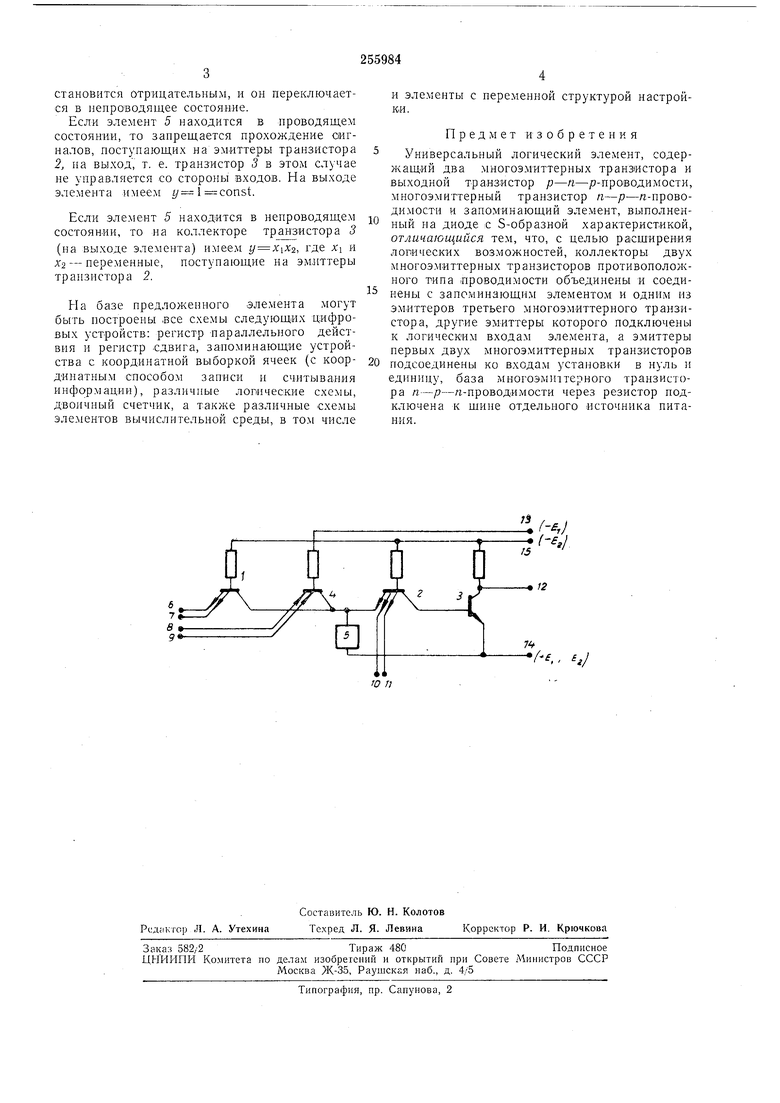

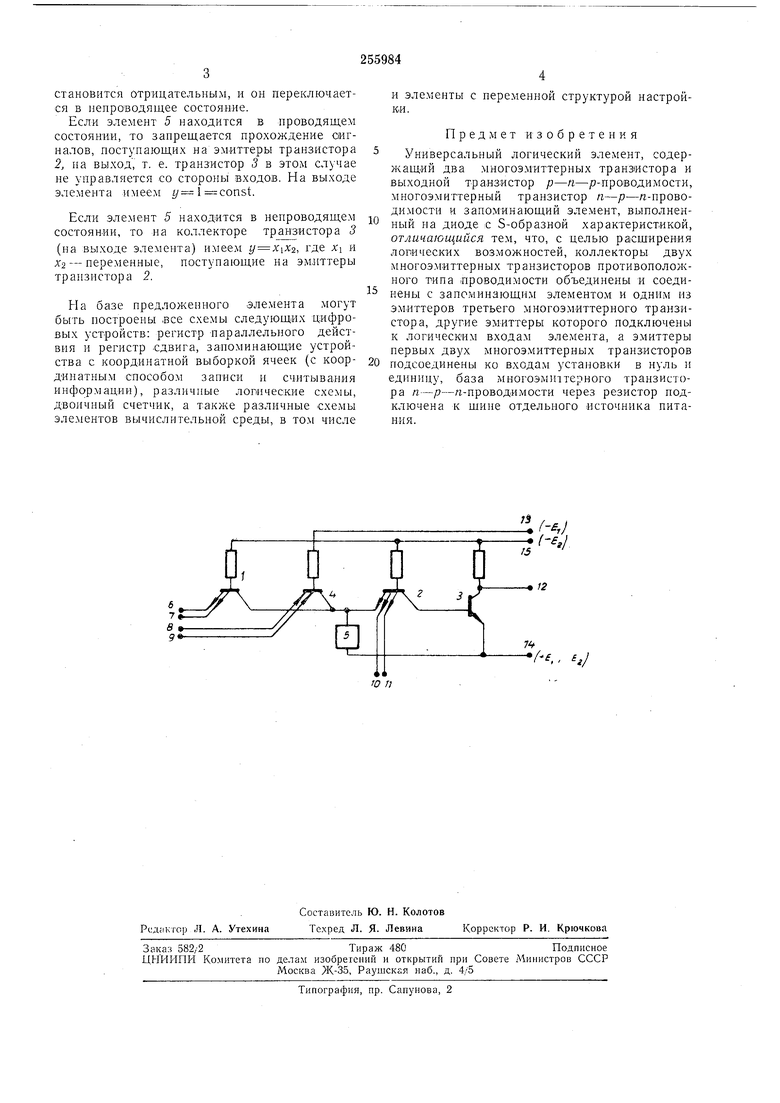

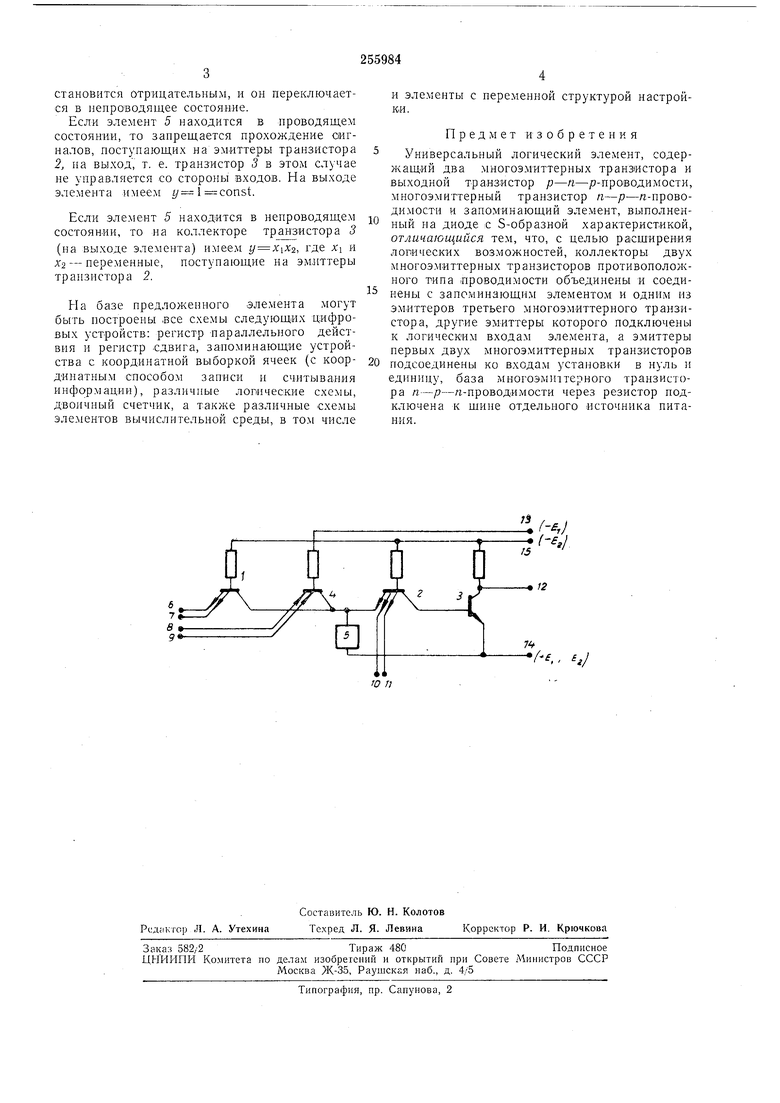

Схема предложенного элемента приведена на чертеже.

Он состоит из многоэмиттерных транзисторов / и 2, выходного транзистора 5, транза}стора 4 п-р-я-проводимости и запоминающего элемента 5.

По входам 6 и 7 подаются сигналы, под

действием которых запоминающий элемент 5 переключается в «О, т. е. из состояния низкой проводимости в состояние высокой проводимости, по входам 5 и Р - сигналы, под действием которых запоминающ.ий элемент .переключается в «1, т. е. из состояния высо.чОЙ проводимости в состояние низкой проводимости, по входам 10 и П - сигналы логических переменных. Выход элемента - 12. Питание элемента осуществляется по входам .

В качестве запоминающего элемента 5 может быть использован прибор со структурой р-п-р-л либо двухполюсный прибор со структурой .металл-диэлектрик-металл, принцип работы которого основан .на электродиффузии ионов одного из металлов в диэлектрик. При нодаче сигналов на оба эмиттера транзистора / потенциал на элементе 5 увеличивается, и он переключается в проводящее состояние, а при подаче сигналов на оба эмиттестановится отрицательным, и он переключается в непроводящее состояние. Если элемент 5 находится в проводящем состоянии, то занрещается прохождение сигналов, поступающих на эмиттеры транзистора 2, на выход, т. е. транзистор 3 в этом случае не управляется со стороны входов. На выходе элемент имеем i/ l const. Если элемент 5 находится в непроводящем состоянии, то на коллекторе транзистора 3 (на выходе элемента) имеем ,, где Xi н А2 - переменные, поступающие на эмлттеры транзистора 2. На базе предложенного элемента .могут быть построены все схемы следующих цифровых устройств: регистр параллельного действия н регистр -сдвига, заноминающие устройства с координатной выборкой ячеек (с координатным способом записи и считывания информации), различные логические схемы, двоичный счетчик, а также различные схемы элементов вычислительной среды, в то. числе Н элементы с переменной структурой настройки. Предмет изобретения Универсальный логический элемент, содержащий два .многоэмиттерных транзистора и выходной транзистор р-П-уС7-Ир01ВОДИМОСТИ, многоэмиттерный транзистор п-р-я-проводи.мости и запоминающий элемент, выполненный на диоде с S-образной характеристикой, отличающийся тем, что, с целью расщирепия логических возможностей, коллекторы двух многоэмиттерных транзисторов противоположного типа проводимости объединены и соединены с запоминающим элементом и одни.м из эмиттеров третьего многоэмиттерного транзистора, другие эмиттеры которого подключены к логическим входам элемента, а эмиттеры первых двух многоэмиттерных транзисторов подсоединены ко входам установки в нуль и единицу, база многоэмиттерного транзистора п-р-п-проводи мости через резистор подключена к щине отдельного источника питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНЫЙ ЭЛЕМЕНТ | 1967 |

|

SU206161A1 |

| Логический переключающийэлЕМЕНТ | 1979 |

|

SU849489A1 |

| Логический элемент и-не | 1978 |

|

SU729848A1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| Ассоциативный запоминающий элемент | 1983 |

|

SU1130900A1 |

| Ячейка памяти | 1973 |

|

SU444245A1 |

| Транзисторно-транзисторный элемент и-не/и | 1973 |

|

SU450365A1 |

| Д-ТРИГГЕР | 1973 |

|

SU389628A1 |

| Генератор импульсов | 1978 |

|

SU790109A1 |

| Триггерный логический элемент И-НЕ | 2018 |

|

RU2694151C1 |

/Л

; (,

-/г

Даты

1969-01-01—Публикация