1

Изобретение относится к цифровой техиике.

Известны транзисторно-транзисторные элементы «И -«НЕ/И, содержащие логический элемент «И на мяогоэмиттерном транзисторе, дна ВЫХОДНЫХ инвертора, дифференциальный усилитель на п-р-п транзисторах, делитель напряжения на двух резисторах я дна р-п-р транзистора. Такие элементы имеют низкую помехоустойчивость и значительную задержку между выходными ларафазными сигналами.

В целях устранения указанных недостатков В предлагаемом транзисторно-транзисторном элементе коллектор многоэмйттерного транзистора логического элемента «И подключен к одному входу дифференциального усилителя, Д|ругой ВХОД которого подсоединен к вредней точке делителя напряжения, коллекторы транзисторов дифференциального усилителя подключены к базам включенных по Схеме с общим эмиттером р-п-р транзисторов. Коллекторы последних соединены с выходными инверторами.

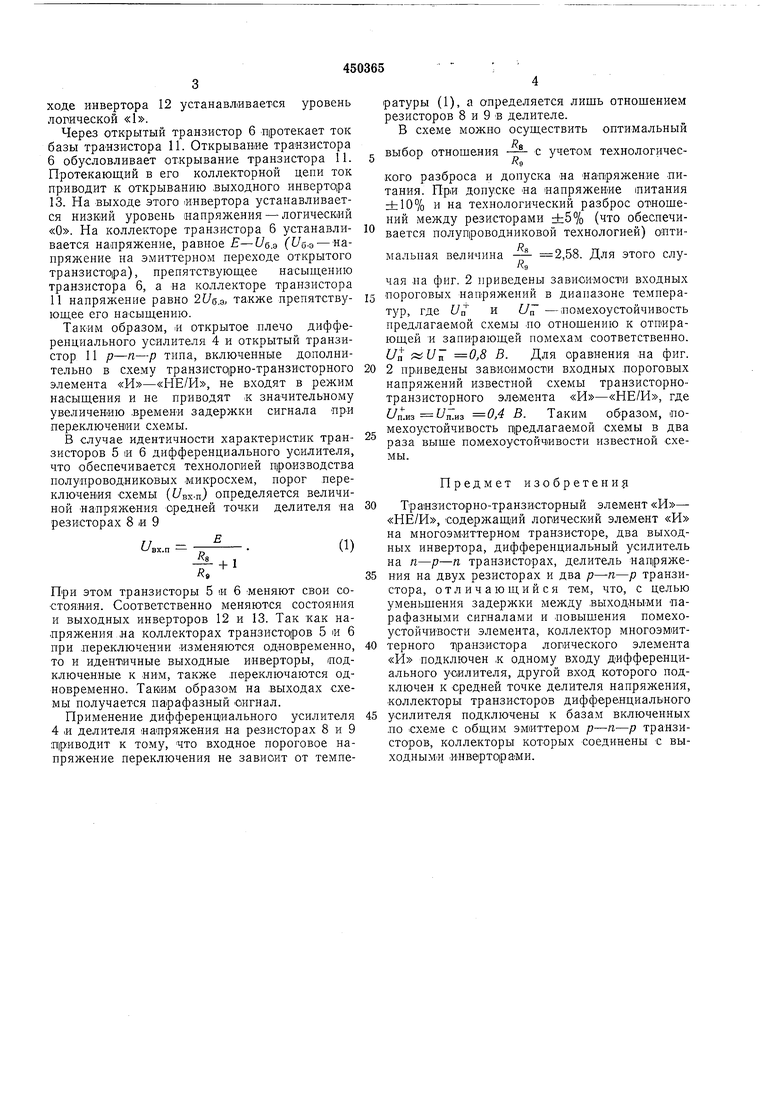

На фиг. 1 изображена принципиальная схема предлагаемого транзисторно-транз«Сторного элемента «И -«НЕ/И ; на фиг. 2 показана зависимость входного порогового напряжеН.ИЯ В диапазоне температур.

Ирияцилиальная схема «И -«НЕ/И содержит логический элемент «И 1 на многоэмиттерном транзисторе 2 и резисторе 3; дифференциальный усилитель 4 на двух транзисторах 5 и 6 п-р-п типа-и резисторе 7. Один ВХОД дифференциального усилителя, являющийся базой транзистора 5, подключен к коллектору многоэмиттерного транзистора. База транзистора 6, являющаяся вторым входо м дифференциального усилителя, подключена к средней точке делителя напряжения на реэисторах 8 и 9. К коллекторам транзисторов 5 |И 6 подключены соответственно базы транзисторов 10 и 11 типа, В коллекторные цепи которых включены выходные инверторы 12 и 13.

Схема работает следующим образом.

Если па один из входов схемы (один из эмиттеров транзистора 2) подан низкий уровень напряжения (логический «О), то многоэмиттерный 11ранз стор 2 находится в насыщении

|И потенциал его коллектора выше потенциала эмиттера на величину напряжения насыщения транзистора. В этом режиме транзистор 5 закрыт, а транзистор 6 открыт за счет смещения на базе, заданного делителем напряжения,

выполненным на резисторах 8 и 9. При этом на коллекторе транзистора 5 устанавливается ВЫСОКИЙ уровень напрял епия, равный Е (Е - напряжение источника питания), и обеспечивает режим закрытого состояния транзистора 10 и ВЫХОДНОГО инвертора 12. На выходе инвертора 12 устанавливается уровень логической «1.

Через открытый транзистор 6 протекает ток базы тра«зИСтора 11. Открывание транзистора 6 обусловливает открывание транзистора И. Протекающий в его коллекторной цепи ток приводит к открыванию выходного инвертора 13. На выходе этого -инвертора устанавливается низкий уровень напряжения - логический «О. На коллекторе транзистора 6 устанавливается напряжение, равное E-U.a (f/б.э -Напряжение на эмиттерном переходе открытого транзистора), препятствующее насыщению транзистора 6, а на коллекторе транзистора 11 напряжение равно 2(7б.э. также препятствующее его насыщению.

Таким образом, « открытое плечо дифференциального усилителя 4 и открытый транзистор 11 р-п-р типа, включенные дополнительно в схему транзисторно-транзисторного элемента «И -«НЕ/И, не входят в режим насыщения и не приводят ,к значительному увеличению .времен-и задержки сигнала при переключении схемы.

В случае идентичности характеристик транзисторов 5 и 6 дифференциального усилителя, что обеспечивается технологией производства полупроводниковых микросхем, порог переключения схемы ((/Ех-п) определяется величиной Напряжения средней точки делителя на резисторах 8 и 9

(1)

г7вх.п

А к

+ 1

при этом транзисторы 5 и 6 меняют свои состояния. Соответственно меняются состояния и выходных инверторов 12 и 13. Так как напряжения на коллекторах транзисторов 5 и б при .переключении изменяются одновременно, то и идентичные выходные инверторы, подключенные к ним, также переключаются одновременно. Таким образом на выходах схемы получается парафазный сигнал.

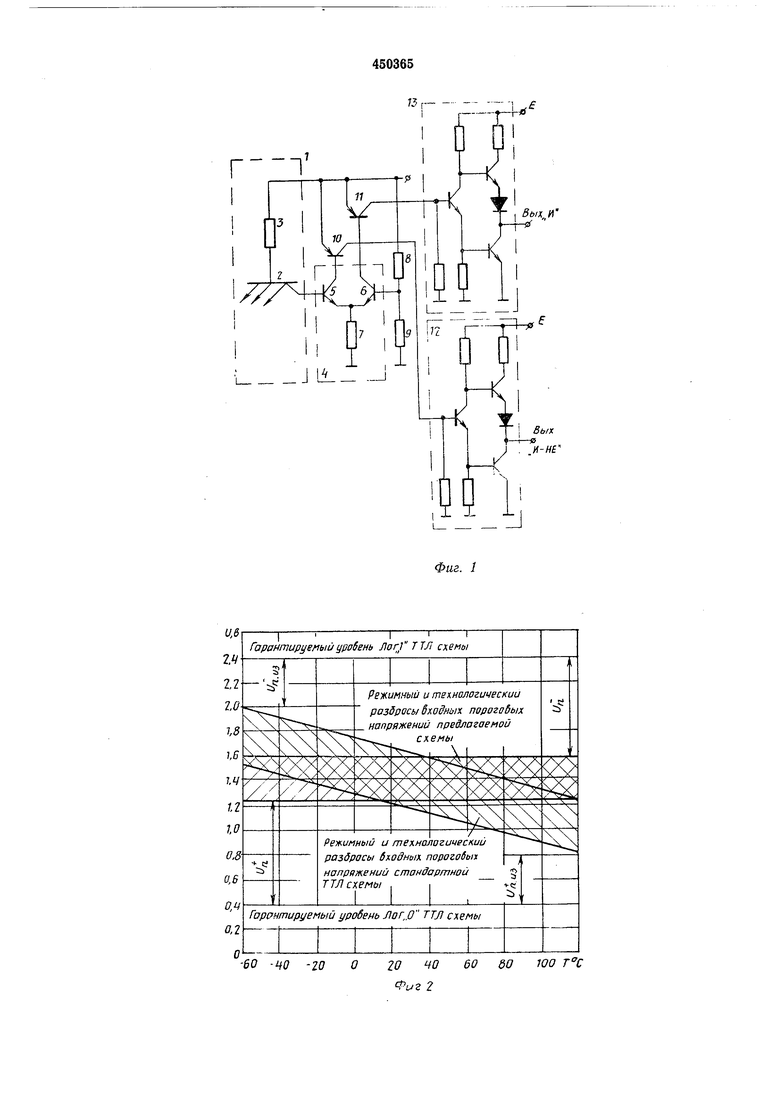

Применение дифференциального усилителя 4 и делителя напряжения на резисторах 8 и 9 приводит к тому, что входное пороговое напряжение переключения не зависит от температуры (1), а определяется лищь отнощением резисторов 8 и 9 в делителе. В схеме можно осуществить оптимальный

KS

г выбор отношения -- с учетом технологического разброса и допуска на напряжение питания. При допуске на напряжение 1питания ±10% и на технологический разброс отношений между резисторами ±5% (что обеспечивается полупроводниковой технологией) оптип

мяльная величина - 2,58. Для этого

чая на фиг. 2 приведены зависимости входных 5 пороговых напряжений в диапазоне температур, где Un и f/iT -помехоустойчивость предлагаемой схемы по отношению к отпирающей и запирающей помехам соответственно. Ua 0,8 В. Для сравнения на фиг. 0 2 приведены зависимости входных пороговых напряжений известной схемы транзисторнотранзисторного элемента «И -«НЕ/И, где

Un.K3 fJn.a3 0,4 В. Таким образом, помехоустойчивость предлагаемой схемы в два раза выше помехоустойчивости известной схемы.

Предмет изобретение

0 Траизисторно-транзисторный элемент «НЕ/И, содержащий логический элемент «И на многоэмиттерном транзисторе, два выходных инвертора, дифференциальный усилитель на п-р-п транзисторах, делитель напряже5 ПИЯ на двух резисторах и два р-п-р транзистора, отличающийся тем, что, с целью уменьшения задержки между выходными парафазными сигналами и повышения помехоустойчивости элемента, коллектор многоэмиттерного TipaH3«CTOpa логического элемента «И подключен к одному входу дифференциального усилителя, другой вход которого подключен к средней точке делителя напряжения, коллекторы транзисторов дифференциального

5 усилителя подключены к базам включенных по схеме с общим эмиттером р-я-р транзисторов, коллекторы которых соединены с выходными инверторами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент и-не | 1973 |

|

SU531283A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Транзисторный инвертор | 1991 |

|

SU1815775A1 |

| Преобразователь постоянного напряжения | 1979 |

|

SU773609A1 |

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| Стабилизированный конвертор | 1979 |

|

SU892425A1 |

Авторы

Даты

1974-11-15—Публикация

1973-06-18—Подача