Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известен логический элемент ИЛИ/ИЛИ - НЕ [Манаев Е.И. Основы радиоэлектроники. − М.: Радио и связь, 1985, стр. 342, рис. 14.23], содержащий шесть транзисторов и пять резисторов.

Недостаток его заключается в том, что у него малая нагрузочная способность. Электрический ток только одного из шести имеющихся транзисторов формирует электрический ток внешней нагрузки на каждом из двух выходов. Если бы удалось увеличить число транзисторов, формирующих ток нагрузки из общего числа имеющихся транзисторов, то это привело бы к увеличению максимальной силы электрического тока внешней нагрузки логического элемента и в результате к повышению нагрузочной способности.

Известен триггер с дополнительной симметрией [Гольденберг Л.М., Импульсные и цифровые устройства. − М.: Связь, 1973, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и источники постоянных питающих напряжений.

Недостатком его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или к эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба имеющихся транзисторов, то это повысило бы нагрузочную способность триггера.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа логический элемент И-НЕ [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 593, рис. 8.5, а], содержащий четыре транзистора, четыре резистора и диод.

Недостаток его заключается в малой нагрузочной способности. Электрический ток только одного из четырёх транзисторов формирует ток внешней нагрузки. Если бы удалось в общем количестве имеющихся транзисторов увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это привело бы к увеличению максимальной силы электрического тока нагрузки логического элемента и в результате к повышению нагрузочной способности.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента И-НЕ.

Это достигается тем, что в триггерный логический элемент И-НЕ, содержащий источник питающего постоянного напряжения, общая шина (минусовая) которого заземлена, первый резистор, включенный между выходом (плюсовая шина) питающего источника и базой первого многоэмиттерного, в частности, двухэмиттерного транзистора (n-p-n), эмиттеры которого образуют входы логического элемента относительно «земли», последовательно соединённые второй резистор, второй транзистор (n-p-n) и третий резистор, свободный вывод второго резистора соединён с выходом питающего источника, база второго транзистора соединена с коллектором первого транзистора, а свободный вывод третьего резистора заземлен, общий вывод эмиттера второго транзистора и третьего резистора подключен к базе третьего транзистора (n-p-n), коллектор которого соединён с выводом выхода логического элемента относительно «земли», а эмиттер заземлён, также имеются последовательно соединённые четвёртый резистор и четвёртый транзистор (n-p-n), свободный вывод четвёртого резистора соединён с выходом питающего источника, введены дополнительный транзистор (p-n-p) противоположного типа проводимости и три дополнительных резистора, дополнительный транзистор и первый дополнительный резистор между собой включены последовательно, эмиттер дополнительного транзистора соединён с общим выводом второго резистора и коллектора второго транзистора, база дополнительного транзистора подключена к общему выводу четвертого резистора и коллектора четвёртого транзистора, общий вывод коллектора дополнительного транзистора и первого дополнительного резистора соединён с базой четвёртого транзистора, свободный вывод первого дополнительного резистора подключен к выходу логического элемента, второй дополнительный резистор включен между эмиттером четвертого транзистора и выходом логического элемента, а третий дополнительный резистор - между «землей» и общим выводом четвертого резистора, коллектора четвёртого транзистора и базы дополнительного транзистора.

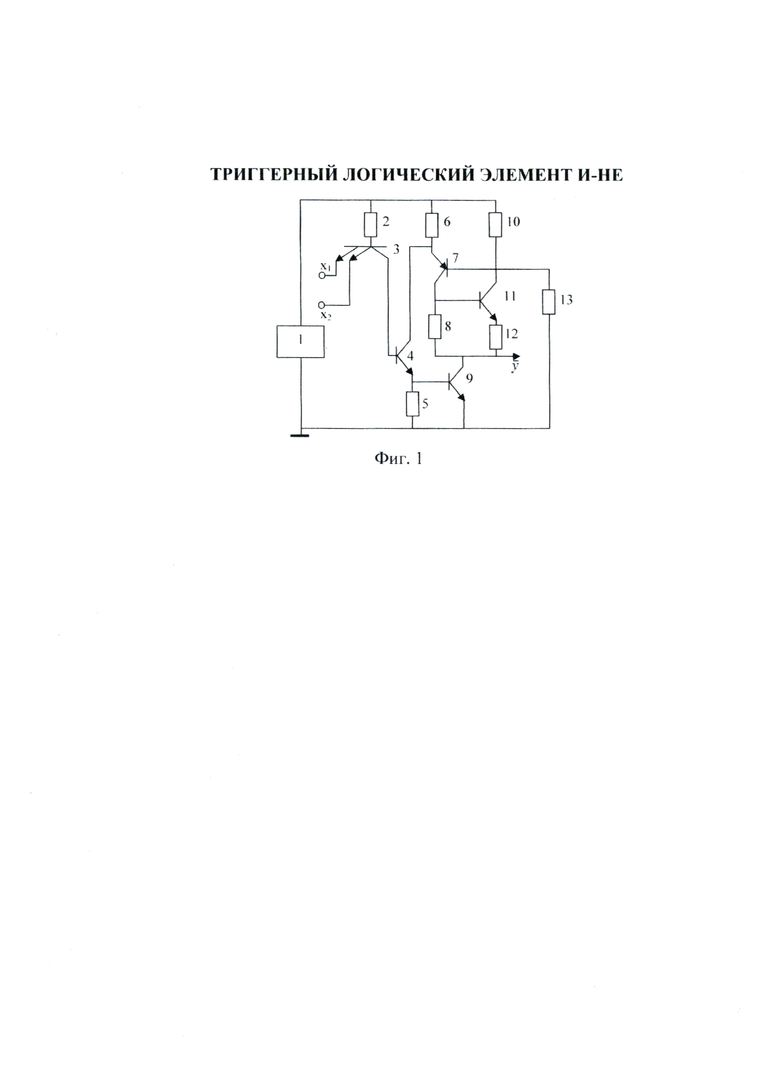

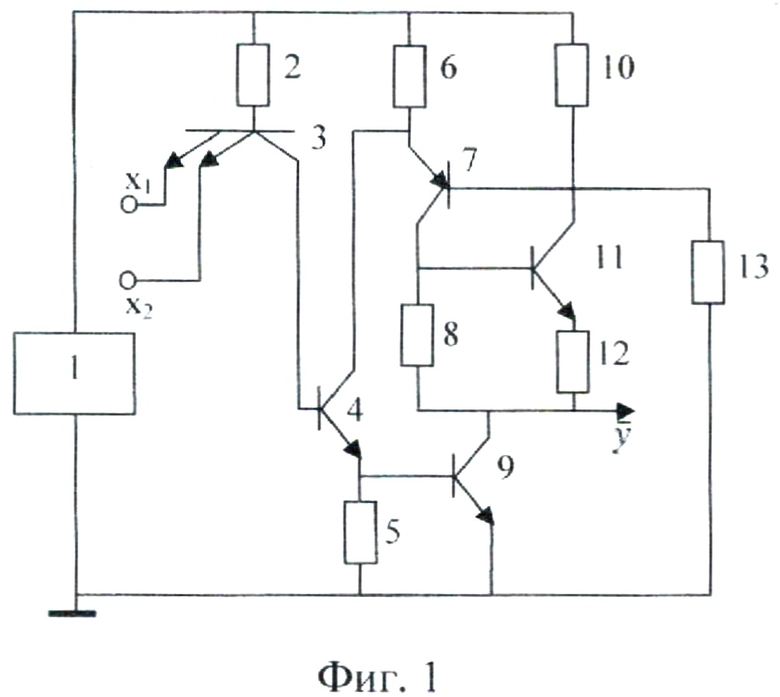

Сущность изобретения поясняется чертежом (фиг. 1).

В триггерном логическом элементе И-НЕ общая шина (вывод отрицательного напряжения) источника 1 питающего постоянного напряжения заземлена, а выход соединён с одним из выводов резистора 2. Другой вывод этого резистора подключен к базе многоэлементного (в частности, двухэмиттерного) n-p-n транзистора 3. Выводы эмиттеров этого транзистора образует входы триггерного логического элемента И-НЕ относительно «земли», а коллектор соединён с базой n-p-n транзистора 4. Между эмиттером его и «землей» включен резистор 5. Последовательно между собой включены резистор 6, p-n-p транзистор 7, резистор 8 и n-p-n транзистор 9. Свободный вывод резистора 6 соединён с общим выводом источника 1 питающего постоянного напряжения и резистора 2. Другой вывод резистора 6 подключен к эмиттеру транзистора 7 и с их общим выводом соединён коллектор транзистора 4. Свободный вывод эмиттера транзистора 9 заземлён, а его база соединена с общим выводом эмиттера транзистора 4 и резистора 5. Между собой последовательно включены резистор 10, n-p-n транзистор 11 и резистор 12. Свободный вывод резистора 10 соединён с общим выводом выхода источника 1, резисторов 2 и 6, а другой вывод этого резистора соединён с коллектором транзистора 11. Свободный вывод резистора 12 подключен к общему выводу резистора 8 и коллектора транзистора 9, также общий вывод последних трёх элементов 8, 9 и 12 образует выход логического элемента относительно «земли». База транзистора 7 соединена с общим выводом резистора 10 и коллектора транзистора 11, а база транзистора 11 - с общим выводом резистора 8 и коллектора транзистора 7. Резистор 13 включен между «землей» и общим выводом резистора 10, базы транзистора 7 и коллектора транзистора 11.

Триггерный логический элемент И - НЕ работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля (близкому к нулю), высокий уровень - уровень логической единицы соответствует значениям напряжения в единицы вольт (нередко четыре вольта). Работа логического элемента отражается таблицей 1. Первые три строчки таблицы соответствуют

тому, что на одном или на двух входах  имеется уровень логического 0 (низкий уровень напряжения). Напряжение источника питания 1 положительной полярности через резистор 2 приложено к базе n-p-n транзистора 3. Поэтому базо-эмиттерный p-n переход или два таких перехода (по сути диоды) открыты (проводят электрический ток) и, как известно, на них выделяется весьма малое значение напряжения. По значению напряжение на базе транзистора 3 относительно «земли» находится в районе нуля (уровень логического нуля). Базо-коллекторный переход (по сути тоже диод) тоже открыт, на базе транзистора 4 низкий уровень напряжения (уровень логического нуля) в районе порогового напряжения, и сила электрического тока через этот транзистор равна нулю или настолько мала, что не влияет на состояние триггера на транзисторах 7, 11 противоположного типа проводимости.

имеется уровень логического 0 (низкий уровень напряжения). Напряжение источника питания 1 положительной полярности через резистор 2 приложено к базе n-p-n транзистора 3. Поэтому базо-эмиттерный p-n переход или два таких перехода (по сути диоды) открыты (проводят электрический ток) и, как известно, на них выделяется весьма малое значение напряжения. По значению напряжение на базе транзистора 3 относительно «земли» находится в районе нуля (уровень логического нуля). Базо-коллекторный переход (по сути тоже диод) тоже открыт, на базе транзистора 4 низкий уровень напряжения (уровень логического нуля) в районе порогового напряжения, и сила электрического тока через этот транзистор равна нулю или настолько мала, что не влияет на состояние триггера на транзисторах 7, 11 противоположного типа проводимости.

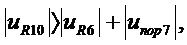

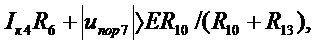

Электрический ток, протекающий через резисторы 10 и 13, создаёт на резисторе 10 напряжение, которое минусом приложено к базе p-n-p транзистора 7. В худшем случае, если

где

где

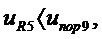

для первых трёх строчек табл. 1. Нулевое значение силы электрического тока транзистора 4 или почти нулевое его значение создаёт на резисторе 5 весьма малое значение напряжения и

для первых трёх строчек табл. 1. Нулевое значение силы электрического тока транзистора 4 или почти нулевое его значение создаёт на резисторе 5 весьма малое значение напряжения и

где

Четвёртая строчка табл. 1 соответствует тому, что на обоих входах (х1 и х2) имеется высокий уровень напряжения (уровень логической 1). Большее по значению напряжение источника питания 1 поддерживает p-n переходы двух базо-эмиттерных и базо-коллекторного переходов транзистора 3 в открытом состоянии и на базе n-p-n транзистора 4 имеется высокий уровень напряжения, который поддерживает этот транзистор в открытом состоянии и существенное значение силы электрического тока коллектора транзистора 4. Электрический ток последнего транзистора создаёт на резисторе 6 напряжение, минусом приложенное к эмиттеру транзистора 7 и достаточное для его закрывания.

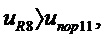

Тогда электрический ток через резистор 8 не протекает, напряжение на нём равно нулю, оно меньше порогового напряжения транзистора 11, и он закрыт. Через резистор 10 протекает электрический ток, замыкающийся только на резистор 13. Напряжение на резисторе 10 минусом приложено к базе транзистора 7. Тогда для получения закрытого состояния транзистора 7 следует выполнить неравенство

где

соответствуют логической 1, электрические токи транзисторов 7 и 11 равны нулю, напряжение на эквивалентной нагрузке и на выходе логического элемента соответствует уровню логического 0.

соответствуют логической 1, электрические токи транзисторов 7 и 11 равны нулю, напряжение на эквивалентной нагрузке и на выходе логического элемента соответствует уровню логического 0.

Электрический ток транзистора 4 (его эмиттерный ток) создаёт на резисторе 5 напряжение достаточное для открывания транзистора 9 и через этот открытый транзистор паразитные ёмкости (выходная емкость логического элемента и входная ёмкость подключаемой нагрузки) сравнительно быстро разряжаются всякий раз при поступлении на входы высокого уровня напряжения (четвёртая строчка табл. 1). Это ослабляет понижение быстродействия логического элемента за счёт увеличения времени разряда паразитных емкостей при отсутствии транзистора 9. Точно также, как и в прототипе, транзистор 9 выполняет роль управляемого ключа. Этот ключ разомкнут при первых трёх строчках табл. 1 и замкнут при четвёртой строчке.

При четвёртой строчке в табл. 1 транзисторы 7 и 11 (рис.1) закрыты с запасом и это обеспечивает весьма малое значение низкого уровня напряжения на выходе логического элемента (уровень логического нуля). В прототипе транзистор, обеспечивающий ток нагрузки, близок в этом случае к открыванию или даже на грани открывания. Чтобы его привести к закрыванию вводят дополнительный диод. Если бы диод отсутствовал, то обсуждаемый транзистор был бы открыт, в лучшем случае на грани открывания. Такое положение приводит к увеличению низкого уровня напряжения (уровень логического нуля), и он больше, чем в триггерном логическом элементе.

Таким образом, в триггерном логическом элементе И-НЕ сила электрического тока внешней нагрузки равна сумме силы токов двух транзисторов 7 и 11, т.е. двух из имеющихся пяти транзисторов, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из имеющихся четырёх транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент И/И-НЕ | 2020 |

|

RU2727613C1 |

| Триггерный сумматор по модулю два | 2018 |

|

RU2700195C1 |

| Триггерный логический элемент ИЛИ-НЕ | 2021 |

|

RU2767176C1 |

| Триггерный логический элемент И/ИЛИ | 2020 |

|

RU2745398C1 |

| Триггерный синхронный R-S триггер | 2018 |

|

RU2692041C1 |

| Триггерный синхронный R-S триггер | 2018 |

|

RU2731438C2 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2783403C1 |

| Триггерный синхронный D триггер | 2018 |

|

RU2692422C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2020 |

|

RU2726853C1 |

Изобретение относится к схемотехнике. Технический результат: повышение нагрузочной способности триггерного логического элемента И-НЕ. Для этого предложен триггерный логический элемент И-НЕ, содержащий пять транзисторов, семь резисторов и источник питающего напряжения. При этом в него введены дополнительный транзистор (p-n-p) и три дополнительных резистора, дополнительный транзистор и первый дополнительный резистор включены последовательно, эмиттер дополнительного транзистора соединен с общим выводом второго резистора и коллектора второго транзистора, база дополнительного транзистора подключена к общему выводу четвертого резистора и коллектора четвертого транзистора, общий вывод коллектора дополнительного транзистора и первого дополнительного резистора соединен с базой четвертого транзистора, свободный вывод первого дополнительного резистора подключен к выходу устройства, второй дополнительный резистор включен между эмиттером четвертого транзистора и выходом устройства, а третий дополнительный резистор - между «землей» и общим выводом четвертого резистора, коллектора четвертого транзистора и базы дополнительного транзистора. 1 ил., 1 табл.

Триггерный логический элемент И-НЕ, содержащий источник питающего постоянного напряжения, общая шина (минусовая) которого заземлена, первый резистор, включенный между выходом (плюсовая шина) питающего источника и базой первого многоэмиттерного, в частности двухэмиттерного, транзистора (n-p-n), эмиттеры которого образуют входы логического элемента относительно «земли», последовательно соединенные второй резистор, второй транзистор (n-p-n) и третий резистор, свободный вывод второго резистора соединен с выходом питающего источника, база второго транзистора соединена с коллектором первого транзистора, а свободный вывод третьего резистора заземлен, общий вывод эмиттера второго транзистора и третьего резистора подключен к базе третьего транзистора (n-p-n), коллектор которого соединен с выводом выхода логического элемента относительно «земли», а эмиттер заземлен, также имеются последовательно соединенные четвертый резистор и четвертый транзистор (n-p-n), свободный вывод четвертого резистора соединен с выходом питающего источника, отличающийся тем, что в него введены дополнительный транзистор (p-n-p) противоположного типа проводимости и три дополнительных резистора, дополнительный транзистор и первый дополнительный резистор между собой включены последовательно, эмиттер дополнительного транзистора соединен с общим выводом второго резистора и коллектора второго транзистора, база дополнительного транзистора подключена к общему выводу четвертого резистора и коллектора четвертого транзистора, общий вывод коллектора дополнительного транзистора и первого дополнительного резистора соединен с базой четвертого транзистора, свободный вывод первого дополнительного резистора подключен к выходу логического элемента, второй дополнительный резистор включен между эмиттером четвертого транзистора и выходом логического элемента, а третий дополнительный резистор - между «землей» и общим выводом четвертого резистора, коллектора четвертого транзистора и базы дополнительного транзистора.

| В.Г | |||

| ГУСЕВ, Ю.М | |||

| ГУСЕВ | |||

| Электроника и микропроцессорная техника, Москва, "Высшая школа", 2005, стр | |||

| Прибор для изменения шага резьбы при токарных винторезных | 1921 |

|

SU593A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Логическая схема или-и-не | 1973 |

|

SU474109A1 |

| Логический элемент И-НЕ ИШЛ | 1985 |

|

SU1262720A1 |

| US 6426652 B1, 30.07.2002. | |||

Авторы

Даты

2019-07-09—Публикация

2018-05-22—Подача