(Л

с

4;;

со

00

.

м

11Д

Изобретение относится к вычислительной технике и может быть использовано в системах обработки многоканальной информшдии, поступающей в вычислительную машину () от удаленньт несинхронизированньк между собой / групп источников.

Целью изобретения является повьше

том нестабильности генераторов импульсов, произвольности момента начала опроса источников информации в каждой группе, а также задержек передачи через линии связи) КИ поступают в разные каналы в произвольные моменты времени. Для одновременного ввода информации в ВМ со всех каналов необ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1986 |

|

SU1381523A2 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1983 |

|

SU1116423A1 |

| Многоканальное устройство для сопряжения | 1985 |

|

SU1282142A1 |

| Устройство для управления монтажом магнитной видеозаписи | 1990 |

|

SU1700598A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

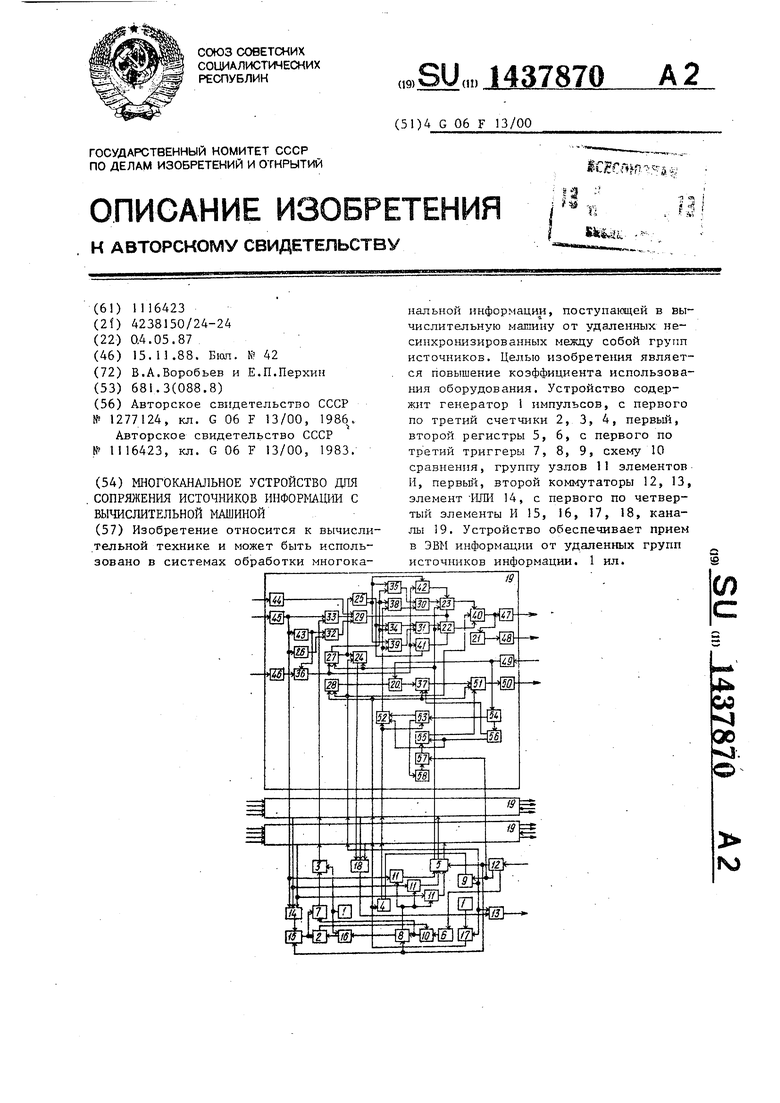

Изобретение относится к вычисли- .тельной технике и может быть использовано в системах обработки многоканальной информации, поступающей в вычислительную машину от удаленных не- синхро1шзированных между собой групп источников. Целью изобретения является повь шение коэффициента использования оборудования. Устройство соде.р- жит генератор импульсов, с первого по третий счетчики 2, 3, 4, первьй, второй регистры 5, 6, с первого по третий триггеры 7, 8, 9, схему 10 сравнения, группу узлов 11 элементов- И, первьиЧ, второй коммутаторы 12, 13, элемент iDUi 14, с первого по четвертый элементы И 15, 16, 17, 18, каналы 9. Устройство обеспечивает прием в ЭВМ информации от удаленных групп источников информации. 1 ил.

15

25

30ние коэффициента использования обору- JQ ходимо произвести выравнивание момен- дования.

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит генератор 1 импульсов, с первого по третий счетчики 2,3 и Д, первый и второй регистры 5 и 6, с первого по третий триггеры 7,8 и 9j схему 10 сравнения, группу узлов 11 элементов И, первьш и второй коммутаторы 2 и 13, элемент ИЛИ 1Д, с первого по четвертьй элементы 15,16,17 и 18, каналы 19.

Калодый канал 19 содержит память 20, сумматор 2 Г, первую и вторую бу- фер1а1е памяти 22 и 23, первый и второй триггеры 24 и 25, первый, второй и третий счетчики 26, 27 и 28, первый, второй и третий узлы элементов ИЛИ 29,30 и 31, первый, второй, третий и четвертый узлы элементов И 32, 33,34 и 35, элемент ИЛИ 36, с первого по третий элементы И 37,38 и 39, первый коммутатор 40s первый и второй элементы И-НЕ 41 и 42, первый элемент 43 задержки, с первого по седьмой согласу}сщие узлы 44,45,46|,47, 48,49 и 50, третий и второй коммутаторы 51 и 52J блок 53 памяти, дешифратор 54, четвертьй элемент И 55, третий и четвертый триггеры 56 и 57, второй элемент 58 задержки.

Устройство работает следующим образом.

Все источники информации опраши- ваются примерно с одинаковой частотой , которая для каждого из источников задается тактовыми импульсами (ТИ), поступающими через-вторые тактовые входы.

Однократный опрос всех источников информации одной группы образует кадр, который сопровождается кадровым импульсом (КИ) 1, поступающим на первые тактовые входы.

Каждая группа источников информации обслуживается своим каналом 19 и синхронизируется своим генератором импульсов, расположенным вместе с ис- тсгчниками информации, поэтому (с учетов окончания загрузки памяти 22 и 23 всех каналов к единому времени,, с которого может быть начат. этот ввод,

в работе устройства следует выделить два основных режима работы - подготовительный и рабочий.

Подготовительный режим начинается с момента записи кода времени в ре- 20 гистр 6, поступающего из ВМ через коммутатор 12 и определяющего-максимальное значение временного интервала, необходимого для ввода одного массива информации в ВМ. Одновременно с подачей кода времени ВМ сьшмает сигнал прерывания ввода, поступа ющий на элемент И 15, триггер 8 управления, регистр 5 разрешения ввода, триггер 9 считывания и четвертый триггер 57 разрешения, снимая их блокировку и обеспечивая готовность устройства к работе. В каждом канале вторые синхросигналы через согласую- |Цие узлы 45 поступают на элемент ИЛИ 145 с выхода которого через элемент И 15 объединенный поток синхросигналов поступает на входы установки О счетчика 2 тактов и триггера 7 управления. Счетчик 2 тактов предназначен для измерения длительности временньсх интервалов между кадровыми синхросигналами. Он подсчитывает тактовые импульсы, поступающие с выхода генератора импульсов через элемент И 16, при наличии разрешаквдего сигнала с триггера 8, предварительно установленного в исходное положение сигналом прерывания ввода.

Схема 10 сравнения формирует сигнал при совпадении кодов счетчика 2 и регистра 6, т.е. при обнаружении временного интервала между первыми синхросигналами, равного и превьшзаю- щего заданную длительность, определенную значением кода, записанного из ВМ в регистр 6. Сигнал совпадения поступает на входы триггеров 7 и 8, изменяя их состояние. С этого момента триггер 8 блокирует элемент И 16,

35

40

45

50

55

5

5

0Q ходимо произвести выравнивание момен-

тов окончания загрузки памяти 22 и 23 всех каналов к единому времени,, с которого может быть начат. этот ввод,

в работе устройства следует выделить два основных режима работы - подготовительный и рабочий.

Подготовительный режим начинается с момента записи кода времени в ре- 0 гистр 6, поступающего из ВМ через коммутатор 12 и определяющего-максимальное значение временного интервала, необходимого для ввода одного массива информации в ВМ. Одновременно с подачей кода времени ВМ сьшмает сигнал прерывания ввода, поступа ющий на элемент И 15, триггер 8 управления, регистр 5 разрешения ввода, триггер 9 считывания и четвертый триггер 57 разрешения, снимая их блокировку и обеспечивая готовность устройства к работе. В каждом канале вторые синхросигналы через согласую- |Цие узлы 45 поступают на элемент ИЛИ 145 с выхода которого через элемент И 15 объединенный поток синхросигналов поступает на входы установки О счетчика 2 тактов и триггера 7 управления. Счетчик 2 тактов предназначен для измерения длительности временньсх интервалов между кадровыми синхросигналами. Он подсчитывает тактовые импульсы, поступающие с выхода генератора импульсов через элемент И 16, при наличии разрешаквдего сигнала с триггера 8, предварительно установленного в исходное положение сигналом прерывания ввода.

Схема 10 сравнения формирует сигнал при совпадении кодов счетчика 2 и регистра 6, т.е. при обнаружении временного интервала между первыми синхросигналами, равного и превьшзаю- щего заданную длительность, определенную значением кода, записанного из ВМ в регистр 6. Сигнал совпадения поступает на входы триггеров 7 и 8, изменяя их состояние. С этого момента триггер 8 блокирует элемент И 16,

5

0

5

0

5

запрещая подачу на счетчик 2 импульсов с генератора 1. Сигналом с другого выхода триггер 8 разрешает через узлы 11 выдачу первых синхроимпульсов на регистр 5. С выхода регистра 5 сигналы разрешения поступают в каждом канапе на выходы счетчика 27 адреса записи, триггера 24 готовности памятей 22 и 23, снимая их блокировку и переводя в рабочий режим. Триггер 8 готовности опорным первым синхроимпульсом, пришедшим после сигнала совпадения с выхода схемы 10 сравнения, вновь устанавливается в исходное состояние, формируя на своем выходе импульсный сигнал, который поступает на вход установки О счетчика 3 времени задержпамятей 22 и 23. Управление режимами записи и считывания осуществляется сигналами с триггера 25 переполнения,

ки, который подсчитывает тактовые им- 20 мации, который поступает с его выхо- пульсы с выхода генератора 1, форми- да через узлы 34,35,30 и 31 на входы руя тем самым код времени задержки поступления первых синхроимпульсов относительно опорного первого синхросигнала. .25 работающего в счетном режиме от сиг- Рабочий режим устройства обеспечи- налов переноса счетчика 27.

После записи массива информагщи в объеме одного кадра триггер 25 закрывает входы узла 35, элемента И 39, 30 элемента И-НЕ 42 и открывает входы . узла 34, элемента И 38 и элемента И-НЕ 41, обеспечивая тем самым перевод памяти 22 в режим записи путем подачи на него кода адреса записи и g первых синхросигналов, а также подготавливая память 23 для режима считывания. Кроме того, сигнал переноса подается на триггер 24 готовности, который при его поступлении формиру- 40 ет сигнал готовности канала к вйводу информации в ВМ, который поступает на элемент И 18, который при наличии указанных сигналов формирует сигнал запроса ввода, поступающий через ком- 26 путем подсчета первых синхросигна- 45 мутатор 13 в ВМ. Ответам ВМ на сиг- лов, поступающих через узел 45. Ввод нал запроса ввода является сигнал

разрешения ввода, поступающий на входы триггеров 9 и 57 через коммутатор

вает загшеь и считывание информации в памяти 22 и 23, поочередно накапли- ваюише и счить вающие массивы данных в объеме одного кадра информации.

Запись информации осуществляется следующим образом.

Информационные сигналы в виде многоканального цифрового потока от ж группы источников информации поступают на информационный вход канала и через узел 44 подаются на вход узла 29. На другие входы узла 29 поступают с выходов узлов 33 и 32 элементов И соответственно код времени задержки и код текущего -номера кадра с выходов счетчика 3 времени задержки и счетчика 26 кадров. Код текущего номера кадра формируется счетчиком

кода текущего номера кадра в информационный поток осуществляется узлом 29 в момент поступления задержанного кадрового импульса с элемента 43 задержки, задержка в котором равна половине периода вторых синхроимпульсов. Ввод кода времени задержки осуществляется узлом 29 в момент поступления первого синхросигнала.

Сформированньй информационный поток с выхода узла 29 записывается в памяти 22 и 23, которые работают в, так называемом режиме качелей : обе

Устройство обладает возможностью по инициативе ВМ производить, в кажпамяти работают в одном из двух режи МОЕ - когда в одной накагшивае,тся информация, из другой уже накопленная информация передается в БМ; затем режимы работы меняются на проти воположные.

Первые синхросигналы, поступающие на вход канала через узел 46, а также задержанные вторые синхросигналы с выхода элемента 43 задержки объединяются на элементе ШШ 36 и далее поступают на вход счетчика 27 адреса записи и выходы элементов И-НЕ 41 и

мации, который поступает с его выхо- да через узлы 34,35,30 и 31 на входы работающего в счетном режиме от сиг- налов переноса счетчика 27.

Устройство обладает возможностью по инициативе ВМ производить, в каж

дом канале селективную синхронизацию вводимой в ВМ информации из памятей 22 и 23. При этом следует выделить два режима работы. В первом режиме работы осуществляется селекция вводимых каналов в ВМ без изменения их , порядкового номера в кадре, т.е. изменения их порядкового номера считывания при вводе в ВМ. Выбор режима ввода информации осуществляется по команде от ВМ по управлякщему входу ка;вдого канала через узел 49, Управление режиНами производится триггером 56. Рассмотрим работу канала 19 в об.оик режимах. В первом режиме работы триггер 56 по команде от ВМ, выделенной девшфратором. 54j устанавли. вается в соответствующее положение, открывая сигналом со своего выхода элемент И 37 и закрывая элемент И 55 Сигнал с выхода элемента И 55 открывает коммутатор 51 для передачи сигналов с выхода элемента И 37. Управляющая информация, содержащая адреса каналов и признаки их передач, поступает от ВМ через узел 49 в память 20 При вводе информации в ВН производится считывание признаков передачи каналов из памяти 20 по адресам, поступающим с выхода счетчика 28 каналов при наличии сигнала строба считывания. Формирование кода адреса осуществляется от сигналов тактовой частоты считьюания, получаемых с выхода

.элемента И 17. Считанные с выхода

памяти 20 признаки передачи каналов етробируются на элементе И 37 сигналами тактовой частоты считьшания и через коммутатор 51 и узел 50 вводят- ся в ВМ. При этом си гналы кода адреса считывания поступают на входы элементов И 38 и 39 с выхода счетчика 4 адреса считывания через коммутатор

..52, управляемый триггером 56.

Во втором режиме по команде от ВМ триггер 56 переводится в противоположное состояние. При этом элемент И 37 закрывается, коммутатор 52 сво им вторым информационным входом подключается к выходу блока 53 памяти,

|элемент И 55 разблокируется. Управ- лянщая информация в виде адресной маски, содержащей адреса каналов и определяннцей очередность считывания каналов из памятей 22 и 23, поступает от ВМ через узел 49, дешифрируется дешифратором 54 и записывается в блок 53 памяти. При этом имеете о

5

0

0

адресом последнего канала в адресной маске записывается соответствующий однобитовый признак. По сигналу раз- решения ввода от ВМ, поступающего с выхода коммутатора 12, взводится триггер 57, переключая через элемент. И 55 коммутатор 51 на передачу в ВМ признаков передачи каналов, сформированных от сигналов тактовой частоты с выхода элемента И 17. Одновременно по сигналам счетчика 4 адреса считывания начинается считьшание из блока 53 памяти адресной маски и выдача ее через коммутатор 52 на один из элементов-И 38 и 39 и один из узлов 30,31 на вход тон памяти 2-2 и 23, которая работает в режиме считьшания, обеспечивая таким образом произвольную переупаковку выдаваемых каналов па ВМ в зависимости от записанной адресной маски. При передаче последнего канала в цикле вьщачя однобитовый признак после,цнего канала с выхода 5 блока 53 памяти, задержанный на элементе 58 задержки, устанавливает триггер 57 в исходное cccTOHi-me, тем самым снимая сигнал на выходе элемента И 55, Коммутатор 51 выключается и прекршцает вьщачу в ВМ признаков передачи каналов. В новом цикле ввода информации в ВМ указа1шый порядок работы повторя ется.

35

ормула изобретения

0

5

0

Многоканальное устройство для сопряжения источников информац1-ш с вычислительной машиной по авт. св. № 116423, отличающееся тем, что, с целью повьшения коэффициента использования оборудования, в каждый канал введены второй, третий комм таторЫ; блок памяти, дешифратор, четвертый элемент И, третий, четвертый триггеры, второй элемент задержки, причем в каждом канапе вход дешифратора соединен с выходом шестого согласующего узла, первый, второй выходы дешифратора соединены соответственно с информационным входом блока памяти и с входом третьего триггера, первый выход которого соединен с третьим входом первого эле- 5 мента И, второй выход третьего триггера cc eдинeн с первым входом четвертого элемента И и с управлягацим входом второго коммутатора, первый информационный вход которого соеди714378708

нен с первым выходом блока памяти, выходом первого коммутатора, выход второй информационный вход второго четвертого триггера соединен с вто- коммутатора и адресный вход блока рым входом четвертого элемента И, памяти соединены с первым выходом выход которого соединен с управляю- третьего счетчика, выход второго ком- щим входом третьего коммутатора, пер- мутатора соединен с вторыми входами вый, второй информационные входы и второго и третьего элементов И, вто- выход которого соединены соответст- рой выход блок памяти через второй венно с выходом первого элемента И, элемент задержки соединен с нулевым ю выходом третьего элемента И и вхо- входом четвертого триггера, еш1нич- дом седьмого согласующего узла, ный вход которого соединен с первым

| Устройство для сопряжения электронно-вычислительной машины с абонентом | 1985 |

|

SU1277124A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1983 |

|

SU1116423A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-15—Публикация

1987-05-04—Подача