сд

Од 00

Изобретение относится, к вычислительной технике, в частности к запоминающим устройствам на цилиндрических магнитных доменах (ЦМД), и может быть использовано в составе систем внешней энергонезависимой памяти ЭВМ

Цель изобретения - повьшение бы- стродегйствия и расширение области пр менения устройства за счет использования доменных микросборок с произвольным числом годных регистров и выполнения функций эмуляции запоминающих устройств на магнитных дисках.

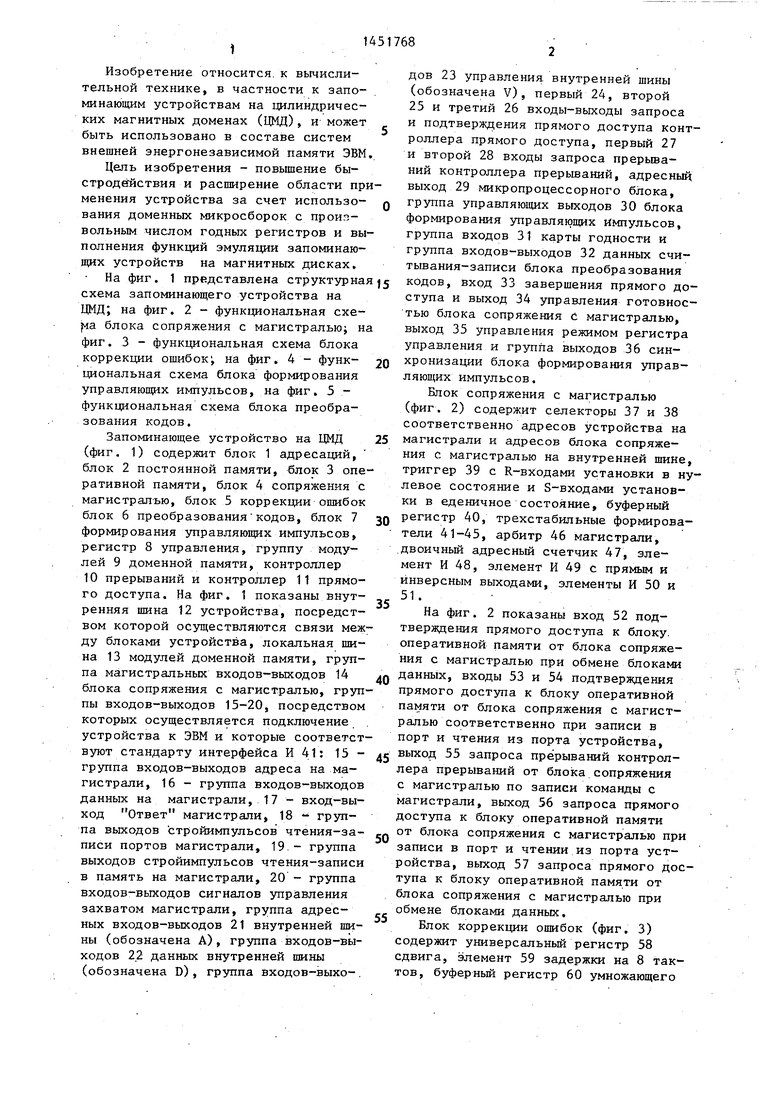

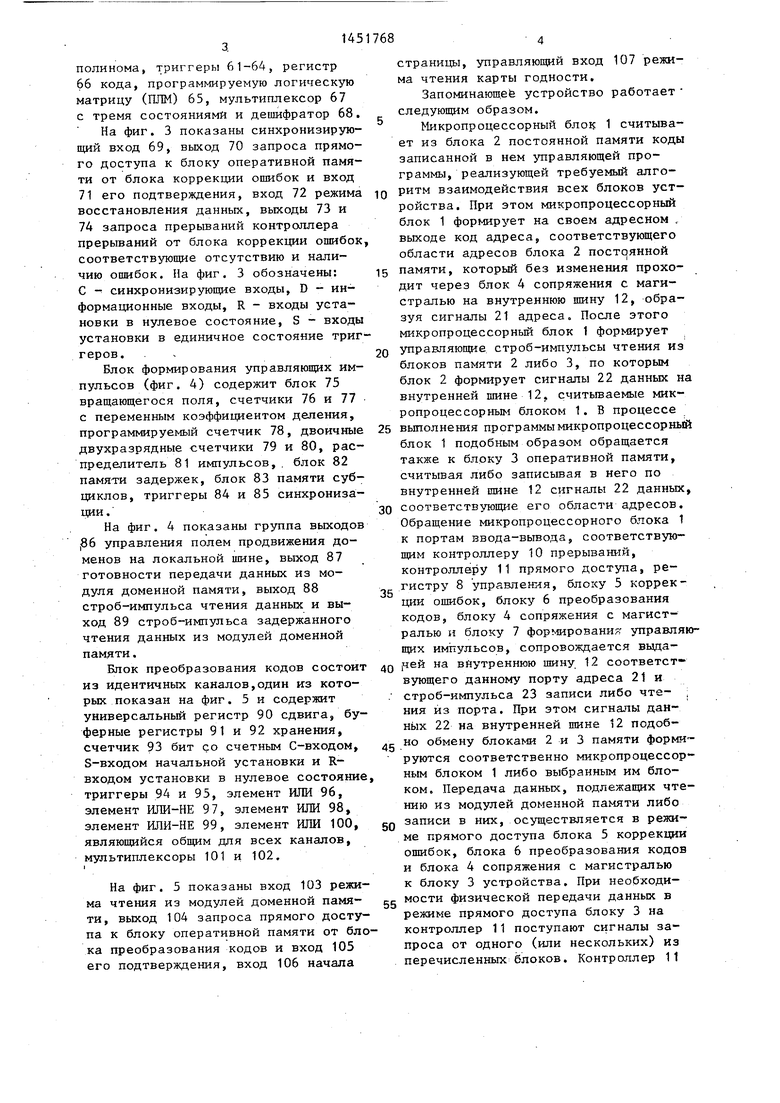

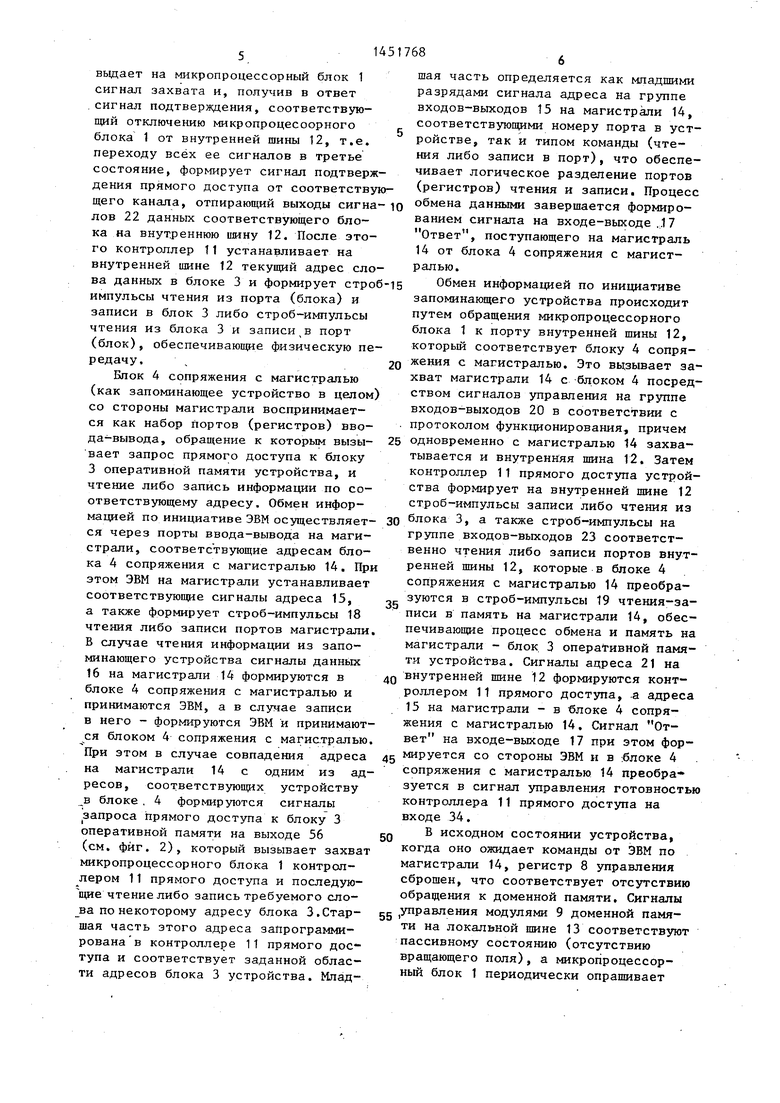

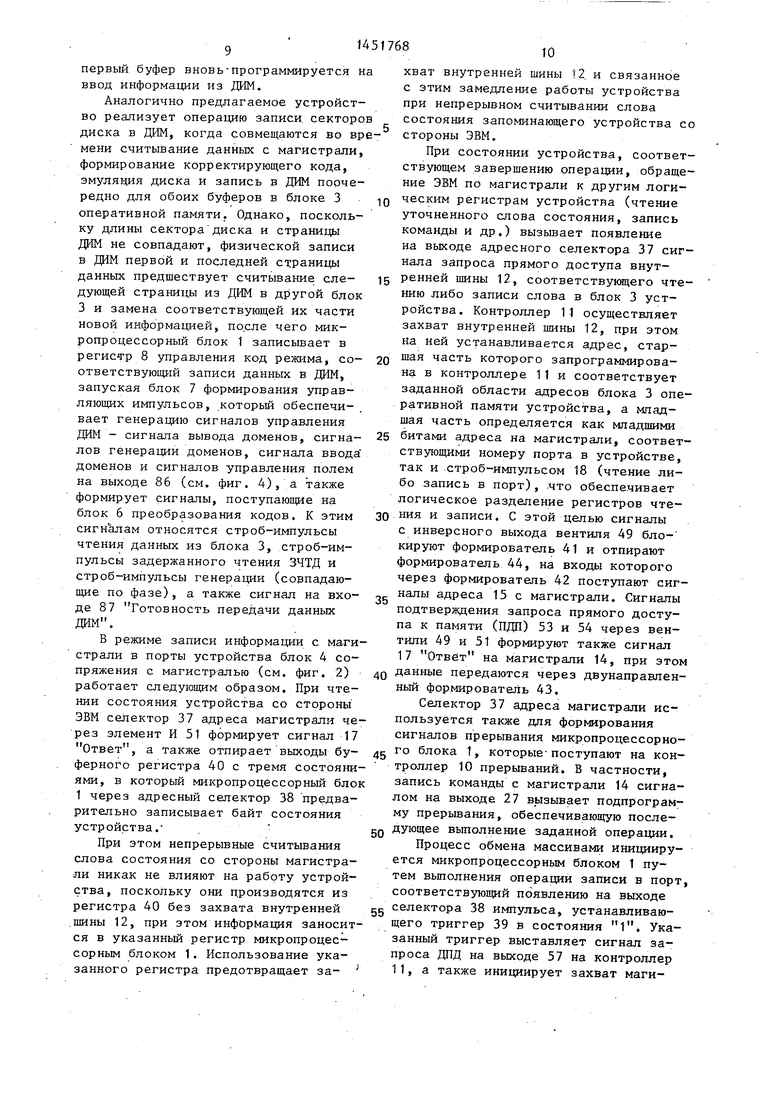

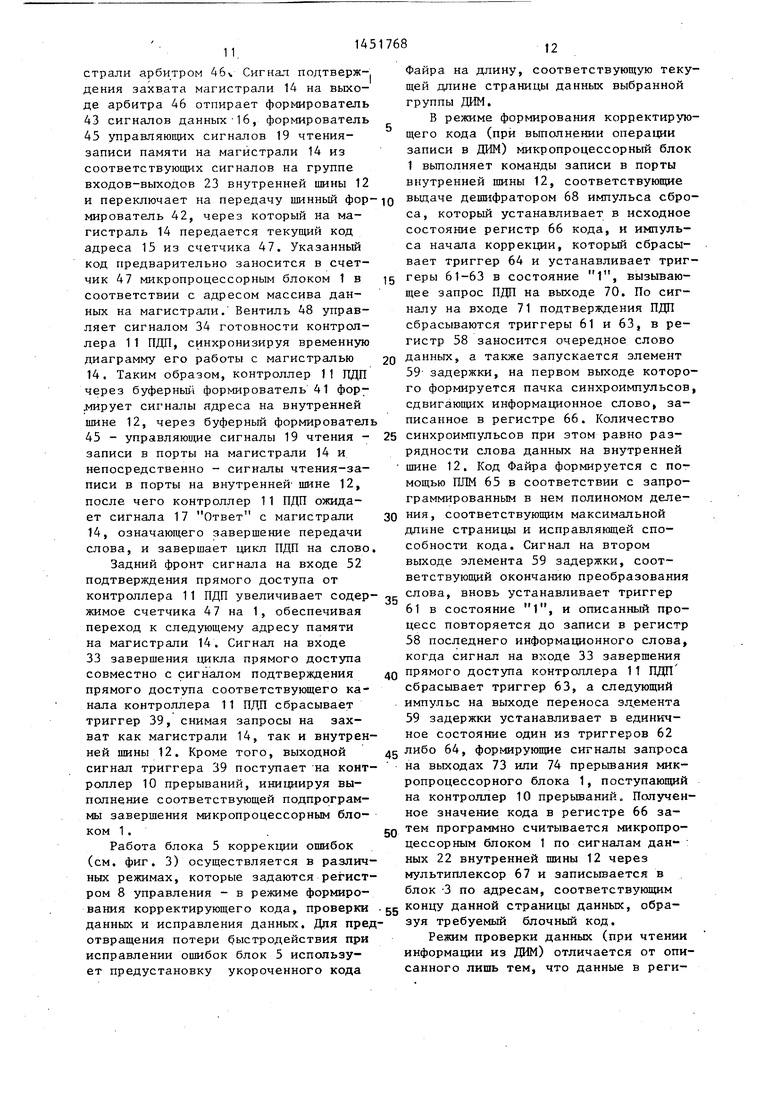

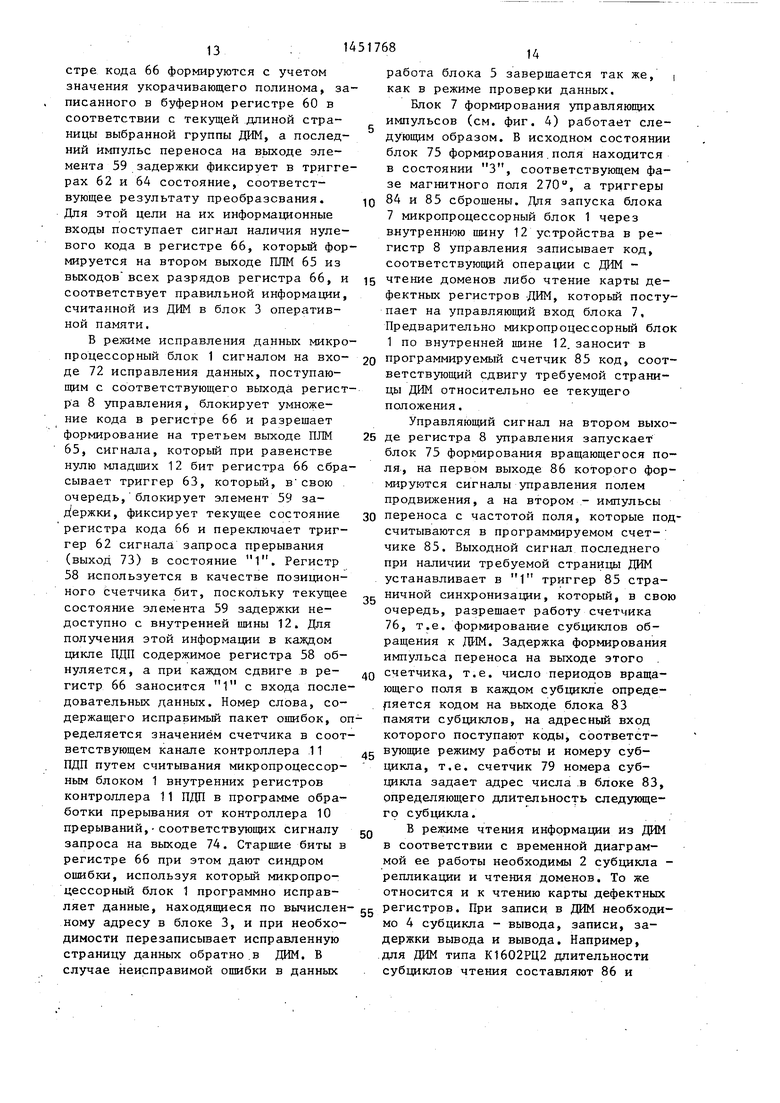

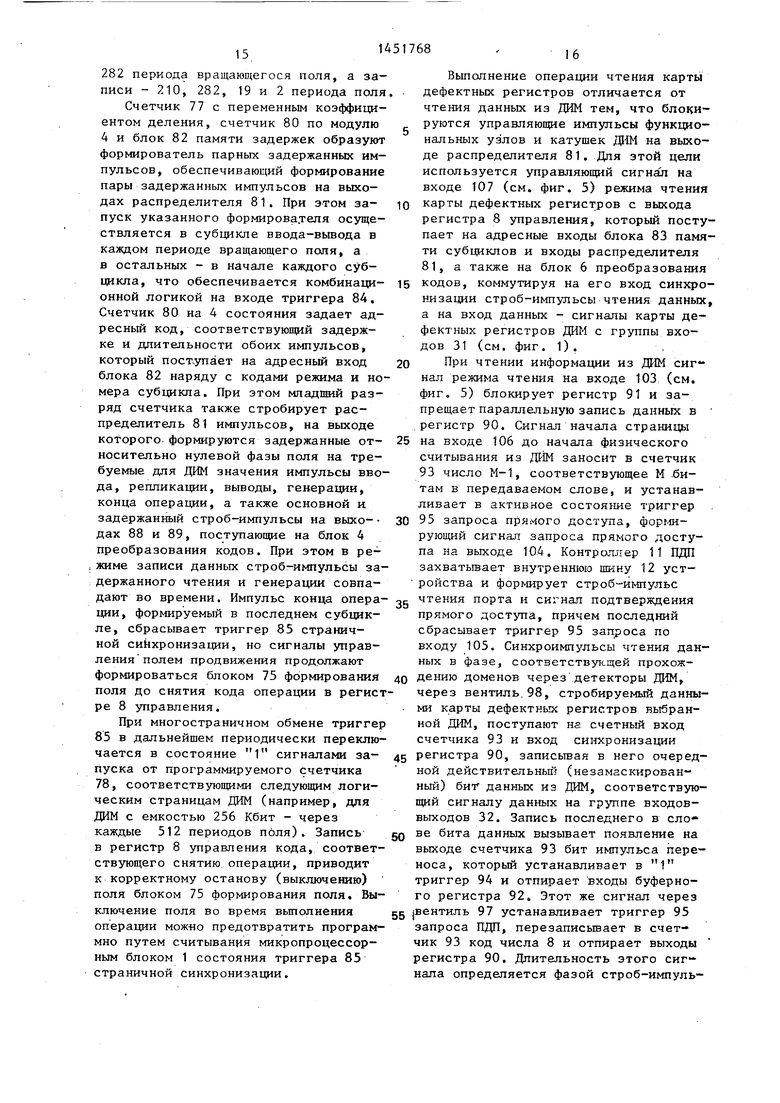

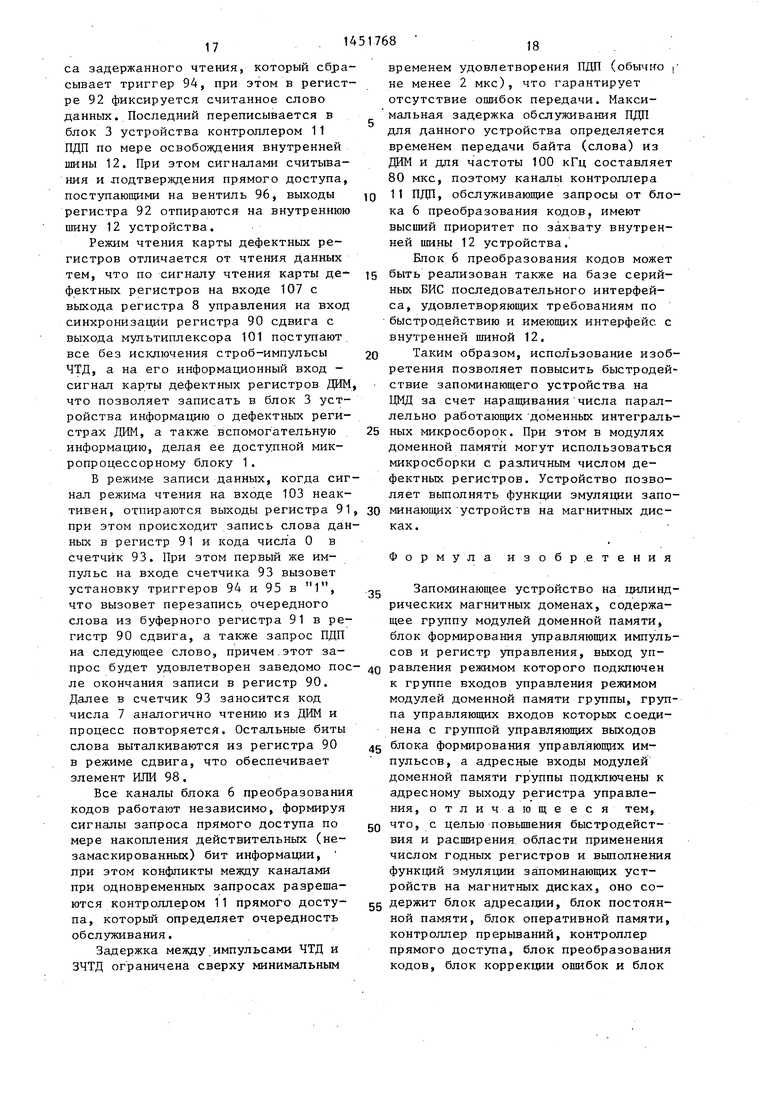

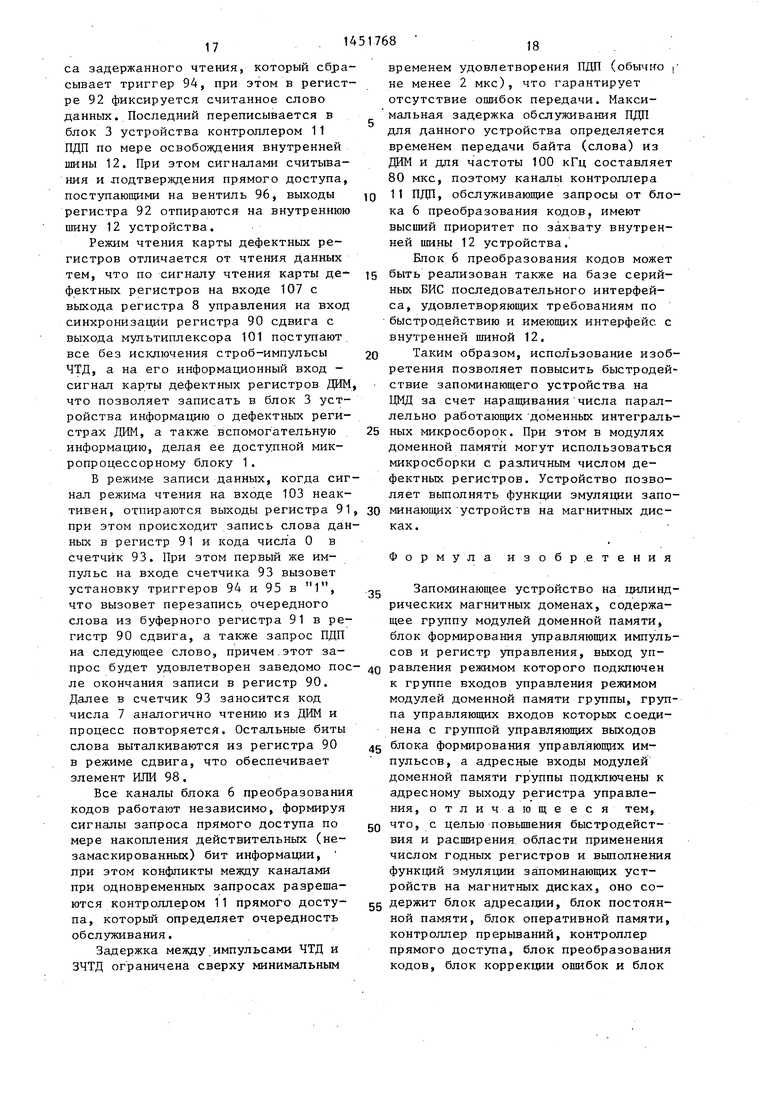

На фиг. 1 представлена структурна схема запоминающего устройства на ЦМД; на фиг. 2 - функциональная схе- блока сопряжения с магистралью н фиг. 3 - функциональная схема блока коррекции ошибок на фиг. 4 - функциональная схема блока формирования управляющих импульсов, на фиг. 5 - функциональная схема блока преобразования кодов.

Запоминающее устройство на ЦМД (фиг. 1) содержит блок 1 адресаций, блок 2 постоянной памяти, блок 3 оперативной памяти, блок 4 сопряжения с магистралью, блок 5 коррекции ошибок блок 6 преобразования кодов, блок 7 формирования управляющих импульсов, регистр 8 управления, группу модулей 9 доменной памяти, контроллер 10 прерываний и контроллер 11 прямого доступа. На фиг. 1 показаны внутренняя шина 12 устройства, посредством которой осуществляются связи меж ду блоками устройства, локальная шина 13 модулей доменной памяти, группа магистральных входов-выходов 14 блока сопряжения с магистралью, груп пы входов-выходов 15-20, посредством которых осуществляется подключение устройства к ЭВМ и которые соответствуют стандарту интерфейса И 41: 15 - группа входов-выходов адреса на магистрали, 16 - группа входов-выходов данных на магистрали, 17 - вход-выход Ответ магистрали, 18 - группа вькодов стройимпульсов чтения-записи портов магистрали, 19.- группа выходов стройимпульсов чтения-записи в память на магистрали, 20 - группа входов-выходов сигналов управления захватом магистрали, группа адресных входов-выходов 21 внутренней шины (обозначена А), группа входов-выходов 22 данных внутренней шины (обозначена D), группа входов-выхо-,

5

5

0

5

0

5

0

5

дов 23 управления внутренней шины (обозначена V), первый 24, второй 25 и третий 26 входы-выходы запроса и подтверждения прямого доступа контроллера прямого доступа, первый 27 и второй 28 входы запроса прерьша- ний контроллера прерываний, адресный выход 29 микропроцессорного блока, группа управляющих выходов 30 блока формирования управляющих импульсов, группа входов 31 карты годности и группа входов-выходов 32 данных считывания-записи блока преобразования кодов, вход 33 завершения прямого доступа и выход 34 управления готовностью блока сопряжения с магистралью, выход 35 управления режимом регистра управления и группа выходов 36 синхронизации блока формирования управляющих импульсов.

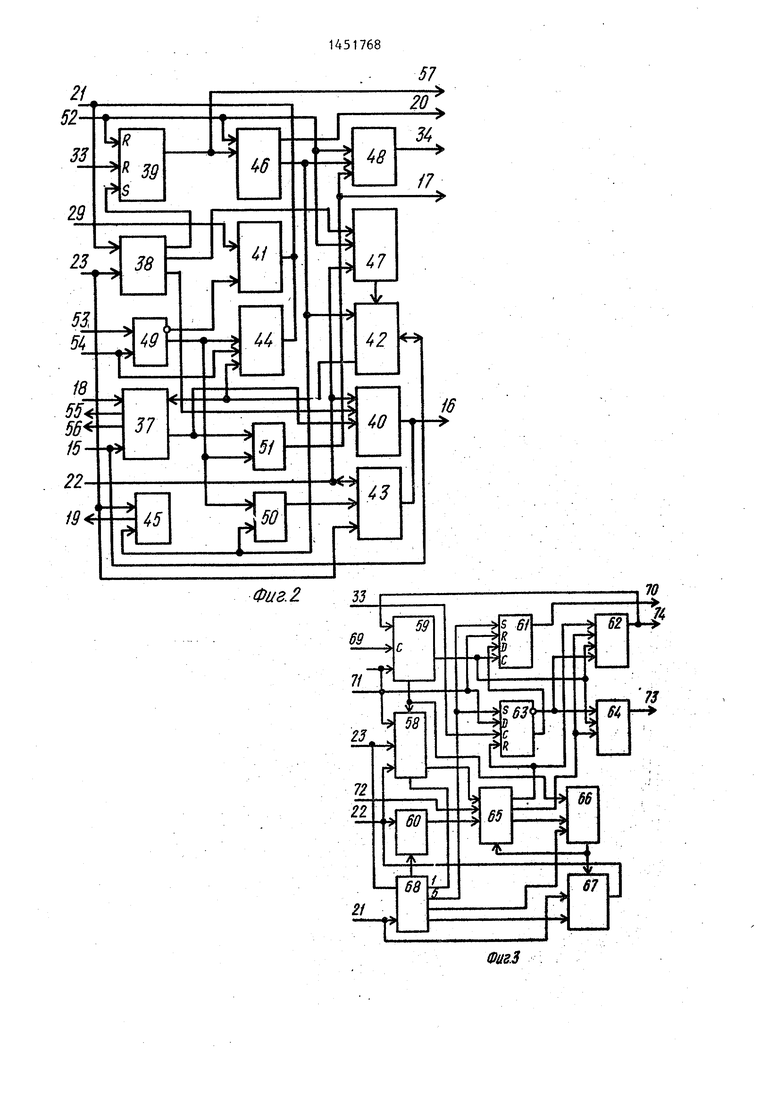

Блок сопряжения с магистралью (фиг. 2) содержит селекторы 37 и 38 соответственно адресов устройства на магистрали и адресов блока сопряжения с магистралью на внутренней шине, триггер 39 с R-входами установки в нулевое состояние и S-входами установки в еденичное состояние, буферный регистр 40, трехстабильные формирователи 41-45, арбитр 46 магистрали, .двоичньй адресный счетчик 47, элемент И 48, элемент И 49 с прямым и инверсным выходами, элементы И 50 и 51.

На фиг. 2 показаны вход 52 под- тверлздения прямого доступа к блоку, оперативной памяти от блока сопряжения с магистралью при обмене блоками данных, входы 53 и 54 подтверждения прямого доступа к блоку оперативной памяти от блока сопряжения с магистралью соответственно при записи в порт и чтения из порта устройства, выход 55 запроса прерываний контроллера прерываний от блока.сопряжения с магистралью по записи команды с магистрали, выход 56 запроса прямого доступа к блоку оперативной памяти от блока сопряжения с магистралью при записи в порт и чтении из порта устройства, выход 57 запроса прямого доступа к блоку оперативной памяти от блока сопряжения с магистралью при обмене блоками данных.

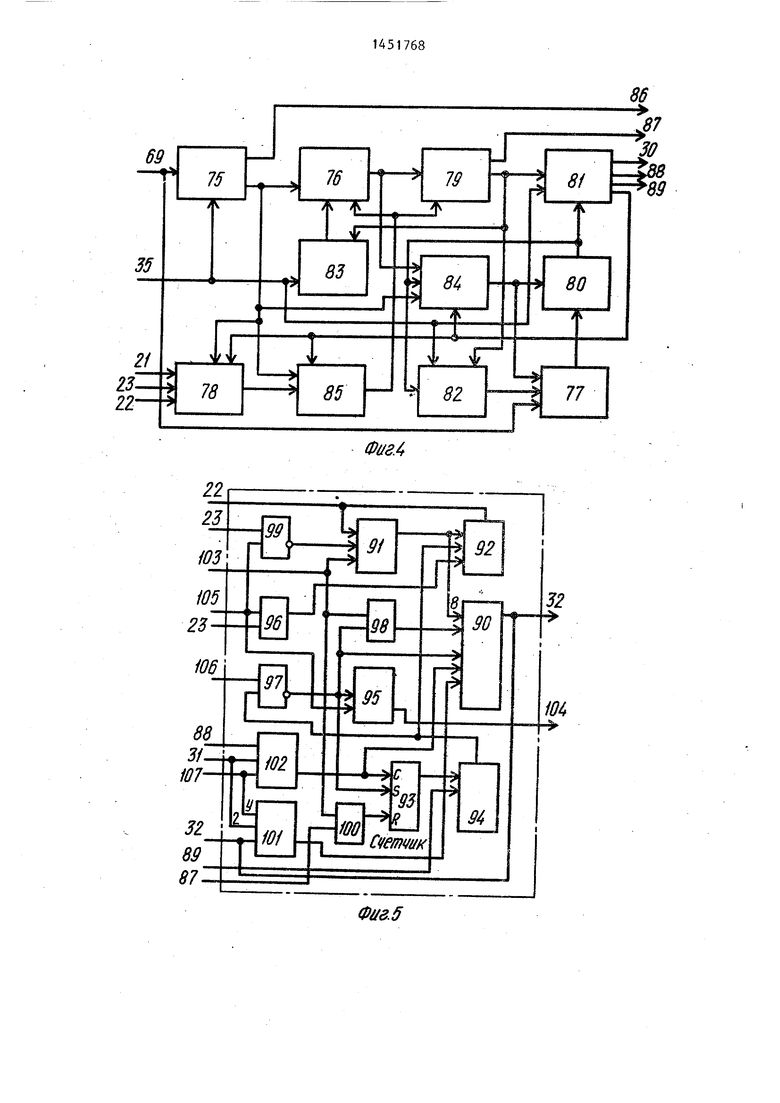

Блок коррекции ошибок (фиг. 3) содержит универсальньй регистр 58 сдвига, элемент 59 задержки на 8 тактов, буферный регистр 60 умножающего

3,

1451768

полинома, триггеры 61-64, регистр 66 кода, программируемую логическую матрицу (ГШМ) 65, мультиплексор 67 с тремя состояниями и дешифратор 68. На фиг. 3 показаны синхронизирующий вход 69, выход 70 запроса прямого доступа к блоку оперативной памяти от блока коррекции ошибок и вход 71 его подтверждения, вход 72 режима восстановления данных, выходы 73 и 74 запроса прерываний контроллера прерываний от блока коррекции ошибок соответствующие отсутствию и наличию ошибок. На фиг. 3 обозначены: С - синхронизирующие входы, D - информационные входы, R - входы установки в нулевое состояние, S - входы установки в единичное состояние триггеров.

Блок формирования управляющих импульсов (фиг. 4) содержит блок 75 вращающегося поля, счетчики 76 и 77 с переменным коэффициентом деления, программируемый счетчик 78, двоичные двухразрядные счетчики 79 и 80, распределитель 81 импульсов,. блок 82 памяти задержек, блок 83 памяти субциклов, триггеры 84 и 85 синхронизации.

На фиг. 4 показаны группа выходов |86 управления полем продвижения доменов на локальной шине, выход 87 готовности передачи данных из модуля доменной памяти, выход 88 строб-импульса чтения данных и выход 89 строб-импульса задержанного чтения данных из модулей доменной памяти.

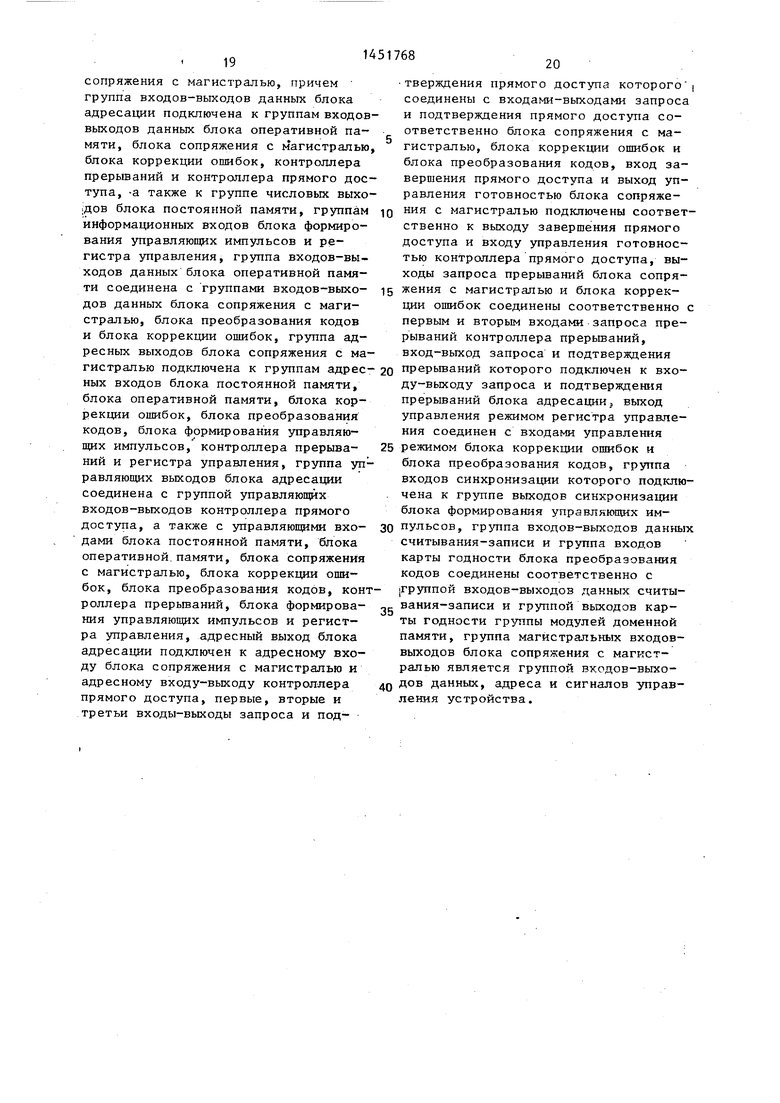

Клок преобразования кодов состоит из идентичных каналов,один из которых показан на фиг. 5 и содержит универсальный регистр 90 сдвига, буферные регистры 91 и 92 хранения, счетчик 93 бит со счетным С-входом, S-входом начальной установки и R- входом установки в нулевое состояние триггеры 94 и 95, элемент ИЛИ 96, элемент ИЛИ-НЕ 97, элемент ИЛИ 98, элемент ИЛИ-НЕ 99, элемент ИЛИ 100, являющийся об1цим для всех каналов, мультиплексоры 101 и 102.

На фиг. 5 показаны вход 103 режима чтения из модулей доменной памяти, выход 104 запроса прямого доступа к блоку оперативной памяти от блока преобразования кодов и вход 105 его подтверждения, вход 106 начала

страницы, управляющий вход 107 режима чтения карты годности.

Запоминающее устройство работает следующим образом.

Микропроцессорный блок 1 считывает из блока 2 постоянной памяти коды записанной в нем управляющей программы, реализующей требуемый алгоритм взаимодействия всех блоков устройства. При этом микропроцессорный блок 1 формирует на своем адресном , выходе код адреса, соответствующего области адресов блока 2 постоянной

5 памяти, который без изменения проходит через блок 4 сопряжения с магистралью на внутреннюю шину 12, образуя сигналы 21 адреса. После этого микропроцессорньш блок 1 формирует

0 управляющие строб-импульсы чтения из блоков памяти 2 либо 3, по которым блок 2 формирует сигналы 22 данных на внутренней щине 12. считываемые микропроцессорным блоком 1. В процессе

5 выполнения программы микропроцессорный блок 1 подобным образом обращается также к блоку 3 оперативной памяти, считывая либо записывая в него по внутренней шине 12 сигналы 22 данных,

о соответствующие его области адресов. Обращение микропроцессорного блока 1 к портам ввода-вывода, соответствующим контроллеру 10 прерываний, контроллеру 11 прямого доступа, регистру 8 управления, блоку 5 коррекции ошибок, блоку 6 преобразования кодов, блоку 4 сопряжения с магистралью и блоку 7 формирования управляющих импульсов, сопровождается выда0 (Чей на внутреннюю шину 12 соответствующего данному порту адреса 21 и .- строб-импульса 23 записи либо чте- , НИН из порта. При этом сигналы данных 22 на внутренней шине 12 подобно обмену блоками 2 и 3 памяти формируются соответственно микропроцессорным блоком 1 либо выбранным им блоком. Передача данных, подлежащих чтению из модулей доменной памяти либо записи в них, осуществляется в режиме прямого доступа блока 5 коррекции ошибок, блока 6 преобразования кодов и блока 4 сопряжения с магистралью к блоку 3 устройства. При необ ходи- .-.- мости физической передачи данных в

п

режиме прямого доступа блоку J на контроллер 11 поступают сигналы запроса от одного (или нескольких) из перечисленных блоков. Контроллер 11

5

выдает на микропроцессорный блок 1 сигнал захвата и, получив в ответ сигнал подтверждения, соответствующий отключению микропроцесоорного блока 1 от внутренней шины 12, т.е. переходу всех ее сигналов в третье состояние, формирует сигнал подтверждения прямого доступа от соответствуюшая часть определяется как младшими разрядами сигнала адреса на группе входов-выходов 15 на магистрали 14, соответствующими номеру порта в уст ройстве, так и типом команды (чтения либо записи в порт), что обеспе чивает логическое разделение портов (регистров) чтения и записи. Процес

щего канала, отпирающий выходы сигна- ю обмена данными завершается формиро20

25

30

лов 22 данных соответствующего блока на внутреннюю шину 12. После этого контроллер 11 устанавливает на внутренней шине 12 текущий адрес слова данных в блоке 3 и формирует строб-15 импульсы чтения из порта (блока) и записи в блок 3 либо строб-импульсы чтения из блока 3 и записи в порт (блок), обеспечивающие физическую передачу,

Бпок 4 сопряжения с магистралью (как запоминающее устройство в целом) со стороны магистрали воспринимается как набор портов (регистров) ввода-вывода, обращение к которым вызывает запрос прямого доступа к блоку 3 оперативной памяти устройства, и чтение либо запись информации по соответствующему адресу. Обмен информацией по инициативе ЭВМ осуществляется через порты ввода-вывода на магистрали, соответствующие адресам блока 4 сопряжения с магистралью 14. При этом ЭВМ на магистрали устанавливает соответствующие сигналы адреса 15, а также формирует строб-импульсы 18 чтения либо записи портов магистрали. В случае чтения информации из запоминающего устройства сигналы данньгх 16 на магистрали 14 формируются в блоке 4 сопряжения с магистралью и принимаются ЭВМ, а в случае записи в него - формируются ЭВМ и принимают- ся блоком 4 сопряжения с магистралью. При этом в случае совпадения адреса на магистрали 14 с одним из адресов, соответствующих устройству .в блоке , 4 формируются сигналы запроса прямого доступа к блоку 3 оперативной памяти на выходе 56 (см. фиг. 2), который вызывает захват микропроцессорного блока 1 контрол- лером 11 прямого доступа и последующие чтение либо запись требуемого сло- ва по некоторому адресу блока 3.Старшая часть этого адреса запрограммирована в контроллере 11 прямого доступа и соответствует заданной области адресов блока 3 устройства. Младванием сигнала на входе-вькоде ..17 Ответ, поступающего на магистраль 14 от блока 4 сопряжения с магистралью.

Обмен информацией по инициативе запоминающего устройства происходит путем обращения микропроцессорного блока 1 к порту внутренней шины 12, который соответствует блоку 4 сопряжения с магистралью. Это вызывает за хват магистрали 14 с блоком 4 посред ством сигналов управления на группе входов-выходов 20 в соответствии с протоколом функционирования, причем одновременно с магистралью 14 захватывается и внутренняя щина 12. Затем контроллер 11 прямого доступа устрой ства формирует на внутренней щине 12 строб-импульсы записи либо чтения из блока 3, а также строб-импульсы на группе входов-выходов 23 соответственно чтения либо записи портов внутренней шины 12, которые в блоке 4 сопряжения с магистралью 14 преобразуются в строб-импульсы 19 чтения-записи в память на магистрали 14, обеспечивающие процесс обмена и память на магистрали - блок. 3 оперативной памяти устройства. Сигналы адреса 21 на 40 внутренней шине 12 формируются контроллером 11 прямого доступа, .а адреса 15 на магистрали - в блоке 4 сопряжения с магистралью 14. Сигнал Ответ на входе-выходе 17 при этом фор35

50

45 мируется со стороны ЭВМ и в :блоке 4 сопряжения с магистралью 14 преобразуется в сигнал управления готовностью контроллера 11 прямого доступа на входе 34.

В исходном состоянии устройства, когда оно ожидает команды от ЭВМ по магистрали 14, регистр 8 управления сброшен, что соответствует отсутствию обращения к доменной памяти. Сигналы

55 .управления модулями 9 доменной памяти на локальной шине 13 соответствуют пассивному состоянию (отсутствию вращающего поля), а микропроцессорный блок 1 периодически опрашивает

шая часть определяется как младшими разрядами сигнала адреса на группе входов-выходов 15 на магистрали 14, соответствующими номеру порта в устройстве, так и типом команды (чтения либо записи в порт), что обеспечивает логическое разделение портов (регистров) чтения и записи. Процесс

обмена данными завершается формирою обмена данными завершается формиро20

25

30

-15

ванием сигнала на входе-вькоде ..17 Ответ, поступающего на магистраль 14 от блока 4 сопряжения с магистралью.

Обмен информацией по инициативе запоминающего устройства происходит путем обращения микропроцессорного блока 1 к порту внутренней шины 12, который соответствует блоку 4 сопряжения с магистралью. Это вызывает захват магистрали 14 с блоком 4 посредством сигналов управления на группе входов-выходов 20 в соответствии с протоколом функционирования, причем одновременно с магистралью 14 захватывается и внутренняя щина 12. Затем контроллер 11 прямого доступа устройства формирует на внутренней щине 12 строб-импульсы записи либо чтения из блока 3, а также строб-импульсы на группе входов-выходов 23 соответственно чтения либо записи портов внутренней шины 12, которые в блоке 4 сопряжения с магистралью 14 преобразуются в строб-импульсы 19 чтения-записи в память на магистрали 14, обеспечивающие процесс обмена и память на магистрали - блок. 3 оперативной памяти устройства. Сигналы адреса 21 на 40 внутренней шине 12 формируются контроллером 11 прямого доступа, .а адреса 15 на магистрали - в блоке 4 сопряжения с магистралью 14. Сигнал Ответ на входе-выходе 17 при этом фор35

0

45 мируется со стороны ЭВМ и в :блоке 4 сопряжения с магистралью 14 преобразуется в сигнал управления готовностью контроллера 11 прямого доступа на входе 34.

В исходном состоянии устройства, когда оно ожидает команды от ЭВМ по магистрали 14, регистр 8 управления сброшен, что соответствует отсутствию обращения к доменной памяти. Сигналы

5 .управления модулями 9 доменной памяти на локальной шине 13 соответствуют пассивному состоянию (отсутствию вращающего поля), а микропроцессорный блок 1 периодически опрашивает

контроллер 10 прерывания, ожидая от блока 4 сопряжения с магистралью 14 прерывания, соответствующего команде ЭВМ: записи типа операции (чтение, запись, форматизация и др.) и ее параметров (дорожка, сектор диска, количество секторов, адрес буфера данных на магистрали и др.) по магистрали 14 в порты, соответствующие адресам устройства памяти на магистрали 1 4 .

В процессе выполнения требуемой операции взаимодействия с доменной

10

из ДИМ, строб-импульсы 89 задержанного чтения ЗЧТД и сигнал 87 Готовность передачи данных ДИМ.В процессе считывания данных из ДИМ блок 6 преобразования кодов формирует сигналы запроса прямого доступа на выходе 104, поступающие на контроллер 11 прямого доступа, и по получении от контроллера 11 сигналов подтверждения прямого доступа на входе 105 (см. фиг. 5), т.е. захвата микропроцессорного блока 1, записывает слова

информации по адресам блока 3, соот- памятью после запуска блока 7 форми- 15 ветствующим выделенному микропроцессорным блоком 1 буферу А

рования управляющих импульсов обмен данными между блоком 3 оперативной памяти и блоком 4 сопряжения с магистралью, блоком 5 коррекции ошибок и блоком 6 преобразования кодов осуществляется в режиме прямого доступа к блоку 3, что обеспечивает конвейерный принцип обработки данных. При этом операции обращения к доменной

, куда

считывается первая по счету страница в группе ДИМ. В это время микропроцессорный блок 1 вычисляет области 20 этого буфера, подлежащие передаче на магистраль 14, и программирует соответствующий канал контроллера 11, обслуживающий блок 4 сопряжения с магистралью 14. По завершении считыва

из ДИМ, строб-импульсы 89 задержанного чтения ЗЧТД и сигнал 87 Готовность передачи данных ДИМ.В процессе считывания данных из ДИМ блок 6 преобразования кодов формирует сигналы запроса прямого доступа на выходе 104, поступающие на контроллер 11 прямого доступа, и по получении от контроллера 11 сигналов подтверждения прямого доступа на входе 105 (см. фиг. 5), т.е. захвата микропроцессорного блока 1, записывает слова

информации по адресам блока 3, соот- ветствующим выделенному микропроцессорным блоком 1 буферу А

, куда

считывается первая по счету страница в группе ДИМ. В это время микропроцессорный блок 1 вычисляет области этого буфера, подлежащие передаче на магистраль 14, и программирует соответствующий канал контроллера 11, обслуживающий блок 4 сопряжения с магистралью 14. По завершении считыва

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Станция локальной сети | 1990 |

|

SU1824640A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам на цилиндрических магнитных доменах (ЦМД), и может быть использовано в составе систем внешней энергонезависимой памяти ЭВМ. Цель изобретения - повышение быстродействия и расширение области применения устройства за счет использования доменных микросборок с произвольным числом годных регистров и выполнения функций эмуляции запоминающих устройств на магнитных дисках. Запоминающее устройство на ЦМД содер - жит блок 1 адресации, блок 2 постоянной памяти, блок 3 оперативной памяти, блок 4 сопряжения с магистралью, блок 5 коррекции ошибок, блок 6 преобразования кодов, блок 7 формирования управляющих импульсов, регистр 8 управления, модулей 9 доменной памяти, контроллер 10 прерываний и контроллер 11 прямого доступа. Наличие указанных блоков позволяет наращивать объем памяти на ЦМД, повысить быстродействие устройства за счет параллельного включения доменных микросборок и расширить область применения устройства за счет использования в модулях доменной памяти мик- росборок с произвольным числом маскируемых регистров. 5 ил. (Л

памяти, формирования корректирующего 25 ния данной страницы Ш1М, т.е. работы

всех каналов контроллера 11, обслуживающих блок 6 преобразования кодов, микропроцессорный блок 1 программирует его на адрес другого буфера в

При выполнении операции чтения сек-30 блоке 3 оперативной памяти (Б) и .

запускает блок 5 коррекции ошибок, проверяющий правильность считанной

кода,обмена с магистралью и эмуляции магнитного диска совмещаются во времени .

с блока 3 страниць ДИМ. При успещном завершении работы последнего (отсутторов устройство работает следующим образом. Прежде всего микропроцессорный блок 1 программно вычисляет адреса модулей 9 доменной памяти и доменных интегральных микросборок (ДОМ) на 35 ствии ошибок в данных) микропроцес- них, которые записывает в регистр 8 сорньй блок 1, получив от контролле- управления наряду с кодом режима, со- ра 10 прерываний прерывание, соответ- ответствующим чтению информации из ствующее сигналу на выходе 74, запус- ДИМ, а также вычисляется номер и ко- кает блок 4 сопряжения с магистралью, личество страниц Д1 М, соответствующих 40 который также в режиме прямого дос- заданным дорожке и сектору диска, ко- тупа осуществляет передачу данных тоыре заносятся в блок 7 формирова- на магистраль. Поскольку служебная ния управляющих импульсов. Затем мик- информация, которая не подлежит пе- кропроцессорный блок 1 пpoгpaм иpyeт редаче на магистраль, может находить- каналы контроллера 1 1 прямого досту- 45 ся внутри страниц ДИМ, то по окончании передачи на магистраль массива

Л

данных, запрограммированного в кана

па, обслуживающие блок 6 преобразования кодов. Управляющий сигнал на

входе 103 режима чтения информации изле контроллера 11 прямого доступа, (см. фиг. 5) с выхода указанногослуживающем блок 4 сопряжения с магирегистра 8 запускает блок 7 формирова-50стралью, последний формирует сигнал

ния управляющих импульсов, которьйзапроса прерывания микропроцессорнообеспечивает генерацию сигналов управ-го блока 1 на выходе 27, который, обления ДИМ, на группе выходов 30, вслуживая указанное прерывание, при

частности сигнала репликации и сигма-необходимости вновь запускает процесс лов управления полем на выходе 86, 55 передачи следующей части массива дана также формирует сигналы синхрониза-ных из буфера. Одновременно с этими

ции на группе выходов 36, поступаю-процессами происходит считывание слещие на блок 6 преобразования кодов -дующей страницы из ДИМ в бустроб-импульсы 88 чтения данных (ЧТД)фер блока 3, по окончании которого

с блока 3 страниць ДИМ. При успещном завершении работы последнего (отсутствии ошибок в данных) микропроцес- сорньй блок 1, получив от контролле- ра 10 прерываний прерывание, соответ- ствующее сигналу на выходе 74, запус- кает блок 4 сопряжения с магистралью, который также в режиме прямого дос- тупа осуществляет передачу данных на магистраль. Поскольку служебная информация, которая не подлежит пе- редаче на магистраль, может находить- ся внутри страниц ДИМ, то по окончании передачи на магистраль массива

ствии ошибок в данных) микропроцес- сорньй блок 1, получив от контролле- ра 10 прерываний прерывание, соответ- ствующее сигналу на выходе 74, запус- кает блок 4 сопряжения с магистралью, который также в режиме прямого дос- тупа осуществляет передачу данных на магистраль. Поскольку служебная информация, которая не подлежит пе- редаче на магистраль, может находить- ся внутри страниц ДИМ, то по окончании передачи на магистраль массива

данных, запрограммированного в кана

первый буфер вновь-программируется н ввод информации из ДИМ.

Аналогично предлагаемое устройство реализует операцию записи секторо диска в ДИМ, когда совмещаются во вр мени считывание данных с магистрали, формирование корректирующего кода, эмуляция диска и запись в ДИМ поочередно для обоих буферов в блоке 3 оперативной памяти. Однако, поскольку длины сектора диска и страницы ДИМ не совпадают, физической записи в ДИМ первой и последней страницы данных предшествует считывание следующей страницы из ДИМ в другой блок 3 и замена соответствующей их части новой информацией, после чего микропроцессорный блок 1 записывает в регистр 8 управления код режима, соответствующий записи данных в ДИМ, запуская блок 7 формирования управляющих импульсов, которьш обеспечивает генерацию сигналов управления ДИМ - сигнала вывода доменов, сигналов генерации доменов, сигнала ввода доменов и сигналов управления полем на выходе 86 (см. фиг. 4), а также формирует сигналы, поступающие на блок 6 преобразования кодов. К этим сигналам относятся строб-импульсы чтения данных из блока 3, строб-импульсы задержанного чтения ЗЧТД и строб-импульсы генерации (совпадающие по фазе), а также сигнал на входе 87 Готовность передачи данных ДИМ.

В режиме записи информации с магистрали в порты устройства блок 4 сопряжения с магистралью (см. фиг. 2) работает следующим образом. При чтении состояния устройства со стороны ЭВМ селектор 37 адреса магистрали через элемент И 51 формирует сигнал 17 Ответ, а также отпирает выходы буферного регистра 40 с тремя состояниями, в который микропроцессорный блок 1 через адресный селектор 38 предварительно записывает байт состояния устройства.

При этом непрерывные считывания слова состояния со стороны магистрали никак не влияют на работу устройства, поскольку они производятся из регистра 40 без захвата внутренней .шины 12, при этом информация заносится в указанный регистр микропроцессорным блоком 1. Использование указанного регистра предотвращает за

J

хват внутренней шины 12. и связанное с этим замедление работы устройства при непрерывном считывании слова состояния запоминающего устройства со стороны ЭВМ.

При состоянии устройства, соответствующем завершению операции, обращение ЭВМ по магистрали к другим логи- -10 ческим регистрам устройства (чтение уточненного слова состояния, запись команды и др.) вызывает появление на выходе адресного селектора 37 сигнала запроса прямого доступа внут- 15 ренней шины 12, соответствующего чтению либо записи слова в блок 3 устройства. Контроллер 11 осуществляет захват внутренней шины 12, при этом на ней устанавливается адрес, стар- 0 тая часть которого запрограммирована в контроллере 11 и соответствует заданной области адресов блока 3 оперативной памяти устройства, а мпад- шая часть определяется как младшими 5 битами адреса на магистрали, соответствующими номеру порта в устройстве, так и строб-импульсом 18 (чтение либо запись в порт) , .что обеспечивает логическое разделение регистров чте- 0 ния и записи. С этой целью сигналы с инверсного выхода вентиля 49 бло- кируют формирователь 41 и отпирают формирователь 44, на входы которого через формирователь 42 поступают сиг- jg налы адреса 15 с магистрали. Сигналы подтверзздения запроса прямого доступа к памяти (ИДИ) 53 и 54 через вентили 49 и 51 формируют также сигнал 17 Ответ на магистрали 14, при этом 0 данные передаются через двунаправленный формирователь 43.

Селектор 37 адреса магистрали используется также для формирования сигналов прерывания микропроцессорно- 5 го блока 1, которые-поступают на контроллер 10 прерываний. В частности, запись команды с магистрали 14 сигналом на выходе 27 вызывает подпрограмму прерывания, обеспечивающую после- 0 дующее выполнение заданной операции.

Процесс обмена массивами инициируется микропроцессорным блоком 1 путем вьшолнения операции записи в порт, соответствующий появлению на выходе g селектора 38 импульса, устанавливающего триггер 39 в состояния 1. Указанный триггер выставляет сигнал запроса ДПД на выходе 57 на контроллер 11, а также инициирует захват магистрали арбитром 46ч Сигнал подтверждения захвата магистрали 14 на выходе арбитра 46 отпирает формирователь 43 сигналов данных-16, формирователь 45 управляю1цих сигналов 19 чтения- записи памяти на магистрали 14 из соответствующих сигналов на группе входов-выходов 23 внутренней шины 12 и переключает на передачу шинный формирователь 42, через который на магистраль 14 передается текущий код адреса 15 из счетчика 47. Указанный код предварительно заносится в счетчик 47 микропроцессорным блоком 1 в соответствии с адресом массива данных на магистрали. Вентиль 48 управляет сигналом 34 готовности контроллера 11 ПДП, синхронизируя временную диаграмму его работы с магистралью 14. Таким образом, контроллер 11 ПДП через буферньш формирователь 41 формирует сигналы адреса на внутренней шине 12, через буферный формировател 45 - управляюиц1е сигналы 19 чтения - записи в порты на магистрали 14 и непосредственно - сигналы чтения-записи в порты на внутренней- шине 12, после чего контроллер 11 ПДП ожидает сигнала 17 Ответ с магистрали 14, означающего завершение передачи слова, и завершает цикл ПДП на слово

Задний фронт сигнала на входе 52 подтверждения прямого доступа от контроллера 11 ПДП увеличивает содержимое счетчика 47 на 1, обеспечивая переход к следующему адресу памяти на магистрали 14. Сигнал на входе 33 завершения цикла прямого доступа совместно с сигналом подтверждения прямого доступа соответствующего канала контроллера 11 ПДП сбрасывает триггер 39, снимая запросы на захват как магистрали 14, так и внутренней шины 12. Кроме того, выходной сигнал триггера 39 поступает на контроллер 10 прерываний, инициируя выполнение соответствующей подпрограммы завершения микропроцессорным блоком 1 .

Работа блока 5 коррекции ошибок (см. фиг. 3) осуществляется в различных режимах, которые задаются регистром 8 управления - в режиме формирования корректирующего кода, проверки данных и исправления данных. Для пре отвращения потери быстродействия при исправлении ошибок блок 5 использует предустановку укороченного кода

Файра на длину, соответствующую текущей длине страницы данных выбранной группы ДИМ.

В режиме формирования корректирующего кода (при вьшолнении операции записи в ДИМ) микропроцессорный блок 1 вьшолняет команды записи в порты внутренней шины 12, соответствующие

выдаче дешифратором 68 импульса сброса, который устанавливает в исходное состояние регистр 66 кода, и импульса начала коррекции, который сбрасывает триггер 64 и устанавливает триг-

геры 61-63 в состояние 1, вызывающее запрос ПДП на выходе 70. По сигналу на входе 71 подтверждения ПДП сбрасываются триггеры 61 и 63, в регистр 58 заносится очередное слово

данных, а также запускается элемент 59 задержки, на первом выходе которого формируется пачка синхроимпульсов, сдвигающих информационное слово, записанное в регистре 66. Количество

синхроимпульсов при этом равно разрядности слова данных на внутренней шине 12. Код Файра формируется с помощью ППМ 65 в соответствии с запрограммированным в нем полиномом деления, соответствуюш м максимальной длине страницы и исправляющей способности кода. Сигнал на втором выходе элемента 59 задержки, соответствующий окончанию преобразования

5

слова, вновь устанавливает триггер

61 в состояние 1, и описанный процесс повторяется до записи в регистр

58последнего информационного слова, когда сигнал на входе 33 завершения

Q прямого доступа контроллера 11 ПДП сбрасывает триггер 63, а следующий . импульс на выходе переноса элемента

59задержки устанавливает в единичное состояние один из триггеров 62

5 либо 64, форг-шрующие сигналы запроса на выходах 73 или 74 прерывания микропроцессорного блока 1, поступающий на контроллер 10 прерьшаний. Полученное значение кода в регистре 66 заQ тем программно считывается микропроцессорным блоком 1 по сигналам дан- : ных 22 внутренней шины 12 через мультиплексор 67 и записывается в блок -3 по адресам, соответствующим gg концу данной страницы данньк, образуя требуемый блочный код.

Режим проверки данных (при чтении информации из ДИМ) отличается от описанного лишь тем, что данные в регистре кода 66 формируются с учетом значения укорачивающего полинома, записанного в буферном регистре 60 в соответствии с текущей длиной страницы выбранной группы ДИМ, а последний импульс переноса на выходе элемента 59 задержки фиксирует в триггерах 62 и 64 состояние, соответствующее результату преобразования. Для этой цели на их информационные входы поступает сигнал наличия нулевого кода в регистре 66, который формируется на втором выходе ПЛМ 65 из выходов всех разрядов регистра 66, и соответствует правильной информации, считанной из ДИМ в блок 3 оперативной памяти.

В режиме исправления данных микропроцессорный блок 1 сигналом на входе 72 исправления данных, поступающим с соответствующего выхода регистра 8 управления, блокирует умножение кода в регистре 66 и разрешает формирование на третьем выходе ПЛМ 65, сигнала, который при равенстве нулю младших 12 бит регистра 66 сбрасывает триггер 63, которьм, в свою очередь, блокирует элемент 59 задержки, фиксирует текущее состояние регистра кода 66 и переключает триггер 62 сигнала запроса прерывания (выход 73) в состояние 1. Регистр 58 используется в качестве позиционного Ьчетчика бит, поскольку текущее состояние элемента 59 задержки недоступно с внутренней шины 12. Для получения этой информации в каждом цикле ПДП содержимое регистра 58 обнуляется, а при каждом сдвиге в регистр 66 заносится 1 с входа последовательных данных. Номер слова, содержащего исправимый пакет ошибок, оределяется значением счетчика в соответствующем канале контроллера 11 ПДП путем считывания микропроцессорным блоком 1 внутренних регистров контроллера 11 ПДП в программе обработки прерывания от контроллера 10 прерываний,- соответствуюш15х сигналу запроса на выходе 74, Старшие биты в регистре 66 при этом дают синдром ошибки, используя который микропроцессорный блок 1 программно исправляет данные, находящиеся по вычислен- регистров. При записи в ДИМ необходи- ному адресу в блоке 3, и при необхо- мо 4 субцикла - вывода, записи, за- димости перезаписывает исправленную держки вывода и вывода. Например, страницу данных обратно.в ДИМ. В случае неисправимой ошибки в данных

для ДИМ типа К1602РЦ2 длительности субциклов чтения составляют 86 и

0

0

5

работа блока 5 завершается так же, | как в режиме проверки данных.

Блок 7 формирования управляющих импульсов (см. фиг. 4) работает следующим образом. В исходном состоянии блок 75 формирования.поля находится в состоянии 3, соответствующем фазе магнитного поля 270, а триггеры 84 и 85 сброшены. Для запуска блока 7 микропроцессорный блок 1 через внутреннюю шину 12 устройства в регистр 8 управления записывает код, соответствующий операции с ДИМ 5 чтение доменов либо чтение карты дефектных регистров ДИМ, который поступает на управляющий вход блока 7, Предварительно микропроцессорный блок 1 по внутренней шине 12. заносит в программируемый счетчик 85 код, соответствующий сдвигу требуемой страницы ДИМ относительно ее текущего положения.

Управляющий сигнал на втором выходе регистра В управления запускает блок 75 формирования вращающегося поля, на первом выходе 86 которого формируются сигналы управления полем продвижения, а на втором - импульсы переноса с частотой поля, которые подсчитываются в программируемом счет- чике 85. Выходной сигнал последнего при наличии требуемой страницы ДИМ устанавливает в 1 триггер 85 страg ничной синхронизации, который, в свою очередь, разрешает работу счетчика 76, т.е. формирование субциклов обращения к ДИМ. Задержка формирования импульса переноса на выходе этого счетчика, т.е. число периодов вращающего поля в каждом субцикле опреде- ряется кодом на вькоде блока 83 памяти субциклов, на адресньй вход которого поступают коды, соответстg вующие режиму работы и номеру субцикла, т.е. счетчик 79 номера субцикла задает адрес числа .в блоке 83, определяющего длительность следующего субцикла.

В режиме чтения информации из ДИМ в соответствии с временной диаграммой ее работы необходимы 2 субцикла - репликации и чтения доменов. То же относится и к чтению карты дефектных

0

0

0

регистров. При записи в ДИМ необход мо 4 субцикла - вывода, записи, за- держки вывода и вывода. Например,

для ДИМ типа К1602РЦ2 длительности субциклов чтения составляют 86 и

282 периода вращаюп{егося поля, а записи - 210, 282, 19 и 2 периода поля Счетчик 77 с переменным коэффициентом деления, счетчик 80 по модулю 4 и блок 82 памяти задержек образуют формирователь парных задержанных импульсов, обеспечивающий формирование пары задержанных импульсов на выходах распределителя 81. При этом запуск указанного формирова.теля осуществляется в субцикле ввода-вьгоода в каждом периоде вращающего поля, а в остальных - в начале каждого суб- цикла, что обеспечивается комбинационной логикой на входе триггера 84, Счетчик 80 на 4 состояния задает адресный код, соответствующий задержке и длительности обоих импульсов, который пост упает на адресный вход блока 82 наряду с кодами режима и номера субцикпа. При этом младший разряд счетчика также стробирует распределитель 81 импульсов, на выходе которого формируются задержанные относительно нулевой фазы поля на требуемые для ДИМ значения импульсы ввода, репликации, выводы, генерации, конца операции, а также основной н задержанный строб-импульсы на выхо- дах 88 и 89, поступающие на блок 4 преобразования кодов. При этом в ре- , жиме записи данных строб-импульсы задержанного чтения и генерации совпадают во времени. Импульс конца операции, формируемый в последнем субцикле, сбрасывает триггер 85 страничной синхронизации, но сигналы управления полем продвижения продолжают формироваться блоком 75 формирования поля до снятия кода операции в регистре 8 управления.

При многостраничном обмене триггер 85 в дальнейшем периодически переключается в состояние 1 сигналами запуска от программируемого счетчика 78, соответствующими следующим логическим страницам ДИМ (например, для ДИМ с емкостью 256 Кбит - через каждые 512 периодов поля). Запись в регистр 8 управления кода, соответствующего снятию операции, приводит к корректному останову (выключению) поля блоком 75 формирования поля. Выключение поля во время вьшолнения операции мож«о предотвратить программно путем считывания микропроцессорным блоком 1 состояния триггера 85 страничной синхронизации.

Выполнение операции чтения карты дефектных регистров отличается от чтения данных из ДИМ тем, что блокируются управляющие импульсы функциональных узлов и катушек ДИМ на выходе распределителя 81. Дпя этой цели используется управляющий сигнал на входе 107 (см. фиг. 5) режима чтения 0 карты дефектных регистров с выхода регистра 8 управления, который поступает на адресные входы блока 83 памяти субциклов и входы распределителя 81, а также на блок 6 преобразования 15 кодов, коммутируя на его вход синхронизации строб-импульсы чтения данных, а на вход данных - сигналы карты дефектных регистров ДИМ с группы входов 31 (см. фиг. 1).

0 При чтении информации из ДИМ сигнал режима чтения на входе 103 (см. фиг. 5) блокирует регистр 91 и запрещает параллельную запись данных в регистр 90. Сигнал начала страницы 5 на входе 106 до начала физического считывания из ДИМ заносит в счетчик 93 число М-1, соответствующее М .битам в передаваемом слове, и устанавливает в активное состояние триггер 0 95 запроса прямого доступа, формирующий сигнал запроса прямого доступа на выходе 104. Контроллер 11 ПДП захватьшает внутреннюю шину 12 устройства и формирует строб-импульс g чтения порта и сигнал подтверждения прямого доступа, причем последний сбрасывает триггер 95 запроса по входу 105. Синхроимпульсы чтения данных в фазе, соответствукщей прохож- 0 дению доменов через детекторы ДИМ, через вентиль.98, стробируемый данными карты дефектных регистров выбранной ДИМ, поступают на счетный вход счетчика 93 и вход синхронизации 5 регистра 90, записывая в него очередной действительньш (незамаскированный) бит данных из ДИМ, соответствующий сигналу данных на группе входов- выходов 32. Запись последнего в ело 0 ве бита данных вызывает появление на выходе счетчика 93 бит импульса переноса, который устанавливает в 1 триггер 94 и отпирает входы буферного регистра 92. Этот же сигнал через g |вентиль 97 устанавливает триггер 95 запроса ПДП, перезаписьшает в счетчик 93 код числа 8 и отпирает выходы регистра 90. Длительность этого сиг нала определяется фазой строб-импуль-

са задержанного чтения, который сбрасывает триггер 94, при этом в регистре 92 фиксируется считанное слово данных. Последний переписывается в блок 3 устройства контроллером 11 ПДП по мере освобождения внутренней шины 12. При этом сигналами считывания и лодтверждения прямого доступа, поступающими на вентиль 96, выходы регистра 92 отпираются на внутреннюю шину 12 устройства.

Режим чтения карты дефектных регистров отличается от чтения данных тем, что по сигналу чтения карты де- фектных регистров на входе 107 с выхода регистра 8 управления на вход синхронизации регистра 90 сдвига с выхода мультиплексора 101 поступают, все без исключения строб-импульсы ЧТД, а на его информационный вход - сигнал карты дефектных регистров ДИМ что позволяет записать в блок 3 устройства информацию о дефектных регистрах ДИМ, а также вспомогательную информацию, делая ее доступной микропроцессорному блоку 1.

В режиме записи данных, когда сигнал режима чтения на входе 103 неактивен, отпираются выходы регистра 91 при этом происходит запись слова данных в регистр 91 и кода числ а О в счетчик 93. При этом первый же импульс на входе счетчика 93 вызовет установку триггеров 94 и 95 в 1, что вызовет перезапись очередного слова из буферного регистра 91 в регистр 90 сдвига, а также запрос ПДП на следующее слово, причем.этот запрос будет удовлетворен заведомо после окончания записи в регистр 90. Далее в счетчик 93 заносится код числа 7 аналогично чтению из ДИМ и процесс повторяется. Остальные биты слова выталкиваются из регистра 90 в режиме сдвига, что обеспечивает элемент ИЛИ 98.

Все каналы блока 6 преобразования кодов работают независимо, формируя сигналы запроса прямого доступа по мере накопления действительных (незамаскированных) бит информации, при этом конфликты между каналами при одновременных запросах разрешаются контроллером 11 прямого доступа, который определяет очередность обслуживания.

Задержка между импульсами ЧТД и ЗЧТД ограничена сверху минимальным

временем удовлетворения ПДП (обычко f не менее 2 мкс), что гарантирует отсутствие ошибок передачи. Максимальная задержка обслуживания ПДП для данного устройства определяется временем передачи байта (слова) из ДИМ и для частоты 100 кГц составляет 80 МКС, поэтому каналы контроллера

11 ПДП, обслуживающие запросы от блока 6 преобразования кодов, имеют высший приоритет по захвату внутренней шины 12 устройства.

Блок 6 преобразования кодов может

быть реализован также на базе серийных БИС последовательного интерфейса, удовлетворяющих требованиям по быстродействию и имеющих интерфейс с внутренней шиной 12.

Таким образом, испол ьзование изобретения позволяет повысить быстродействие запоминающего устройства на ЦМД за счет нарашлвания числа параллельно работающих доменных интеграль-

ных микросборок. При этом в модулях доменной памяти могут использоваться микросборки с различным числом дефектных регистров. Устройство позволяет выполнять функции эмуляции запоминающих устройств на магнитных дисках.

Формула изобретения

Запоминающее устройство на цилиндрических магнитных доменах, содержащее группу модулей доменной памяти, блок формирования управляющих импульсов и регистр управления, выход управления режимом которого подключен к группе входов управления режимом модулей доменной памяти группы, группа управляющих входов которых соединена с группой управляющих выходов

блока формирования управляющих импульсов, а адресные входы модулей доменной памяти группы подключены к адресному выходу регистра управления, отличающееся тем,

что, с целью повьщ|ения быстродействия и расширения области применения числом годных регистров и вьшолнения функций эмуляции запоминающих устройств на магнитных дисках, оно содержит блок адресации, блок постоянной памяти, блок оперативной памяти, контроллер прерываний, контроллер прямого доступа, блок преобразования кодов, блок коррекции ошибок и блок

сопряжения с магистралью, причем группа входов-выходов данных блока адресации подключена к группам входов- выходов данньк блока оперативной памяти, блока сопряжения с магистралью, блока коррекции ошибок, контроллера прерываний и контроллера прямого доступа, -а также к группе числовых выхо- ;дов блока постоянной памяти, группам информационных входов блока формирования управляющих импульсов и ре гистра управления, группа входов-выходов данных блока оперативной памяти соединена с группами входов-выхо- 45 жения с магистралью и блока коррек- дов данных блока сопряжения с магистралью, блока преобразования кодов и блока коррекции ошибок, группа адресных выходов блока сопряжения с мации ошибок соединены соответственно первым и вторым входами запроса прерываний контроллера прерываний, вход-выход запроса и подтверждения

гистрапью подключена к группам адрес- 20 прерьгоаний которого подключен к вхоных входов блока постоянной памяти, блока оперативной памяти, блока коррекции ошибок, блока преобразования кодов, блока формирования управляющих импульсов, контроллера прерываний и регистра управления, группа управляющих выходов блока адресации соединена с группой управляющих входов-выходов контроллера прямого доступа, а также с управляющими входами блока постоянной памяти, блока оперативной, памяти, блока сопряжения с магистралью, блока коррекции ошибок, блока преобразования кодов, контроллера прерьшаний, блока формирова- с ния управляющих импульсов и регистра управления, адресный выход блока адресации подключен к адресному входу блока сопряжения с магистралью и адресному входу-выходу контроллера прямого доступа, первые, вторые и третьи входы-выходы запроса и подду-выходу запроса и подтверждения прерываний блока адресации,, выход управления режимом регистра управления соединен с входами управления

25 режимом блока коррекции ошибок и блока преобразования кодов, группа входов синхронизации которого подключена к группе выходов синхронизации блока формирования управляющих им30 пульсов, входов-выходов данных считывания-записи и группа входов карты годности блока преобразования кодов соединены соответственно с Группой входов-выходов данных считывания-записи и группой выходов карты годности группы модулей доменной памяти, грздтпа магистральных входов- выходов блока сопряжения с магистралью является группой входов-выхо4Q дов данных, адреса и сигналов управления ус тр ойс ТВ а.

тверждения прямого доступа которого | соединены с входами-выходами запроса и подтверждения прямого доступа соответственно блока сопряжения с магистралью, блока коррекции ошибок и блока преобразования кодов, вход завершения прямого доступа и выход управления готовностью блока сопряжения с магистралью подключены соответственно к выходу завершения прямого доступа и входу управления готовностью контроллера прямого доступа, выходы запроса прерываний блока сопряжения с магистралью и блока коррек-

ции ошибок соединены соответственно с первым и вторым входами запроса прерываний контроллера прерываний, вход-выход запроса и подтверждения

ду-выходу запроса и подтверждения прерываний блока адресации,, выход управления режимом регистра управления соединен с входами управления

режимом блока коррекции ошибок и блока преобразования кодов, группа входов синхронизации которого подключена к группе выходов синхронизации блока формирования управляющих импульсов, входов-выходов данных считывания-записи и группа входов карты годности блока преобразования кодов соединены соответственно с Группой входов-выходов данных считывания-записи и группой выходов карты годности группы модулей доменной памяти, грздтпа магистральных входов- выходов блока сопряжения с магистралью является группой входов-выходов данных, адреса и сигналов управления ус тр ойс ТВ а.

Фиг. 2.

| Computer Design, 1978, № 2, p | |||

| Способ получения суррогата олифы | 1922 |

|

SU164A1 |

| Катодное реле | 1918 |

|

SU159A1 |

Авторы

Даты

1989-01-15—Публикация

1987-01-21—Подача