Изобретение относится к области преобразования и кодирования информации.

Известны преобразователи интервалов времени в цифровой код, содержащие формирующие триггеры, схему сборки, регистры памяти разрядов и линию задержки с отводами, причем выходы линий задержки подключены ко входам схемы сборки, выход схемы сборки соединен с первым входом формирующего триггера, второй вход которого соединен с последним выходом линии задержки, входы регистров памяти разрядов подключены к выходам линий задержки.

В известных преобразователях количество оборудования зависит от числа разрядов.

Предложенный преобразователь пнтервалов времени в цифровой код отличается тем, что, с целью упрощения, он содержит схемы совпадений, расширитель импульсов, сдвигающий регистр, причем вход линии задержки соединен со входом сдвигающего регистра и с выходом схемы совпадений, вход схемы совпадений подключен к выходу формирующего триггера, один вход которого соединен с клеммой «сброс, а другой со входом линии задержки, разрешающие входы регистров памяти разрядов соединены с первыми входами схем совпадения разрядов, выходы схемы совпадений разрядов соединены с выходом формирующего триггера схемы сборки, вторые

входы схем совпадений разрядов соединены с выходами сдвигающего регистра, а вход формирующего триггера схемы сборки соединен со входом расщирителя импульсов, вы.ход которого подключен к первому входу схемы совпадений, второй вход схемы совпадений соединен с последним выходом сдвигающего регистра, выход схемы совпадений подключен ко входу линии задержки. Это упрощает преобразователь, так как количество оборудования с ростом числа разрядов увеличивается незначительно.

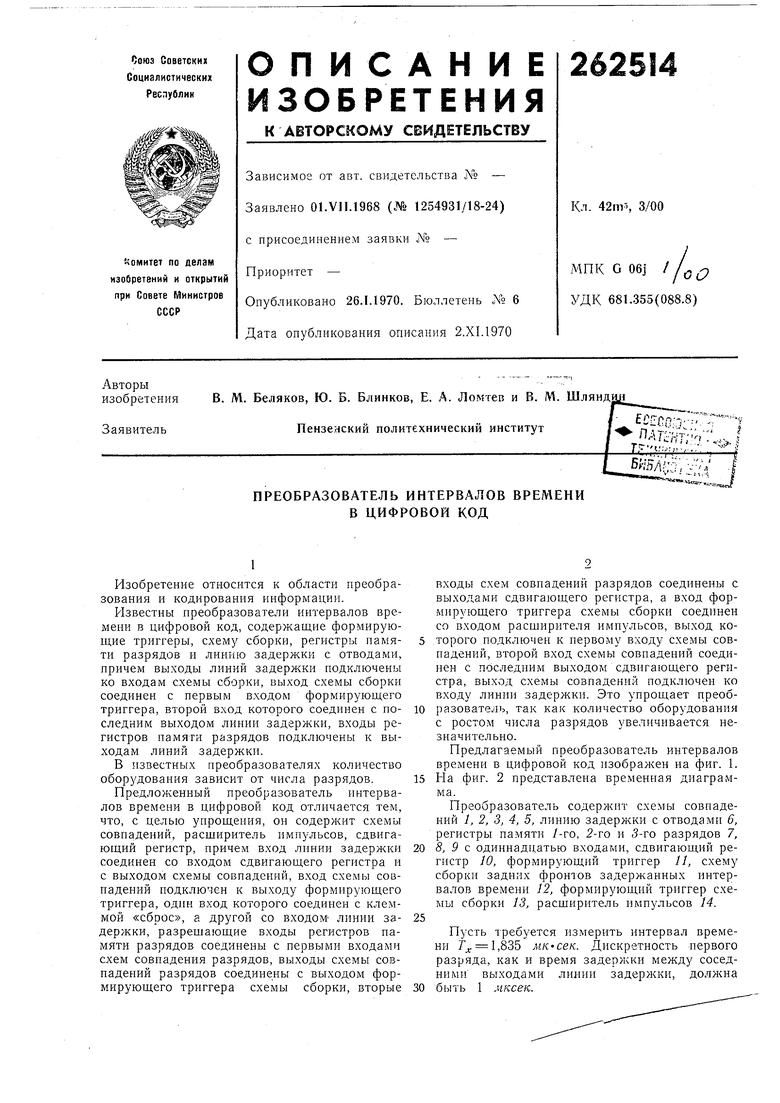

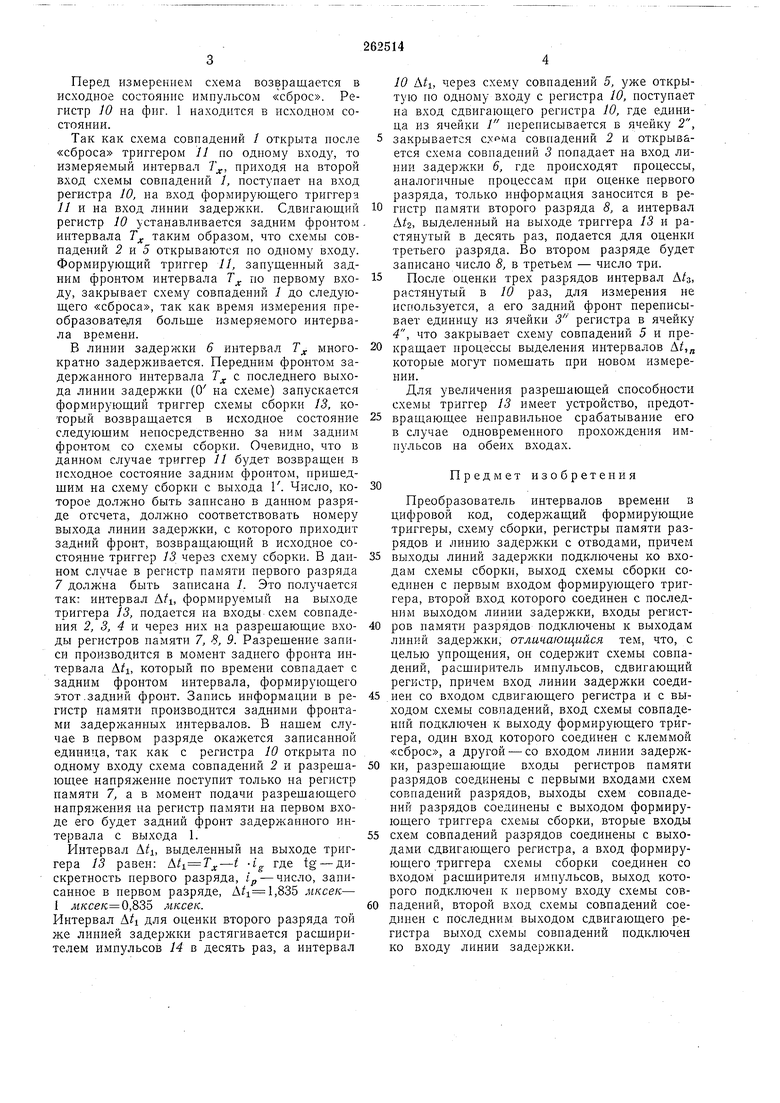

Предлагаемый преобразователь интервалов времени в цифровой код изображен на фиг. 1.

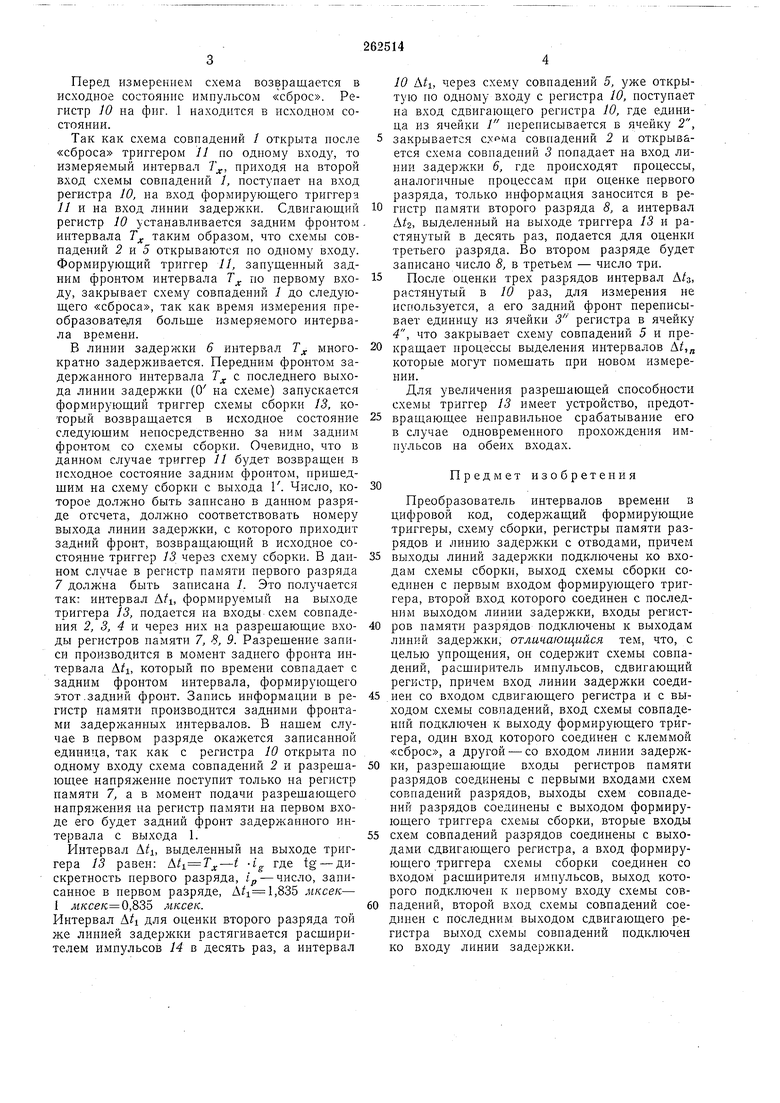

На фиг. 2 представлена временная диаграмма.

Преобразователь содержит схемы совпадений 1, 2, 3, 4, 5, линию задержки с отводами 6, регистры памяти /-го, 2-го и .5-го разрядов 7,

8, 9 с. одиннадцатью входами, сдвигающий регистр 10, формирующий триггер //, схему сборки задних фронтов задержанных интервалов времени 12, формирующий триггер схемы сборки 13, расщирнтель импульсов 14.

Пусть требуется измерить интервал времени 7 1,835 мк-сек. Дискретность первого разряда, как и время задержки между соседними выходами линии задержки, должна

Перед измерением схема возвращается в исходное состояние имнульсом «сброс. Регистр 10 на фиг. 1 находится в исходном состоянии.

Так как схема совпадений / открыта после «сброса триггером 11 по одному входу, то измеряемый интервал 7, приходя на второй вход схемы совпадений 1, поступает на вход регистра 10, на вход формирующего триггера // и на вход линии задержки. Сдвигающий регистр 10 устанавливается задним фронтом интервала Т таким образом, что схемы совпадений 2 и 5 открываются по одному входу. Формирующий триггер //, запущенный задним фронтом интервала Т, но первому входу, закрывает схему совпадений 1 до следующего «сброса, так как время измерения преобразоватешя больще измеряемого интервала времени.

В линии задержки 6 интервал многократно задерживается. Передним фронтом задержанного интервала Т с последнего выхода линии задержки (О на схеме) запускается формирующий триггер схемы сборки 13, который возвращается в исходное состояние следующим непосредственно за ним задним фронтом со схемы сборки. Очевидно, что в данном случае триггер )/ будет возвращен в исходное состояние задним фронтом, нришедщим на схему сборки с выхода Г. Число, которое должно быть записано в данном разряде отсчета, должно соответствовать номеру выхода линии задержки, с которого приходит задний фронт, возвращающий в исходное состояние триггер 13 через схему сборки. В данном случае в регистр памяти первого разряда 7 должна быть записана 1. Это получается так; интервал A/i, формируемый на выходе триггера 13, подается на входы схем совпадеиия 2, 3, 4 vi через них на разрещающие входы регистров памяти 7, 8, 9. Разрешение записи производится в заднего фронта интервала А/1, который по времени совпадает с задним фронтом интервала, формирующего этот.задний фронт. Запись информации в регистр памяти производится задними фронтами задержанных интервалов. В нашем случае в первом разряде окажется записанной единица, так как с регистра 10 открыта по одному входу схема совпадений 2 и разрещающее напряжение поступит только на регистр памяти 7, а в момент подачи разрещающего напряжения на регистр памяти на первом входе его будет задний фронт задержанного интервала с выхода 1.

Р1нтервал , выделенный на выходе триггера 13 равен: -i где tg - дискретность первого разряда, / число, записанное в первом разряде, A/i 1,835 мксек- 1 ./ик;се/с 0,835 мксек.

Интервал Aii для оценки второго разряда той же линией задержки растягивается расширителем импульсов 14 в десять раз, а интервал

10 , через схему совпадений 5, уже открытую ио одному входу с регистра 10, ностунает на вход сдвигающего регистра 10, где единица из ячейки / переписывается в ячейку 2, 5 закрывается совпадений 2 и открывается схема совпадений 3 попадает на вход линии задержки 6, где происходят процессы, аналогичиые процессам при оценке первого разряда, только информация заносится в регистр памяти второго разряда 5, а интервал , выделенный на выходе триггера 13 и растянутый в десять раз, подается для оценки третьего разряда. Во втором разряде будет записано число 8, в третьем - число три.

5 После оценки трех разрядов интервал А/з, растянутый в 10 раз, для измерения не используется, а его задний фронт переписывает единицу из ячейки 3 регистра в ячейку 4, что закрывает схему совпадений 5 и прекращает процессы выделения интервалов А/,„ которые могут помещать при новом измерении.

Для увеличения разрешающей способности схемы триггер 13 имеет устройство, предотвращающее неправильное срабатывание его в случае одновременного прохождения имнульсов на обеих входах.

Предмет изобретения

Преобразователь интервалов времени в цифровой код, содержащий формирующие триггеры, схему сборки, регистры памяти разрядов и линию задержки с отводами, причем

выходы линий задержки подключены ко входам схемы сборки, выход схемы сборки соединен с иервым входом формирующего триггера, второй вход которого соединен с последним выходом линии задержки, входы регистров памяти разрядов подключены к выходам линий задержки, отличающийся тем, что, с целью упрощения, он содержит схемы совпадений, расширитель импульсов, сдвигающий регистр, причем вход линии задержки соединей со входом сдвигающего регистра и с выходом схемы совпадений, вход схемы совпадений подключен к выходу формирующего триггера, один вход которого соединен с клеммой «сброс, а другой - со входом линии задержки, разрещающие входы регистров памяти разрядов соединены с первыми входами схем совпадений разрядов, выходы схем совпадений разрядов соедииены с выходом формирующего триггера схемы сборки, вторые входы

схем совпадений разрядов соединены с выходами сдвигающего регистра, а вход формирующего триггера схемы сборки соединен со входом расщнрителя импульсов, выход которого подключеп к первому входу схемы совпадений, второй вход схемы совпадений соединен с последним выходом сдвигающего регистра выход схемы совнадений подключен ко входу линии задержки.

аНЕЕЕЕЕИх

CSpoc

rSh

r 2 3 4/

EH

ФигЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛОВ ВРЕМЕНИ В ЦИФРОВОЙ КОД | 1970 |

|

SU271131A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОРОТКИХ ИНТЕРВАЛОВ ВРЕМЕНИ В ЦИФРОВОЙ КОД | 1969 |

|

SU257883A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛОВ ВРЕМЕНИ В ЦИФРОВОЙ КОД | 1973 |

|

SU387520A1 |

| Преобразователь интервалов времени в цифровой код | 1974 |

|

SU519706A1 |

| Устройство для анализа параметров графа | 1988 |

|

SU1681312A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2020766C1 |

| Устройство для измерения повторяющихся интервалов времени | 1986 |

|

SU1403013A1 |

| Устройство для ввода информации из канала связи | 1989 |

|

SU1684794A1 |

,

ГГг

ш:

rrrs:

i г f- 6 8 П 2 1 S д го 22 2V 21 28 ,« J2 3V 36 38

.й

-4- , I I I 1

I I . I I

1-4

П1 I

Даты

1970-01-01—Публикация