Предложенная логическая схема «И-НЕ/И относится к динамическим элементам вычислительной техннки и предназначена для использования в качестве универсального логического элемента В цифровых вычислительных устройствах.

Логические схемы «И-НЕ/И динамического ти1па, содерж ащие входные диодные схемы «И И транзисторы, известны. Недостатком их является наличие индукти1Бностей, трансформаторов; сложность схемы либо зависимость работы от постоянной времени накопления и рассасывания заряда в базе транзистора.

Предложенная логическая схема, состоящая из Двух динамических элементов с взаимяо инверсными выходами, отличается тем, что в каждом элементе база инвертирующего транЗистора соединена через разделительный конденсатор с .выходом диодной схемы «И и через диод цепи разряда конденсатора - с источником смещения, лричем БЫХОД каждого из динамических элементов соединен с одним из входов (второто элемента. Это нозволяет .повысить быстрод.ействие и увеличить помехоустойчиВОсть схемы.

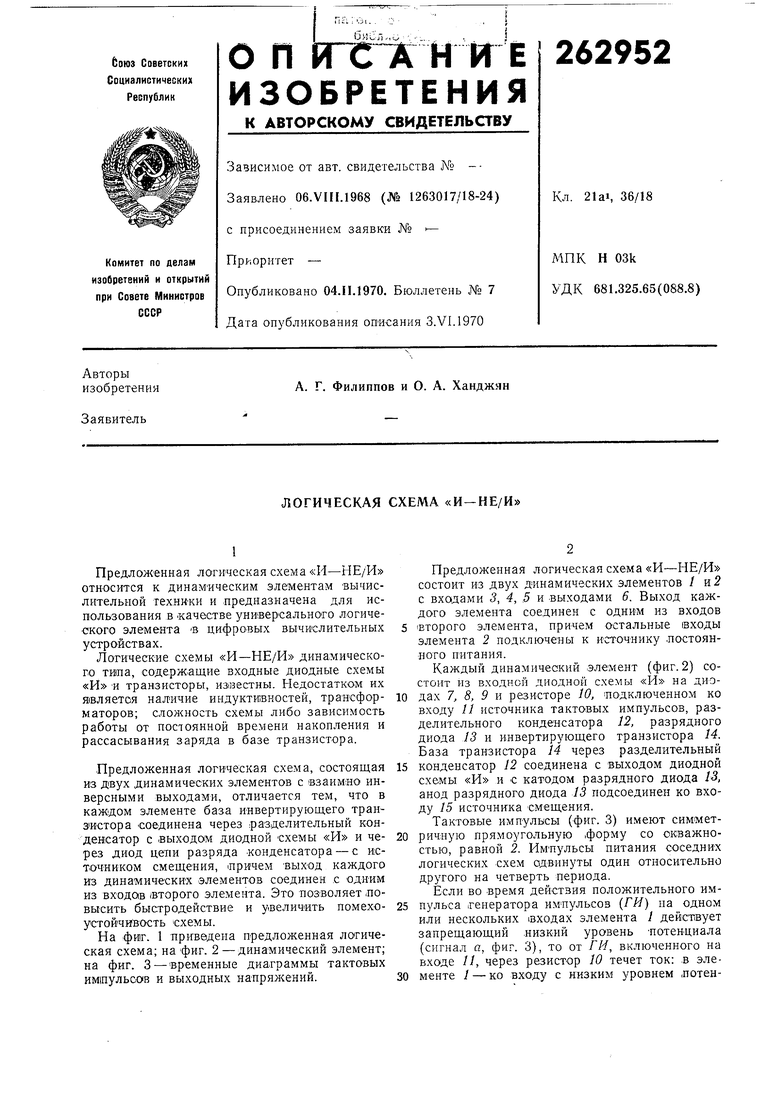

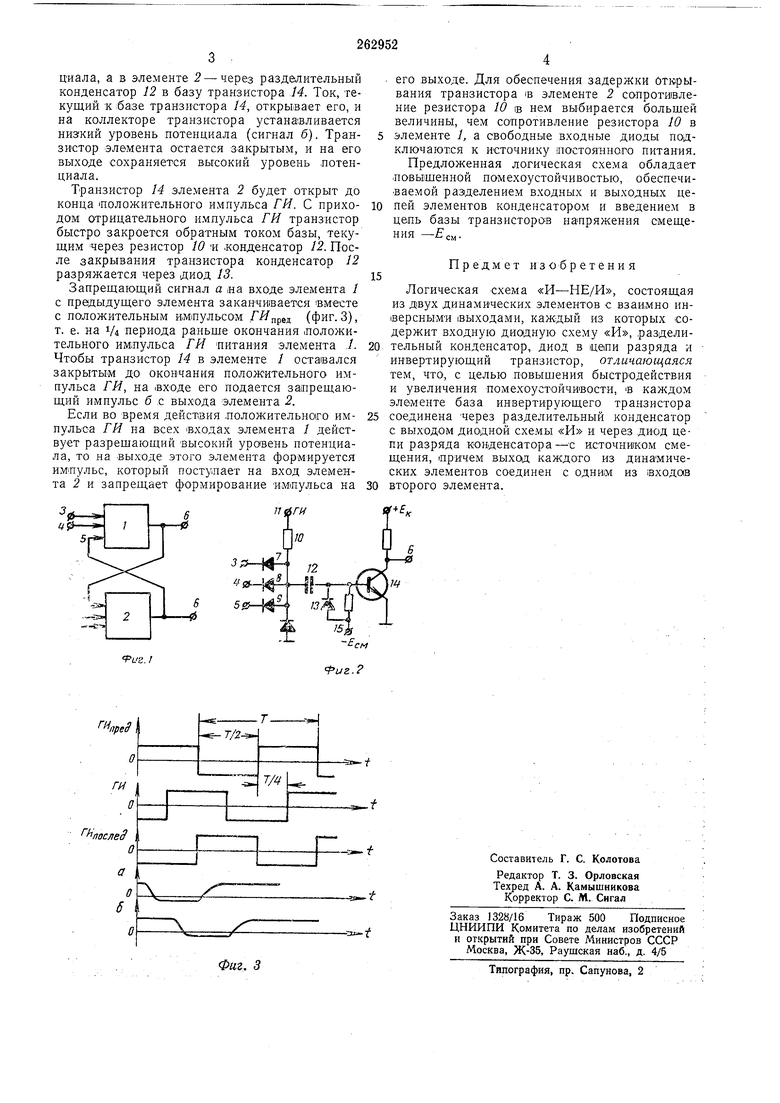

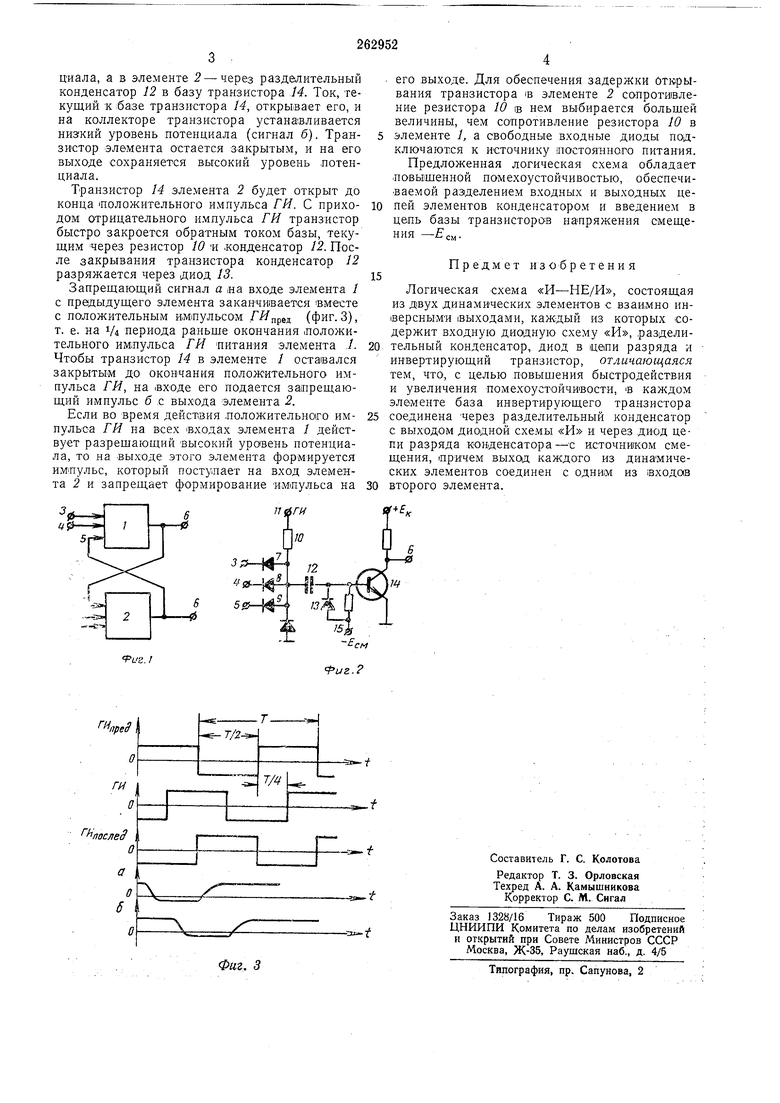

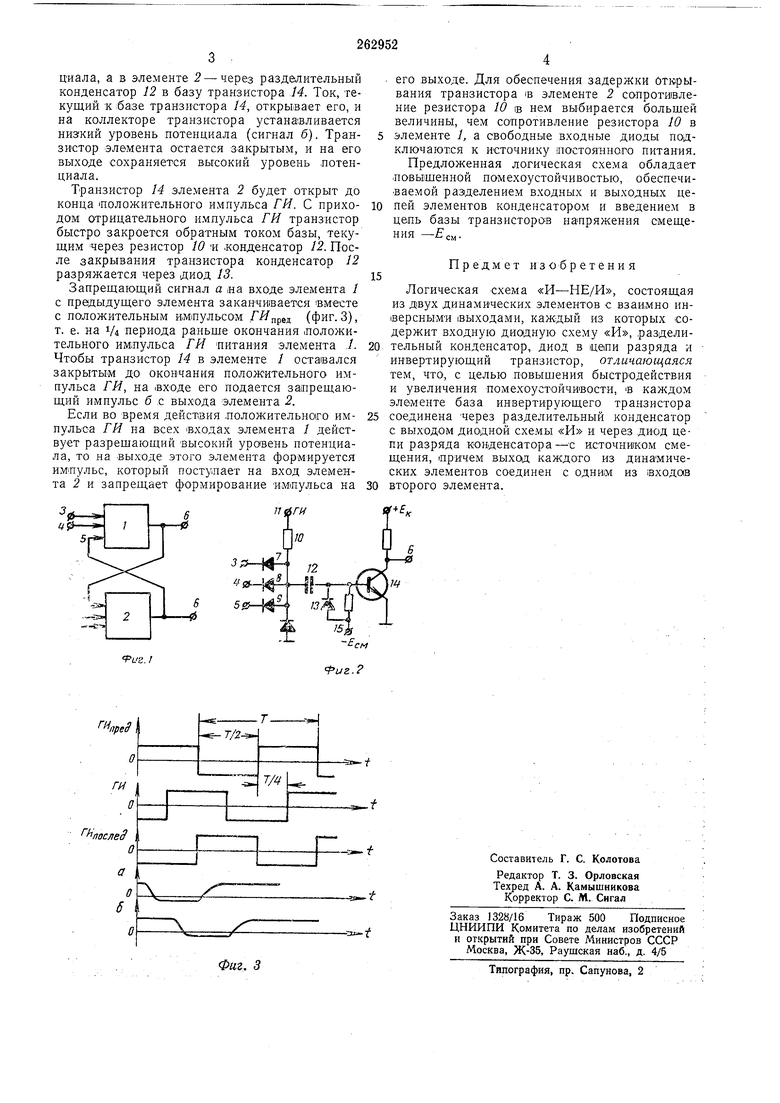

На фи1г. 1 приведена предложенная логическая схема; на фиг. 2 - динамический элемент; на фиг. 3 - временные диаграммы тактовых импульсов и выходных напрял ений.

Предложенная логическая схема «И-НЕ/И состоит из двух динамических элементов / и2 с входами 3, 4, 5 и выходами 6. Выход каждого элемента соединен с одним из входов шторого элемента, причем остальные входы элемента 2 подключены к источнику .постоянного питания.

Каждый динамический элемент (фиг. 2) состоит из входной диодной схемы «И на диодах 7, 8, 9 1 резисторе 10, подключенном ко входу 11 источника тактовых импульсов, разделительного конденсатора 12, разрядного диода 13 и инвертирующего транзистора 14. База транзистора 14 через разделительный

конденсатор 12 соединена с выходом диодной схемы «И и с катодом разрядного диода 13, анод разрядного диода 13 подсоединен ко входу 15 источника смещения.

Тактовые импулисы (фиг. 3) имеют симметричную прямоугольную .форму со скважностью, равной 2. Импульсы питания соседних логических схем сдвинуты один относительно другого на четверть периода.

Если во время действия положительного импульса генератора импульсов (ГИ) на одном или нескольких входах элемента I дейст1вует запрещающий .низкий уровень потенциала (сигнал а, фиг. 3), то от ГИ, включенного на входе //, через резистор 10 течет ток: в элециала, а в элементе 2 - через разделительный конденсатор 12 в базу транзистора 14. Ток, текущий к;базе транзистора 14, открывает его, и на коллекторе транзистора устанавливается низкий уровень нотенциала (сигнал б). Транзистор элемента остается з.акрытым, и на его выходе сохраняется высокий уровень .потенциала.

Транзистор 14 элемента 2 будет открыт до конца Положительного импульса ГИ. С приходом отрицательного импульса ГИ транзистор быстро закроется обратным током базы, текущим через резистор 10 и .конденсатор 12. После закрывания транзистора конденсатор 12 разряжается через диод /5.

Запрещающий сигнал а иа входе элемента / с предыдущего элемента заканЧИ1вается вместе с положительным импульсом ГЯцред (фиг. 3), т. е. на 1/4 периода раньше окончания лоложительного им:пульса ГИ питания элемента ./. Чтобы транзистор 14 в элементе / оставался закрытым до окончания положительного импульса ГИ, на входе его подается запрещающий импульс б с выхода элемента 2.

Если во время действия полол ительного импульса Г И на всех входах элемента 1 действует разрещающий высокий уровень потенциала, то на -выходе этого элемента формируется импульс, который поступает на вход элемента 2 и запрещает формирование имлульса на

его выходе. Для обеспечения задержки бтк рывания транзистора в элементе 2 сопротивление резистора 10 в нем выбирается большей величины, чем сопротивление резистора 10 в элементе /, а свободные входные диоды подключаются к источнику итостоянного питания. Предложенная логическая схема обладает -повышенной помехоустойчивостью, обеспечиваемой разделением входных и выходных цепей элементов конденсатором и введением в цепь базы транзисторов напряжения смещения -fcMПредмет изобретения

Логическая схема «И-НЕ/И, состоящая из двух динамических элементов -с взаимно инверсными выходами, каждый из которых содержит входную диодную схему «И, разделительный конденсатор, диод в цепи разряда и инвертирующий транзистор, отличающаяся тем, что, с целью повышения быстродействия и увеличения помехоустойчивости, в элементе база инвертирующего транзистора

соединена через разделительный конденсатор с выходом диодной схемы «И и через диод цепи разряда конденсатора-с источником смещения, причем выход каждого из динамических элементов соединен с одним из 1входав

второго элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ДИНАМИЧЕСКИЙ ЭЛЕМЕНТ «НЕ—ИЛИ» НА ТРАНЗИСТОРАХ | 1968 |

|

SU218528A1 |

| ДИНАМИЧЕСКИЙ ИНВЕРТОР | 1969 |

|

SU235817A1 |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И-ИЛИ», «И-ИЛИ-НЕ» | 1969 |

|

SU238599A1 |

| МНОГОВХОДНОЙ ДИНАМИЧЕСКИЙ ИНВЕРТОР НА ТРАНЗИСТОРАХ | 1968 |

|

SU209838A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| СИГНАЛЬНОЕ УСТРОЙСТВО ТРАНСПОРТНОГО СРЕДСТВА | 1993 |

|

RU2070114C1 |

| Ждущий мультивибратор | 1978 |

|

SU782134A1 |

| УНИВЕРСАЛЬНЫЙ ДИНАЛ1ИЧЕСКИЙ ЭЛЕМЕНТ | 1969 |

|

SU253867A1 |

| Трансформаторный широтно-импульсный модулятор | 1985 |

|

SU1383475A1 |

Даты

1970-01-01—Публикация