(54) ПРЕОБРАЗОВАТЗЕт ДВОИЧНОГО КОДО УГЛА В ДВОИЧНОДЕеяТИЧНО-ПШСТИДЕСЯТйР11ЧНЫЙ ЮД ГРАДУСОВ; МИНУТ, СЕКУНД V у

t

Изобретение относите к автомати ке и вычислительной технике и может : быть.использовано при построении прербраэрвателей 1кодов : .

Известен преббразоватёльдвоичного угла в код градусов, ««втут секунд, содёржа&шй г енератор импульсов, двоичный счетчи1сгЯ Ьично десятичны счетчики, блоки коррёкции, :ЭлемеиШ:И:, Cll.; ; V;;;.:,,: /;,:,

Недостатки иЭвёстногр устройства

.сострят ; в низкой :бЬ1СТрРДеЙСТ8ИИ и

низкой надежнрсти. /

Наиболее близким к изобретению . по технической сущности и схемн м построению является прёобразб ател двоичного кода угла в дврйчнр-яеея тично-iaeстидесятиричньгй код граяу;т . сов г минуту сёкуид, 6од€ ржа1ф«й pfeTh чик выходногр кода, срстоййИЙ из ; тетрад и триад, послёдоватёя йох оединаиНые генератор тактовых HMtynbсов, первый и втррой распределителя импульсов и группу мультиплёксеров, и элемейт . ;

Недостатки известного преобразователя состоят в относительно низKCJM быстродействии и необходимости использования тетрады и -црлода выходно-.

гр счетчика с выводами счетрных входов

-всех разрядов..;,- , .. .«,; .;.;у-.-,;, /;:

: Цель изобретёни является повншёние быстродейотвия,, р асип{рёниё видов двоично-jвtвcятйчнoго кодирования и нрмейклатурц тетрад и триад шадхэднргр счетчика

Поставленная цель ,достигается тем, что в Преобразователь Двоичного

10

: йода угла в дВоИчнбг-дееятйчнр-шести1|есгяти ричвый крдлрадусрв тонут и секунд соде ржаздий счез-чик вазсРднргЬ кодй, сюстсищий,

импульсов, п6 ледоВ( сбед:шненньте

15

:яервый JH второй распределители импульсов/ тгЬстрвь входа koTOpux средйыены с I и (Ш гёиар

iTopai ймпул1 р6в соотвётствеинр,й

lajieMeiH Й

20

: об вас.ряами сброса счётчика в 1ходиЬгб

; Kojuta первый Вхрл элемента И соединён

i С выходом старшего разряда второго

распрёделит еля импульсов, а второй вхр:Д элемента И является входом син25хронизации прёобразоват.еля, первую

и вторую группы мультиплёксеров, выходы KO ijsiaJx соединены с первыми и вторыми счетными вхрдами соответ: ствуквцих декад счетчика выходного

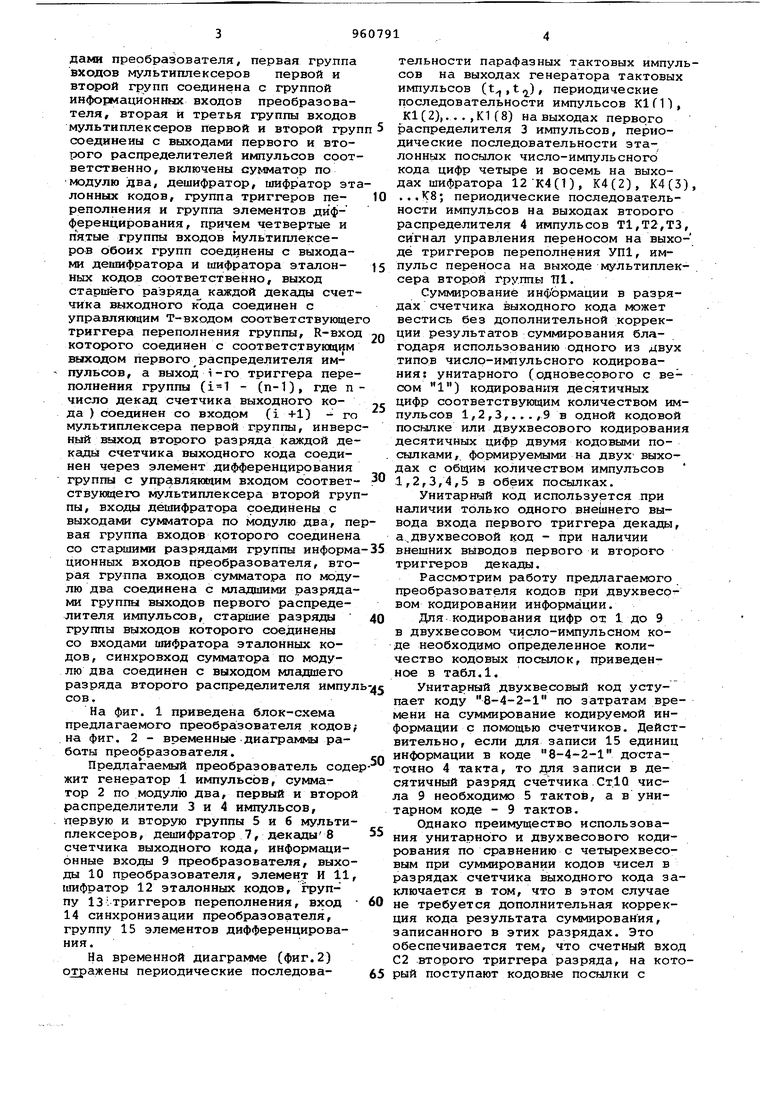

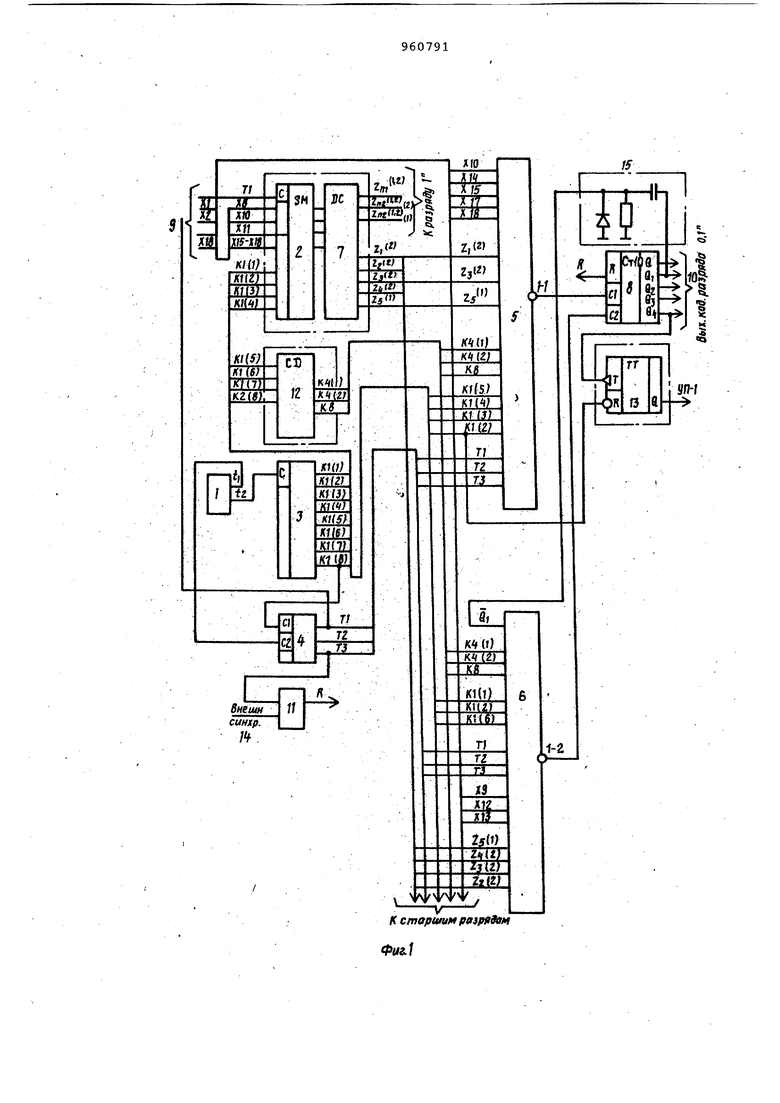

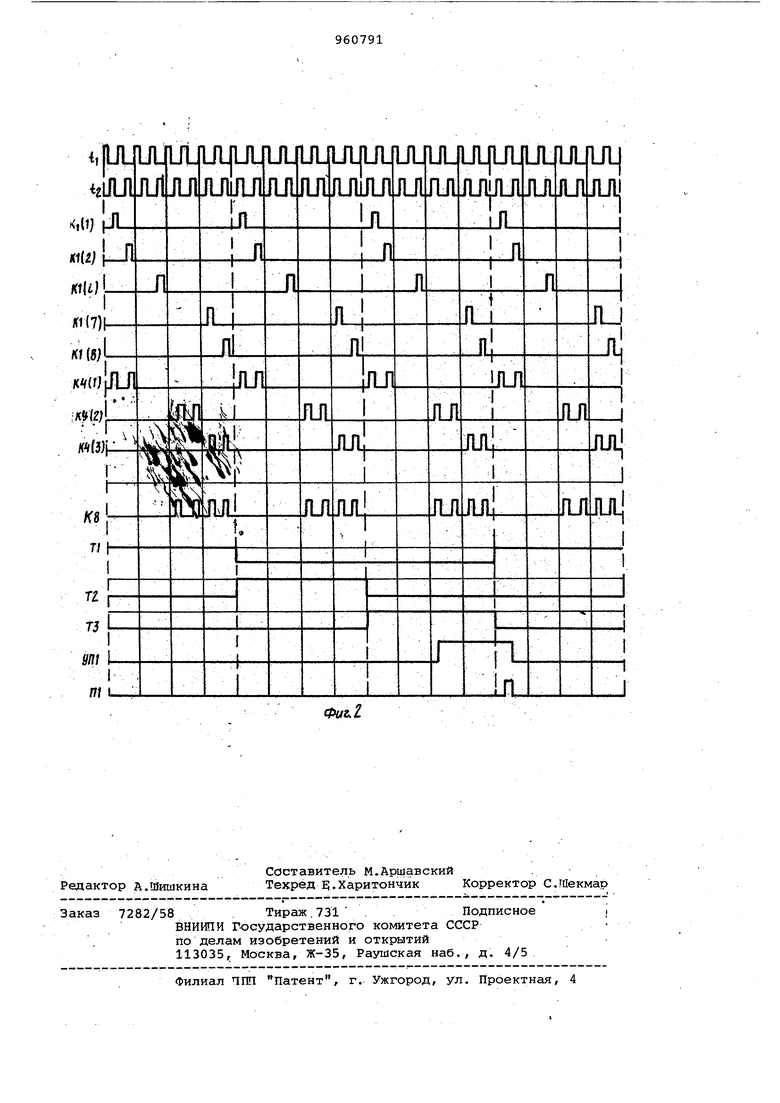

30 ; крда, выхрды которого являются выходa и преобразователя, первая группа входов мультиплексеров первой и второй групп соединена с группой информационных входов преобразователя, вторая и третья группы входов мультиплексеров первой и второй гру соединены с выходами первого и второго распределителей импульсов соот ветственно , включены сумматор по модулю два, дешифратор, эт лонных кодов, группа триггеров переполнения и группа элементов дифференцирования, причем четвертые и п:ятые группы входов мультиплексеров обоих групп соединены с выходами дешифратора и шифратора эталонных кодов соответственно, выход старшего разряда каждой декады счетчика выходного кода соединен с управляющим Т-входом соотЬетствующег триггера переполнения группы, R-вход которого соединен с соответствующим выходом первого распределителя импульсов, а выход i-го триггера переполнения группы (1 1 - (п-1), где п число декад счетчика выходного кода ) соединен со входом (i +1) - го мультиплексера первой группы, инвер кьлй выход второго разряда каждой декады счетчика выходного кода соединен через элемент дифференцирования группы с управляющим входом соответствунэдего мультиплексера второй груп пы, входы дешифратора соединены с выходами сумматора по модулю два, пе вая группа входов которого соединена со старшими разрядами группы информа ционных входов преобразователя, вторая группа входов сумматора по модулю два соединена с мпадшими разрядами группы выходов первого распределителя импульсов, старшие разряды группы выходов которого соединены со входами шифратора эталонных кодов, синхровход сумматора по модулю два соединен с выходом младшего разряда второго распределителя импул сов. На фиг. 1 приведена блок-схема предлагаемого преобра:зователя кодов на фиг. 2 - временные диаграммы работы преобразователя. Предлагаемый преобразователь соде жит генератор 1 импульсов, сумматор 2 по модулю два, первый и второй распределители 3 и 4 импульсов, первую и вторую группы 5 и 6 мультиплексеров, дешифратор 7, декады8 счетчика выходного кода, информационные входы 9 преобразователя, выходы 10 преобразователя, элемент И 11 1йифратор 12 эталонных кодов, группу 13, триггеров переполнения, вход 14 синхронизации преобразователя, группу 15 элементов дифференцирования. На временной диаграмме (фиг.2) отражены периодические последовательности парафазных тактовых импульсов на выходах генератора тактовых импульсов (t,t), периодические последовательности импульсов К1С11, К1 (2),. , . ,К1 f 8) на выходах первого 1эаспределителя 3 импульсов, периодические последовательности эталонных посылок число-импульсного кода цифр четыре и восемь на выходах шифратора 12К4(1), К4(2), К4СЗ), ...К8; периодические последовательности импульсов на выходах ВТОРОГО распределителя 4 импульсов Т1,Т2,ТЗ, сигнал управления переносом на выходё триггеров переполнения УП1, импульс переноса на выходе мультиплексера второй Группы Til. Суммирование информации в разрядах счетчика выходного кода может вестись без дополнительной коррекции результатов суммирования благодаря использованию одного из двух типов число-им1ульсного кодирования; унитарного (одновесового с весом 1) кодирования десятичных цифр соответствующим количеством импульсов 1,2,3,...,9 в одной кодовой посылке или двухвесового кодирования десятичных цифр двумя кодошлми посылками, формируемыми на двух выходах с общим количеством импульсов 1,2,3,4,5 в обеих посылках. Унитарный код используется при наличии только одного внешнего вывода входа первого триггера декады, а,двухвесовой код - при наличии внешних выводов первого и второго триггеров декады. Рассмотрим работу предлагаемого преобразователя кодов при двухвесрвом кодировании информации. Для кодирования цифр от 1 до 9 в двухвесовом число-импульсном коде необходимо определенное количество кодовых посылок, приведенное в табл.1. Унитарный двухвесовый код уступает коду 8-4-2-1 по затратам времени на csa«миpoвaниe кодируемой информации с помощью счетчиков. Действительно, если для записи 15 единиц информации в коде 8-4-2-1 достаточно 4 такта, то для записи в десятичный разряд счетчика CT.IQ числа 9 необходимо 5 тактов, а в унитарном коде - 9 тактов. Однако преимущество использования унитарного и двухвесового кодирования по сравнению с четырехвесовым при суммировании кодов чисел в разрядах счетчика выходного кода заключается в том, что в этом случае не требуется дополнительная коррекция кода результата суммирования, записанного в этих разрядах. Это обеспечивается тем, что счетный вход С2 второго триггера разряда, на который поступают кодовые посылки с весом 2 , находится вне кольца обратной связи, исключающей шесть избыточных состояний декады. Благодаря этому, при записи в декаду значения очередного слагаемого в двухвесовом коде исключена возмож ность получения любой из шести запр щенных комбинаций. В предлагаемом преобразователе кодирование информации производится с помощью эталон ных кодовых посылок десятичных цифр для формирования которых введен шифратор 12 эталонных последователь ностей. На выходах шифратора 12 формируют ся периодические последовательности эталонных кодовых посылок с периодом повторения, равным Тц(фиг.2). К4(1), К4(2), К4{3) - для кодирования цифры 4; К8 - для кодирования цифры 8. В качестве периодических последо вательностей эталонных одноимпульсных кодовых посылок цифры 1, распре деленных на вход С1 первого триггера декады, одноимпульсных кодовых посылок цифры 2, распределяемых на вход С2 второго триггера декады, в предлагаемом преобразователе кодов используются периодически, пос довательности импульсов К1(1), К1 (2),...К1(7),К1(8) , формируемые на выходах neipBoro распределителя 3 импульсов. Последовательности эталонных .кодовых посылок K4(i) и К8 распределя ются на вход С2 второго триггера де кады счетчика при кодировании цифр и 8 во всех разрядах счетчика. Кодо вые посылки цифр 3,5,7 и 9 распреде ляются на входы С1 и С2 первого и второго триггеров каждого разряда счетчика выходного кода. Одноименные кодовые посылки одноимпульсные. К1 (1) . К1 (2) ,. . .,К1 (8) и двухимпульсные К4(1), К4(2), К4(3 различаются только взаимным располо жением импульсов в интервале времени Тц, задаваемым вторым распределителем импульсов. Введение шифратора число-импульс ного кода позволяет повысить эффективность использования тактов K(i) в каждом из интервалов времени Ту| с учетом межразрядных импульсов переноса. С помощью мультиплексеров 5 и 6 относящихся к первым и вторым три-ггерам разрядов счетчика выходного кода, производится уплотнение информации на счетных входах С1 и С2 первого и второго триггеров каждого разряда, поступайщей с трех направлений, с выходов Kl(i) первого распределителя импульсов и шифратора 12 K(i), с выходов Ти второго распределителя импульсов; с информационного входа Хо преобразователя. Кроме того, на входы С1 и С2 первого и второго триггеров каждого разряда поступают импульсы переноса П из предыдущего триггера мпадизей разрядности. С помощью группы триггеров переполнения., включенных между соседними разрядами выходного счетчика, производится разделение во времени операций записи информации в каждый из разрядов выходного счетчика и записи межразрядных импульсов переноса, производимой в наперед заданные моменты времени посредством использования первого распределителя импульсов в качестве генератора синхроимпульсов. Рассмотрим работу предлагаемого преобразователя кОдов. Работа группы триггеров 13 переполнения основана на записи и хранении в течение интервала времени, не превышающего длительности периода Ти импульсной последовательности Kl(i) импульса переноса, возникакяцего на выходе младшего разряда счетчика выходного кода после формирования в этом разряде суммы кодов чисел, превышакяцей десять единиц. Состоя ние Q 1 на .выходе триггера;13 используется в качестве управляю1иего сигнала УП1 при формировании сигНала переноса П , И предлагаемом преобразователе кодов импульсы переноса разрядов 0,1, 1, . . .,10° выходного счетчика формируются синхронно с импульсами К1(1), К1 (2) , . . .,К1 С8) последовательностей, снимаемых с выходов первого распределителя 3 импульсов, одновременно используемого в качестве формирователя синхроимпульсов межразрядных, переносов П1, П2, ПЗ, П4, П5. 3 качестве примера рассмотрим как происходит формирование импульса переноса П1 из разряда 0,1 в разряд 1 счетчика выходного кода. Импульсы переноса П1 из разряда 0,1 в разряд 1 , синхронные с импульсами последовательности К1(1), формируются с помощью мультиплексера, связанного с первым триггером декады единиц секунд, когда поступает сигнал УП1 положительной полярности с выхода триггера 13 в положительный импульс последовательности К1(1). К После.окончания формирования синхронного импульса переноса П1 триггер 13 устанавливается в исходное состояние отрицательным фронтом синхросигнала последовательности К1С1), Очевидно, что в случае отсутствия импульса переполнения на выходе младшего разряда счетчика триггер 13 продолжает находиться в нулевом состоянии, когда сигнал и импульс переноса П1 не формируется.

В интервале времени между двумя одноименными синхроимпульсами переноса, равном Т,4, количество единиц число-импульсного кода, суммируемого с кодом, ранее записанным в данном разряде, не должно превышать 10 и б единиц для десятичного и шестиричного разрядов, соответственно.

Действительно, если.в десятично разряде .формируется сумма чисел 9+10, где 9 - максимальное значение числа, хранимого в декаде, то на выходе декады при суммировании формируется один импульс переполнения, т.е. устанавливается состояние (), а в декаде вновь фиксируется код числа 9.

Введение синхронизаторов импульсов межразрядных переносов позволяет производить суммирование кодов параллельно и одновременно во всех эазрядах выходного счетчика. При этом на время формирования синхпонных импульсов переноса П1 ,П2,...,П5 . в предлагаемом преобразователе предусмотрен запрет поступления кодов суммируемых чисел в соответствующие разряды выходного счетчика.

С учетом количества тактов преобразования, отведенных на синхронизацию импульсов межразрядных переносов, количество тактов преобразования При двухвесовом число-импульсно кодировании 2-1 суммируе фпс кодовых посылок не превышает 60, при унитарном кодировании - не превышает 90.

Дальнейшее значительное уменьшение количества тактов преобразования, например в 3 раза (до 21 такта) , в предлагаемом преобразователе кодов достигается тем, что в него введены вспомогательные накопительные сумматоры по модулю 2 - деш раторы состояний логических единиц входного кода двоичных разрядов, сгруппированных поразрядно, по разрядам 0,1, 1..., f, 10 счетчика выходного кода по признаку объединения равнЕлс слагаемых цифр соответствукяци с десятичных эквивалентов

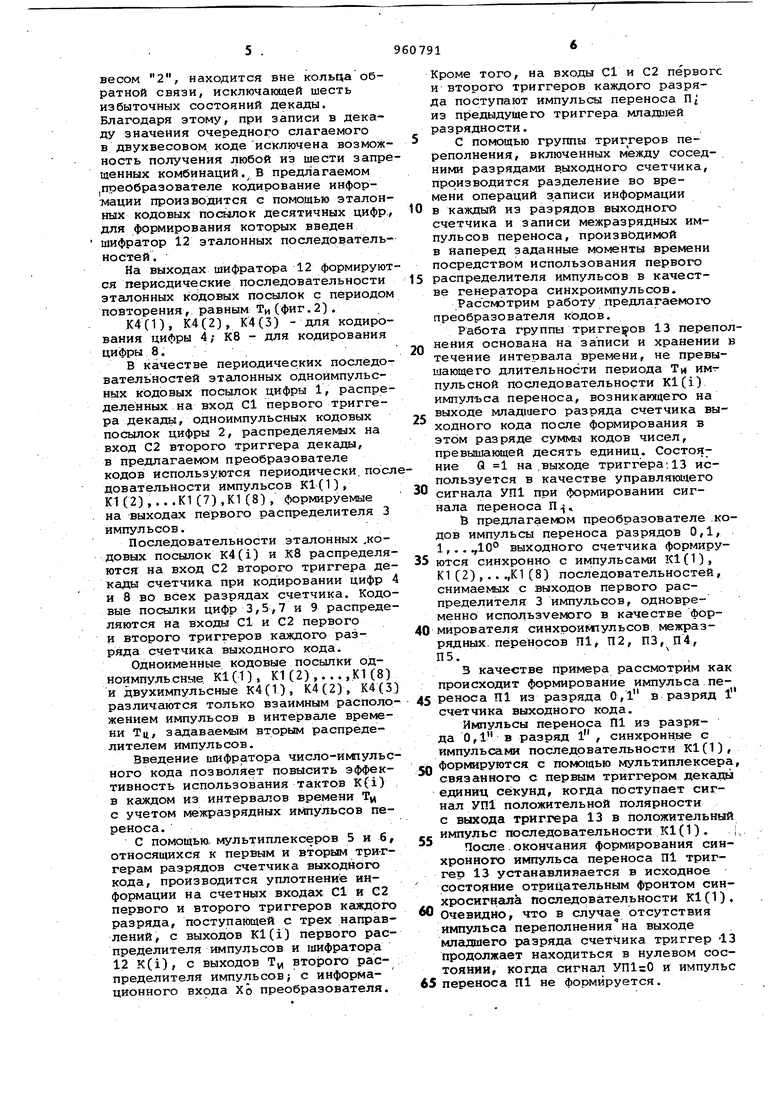

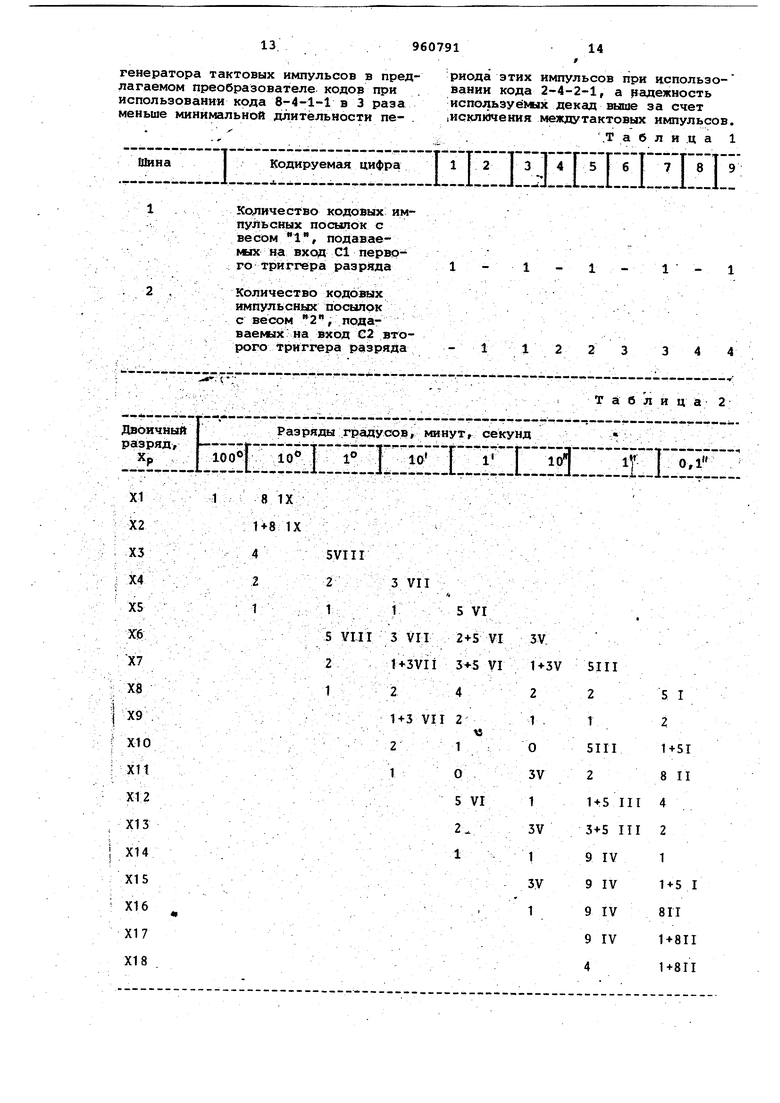

Разряды входного двоичного кода сгруппированы в 9 групп, показанных Втабл.2.

Необходимым условием для выделений групп двоичных разрядов является принадлежность цифр их десятичных эквивалентов к одному и йму же десятичному разряду га.

Достаточным условием объединения в одну группу ряда двоичных разрядов входного кода является равенство слагаемых цифр тех десятичных эквивалентов группируемых двоичных разрядов, которые относятся к одному и тому десятичному разряду

m счетчика выходного кода. В табл.2: объединены в 9 групп слагаемые цифр, равные или большие 5 из числа относящихся к десятичным разрядам, а также слагаемые цифр, равные или 5 большие 3 из числа относящихся к шестиричным разрядам выходного кода.

Например, в группу 1 объединены - двоичные разряды 8,10 и 15 входного , кода по принадлежности соответствующих цифр 5,6 и 6 к разряду 0,1 выходного кода. Достаточным условием объединения 8,10 и 15 двоичных разрядов в группу 1 является равенство слагаемых 5 цифр 5 и 6, представленных в виде сумм слагаемых 5+0 и 5+1, соответственно, из числа относящихся к десятичному разряду 0,1 выходного кода.

Согласно табл.2 в группу V объединены 6,7,11,13,15 двоичные разряды по равенству слагаемых 3 цифр 3 и 4, представленных.в виде сумм слагаемых 3+0 и 3+1, из числа относящихся к шестиричному разряду 10 5 выходного кода.

Как следует из табл.2, одни и те же разряды входного двоичного кода мэгут входить в различные группы.

Например, разряд 6 двоичного кода входит в V, VI, VII и VIII группы.

В предлагаемсэм преобразователе кодов производится суммирование состояний логических единиц разрядов входного двоичного кода при ,входящих в одну группу, и дешифрация результатов суммирования с помощью соответствующих сумматоров-дешифраторов. Сигналы на выходах сумматоров-дешифраторов используются в качестве управляющих при записи кодов каждой из сумм слагаемах цифр, принадлежащих к одной группе, относящейся к млатчему разряду (т-1) счетчика выходного кода.в 5 два соседних разряда (т-1).и m , где разряд m - старший из названных разрядов.

Благодаря введению предлагаемых сумматоров-дешифраторов значительно сокращается время преобразования кодов за счет записи суммируемых кодов в два соседних разряда, когда формирование каждой единицы переноса в старший разряд произвое дится без суммирования 10 единиц в младшем разряде счетчику выходного кода.

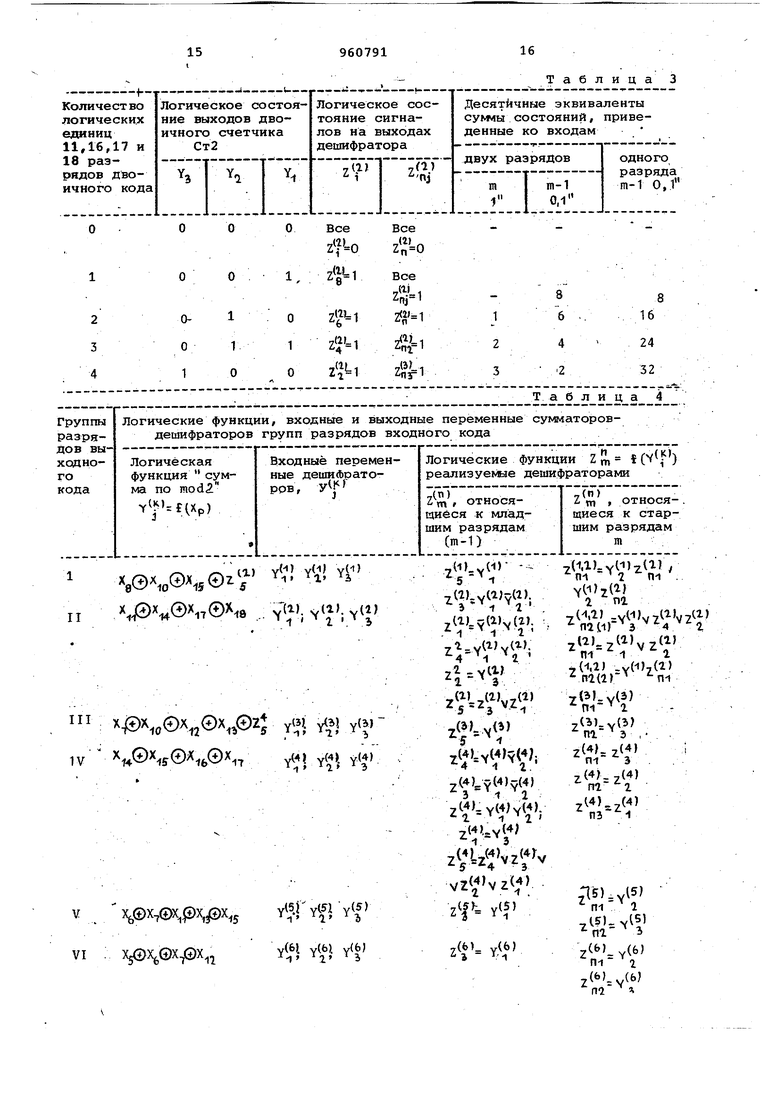

Рассмотрим работу сумматора по людулю два и дешифратора II группы разрядов, объединяющей 11,16,17,18 разрядов двоичного кода.

Сумматор по модулю два состоит из последовательно соединенных элементов 4-2И-4ИЛИ элемента 2И, трехразрядного двоичного счетчика Ст2. 5 Первые входы элемента 4-2И-4ИЛИ

соедийенц с входами 11,16,17,18 разрядов входного Kpjia, вторые входы - с выходами К1(1), К1(2), К1(3) К1(4) первого распределителя импульсов, второй вход элемента 2И подключен к первому входу Т1 второго распределителя импульсов, выходы дешифратора 7 Zg-ze. Z Zl-подключены к входам мультиплексера, выход которого - с входом второго триггера декады 0,1, а выходы пг пь первым входам мультиплексеров, выходы которых соединены с входами первого и второго триггеров декады 1. ; Рабата сумматора по модулю два и дешифратора осуществляется следующим образом.

Во время действия сигнала , поступающего с первого выхода второго распределителя 4 импульсов, в течение четырех тактов поспедовательностей к1С1)-К1С4) йа вход двоичного счетчика поступает количество импульсов С V1 V 2 V 3 V4, равное числу логических единиц состояний 11, 16, 17, 18 разрядов входног кода. После окончания четвертого такта К1(4) на выходах Y, Y,.Y двоичного счетчика Ст2 сохраняется |одна из следую1чих комбинаций логи-; ческих состояний, записанная в зависимости от количества логических единиц .состояний двоичных разрядов в группе (см.табл.3).

„При этом выходные сигналы Zn-, Zp Zp, группы разрядов используются в качестве управляющих при записи соответственно 1V 2 V 3 единиц переноса в старший разряд l счетчика выходного кода, а выходные сигналы Z|;, используются в качестве управляющих при записи 8 V 6 V 4 V 2 единиц в младший разряд 0,1. Следует отметить, что 7 управляющих сигналов Z; достаточно снимать только с четырех выходов дешифратора за счет равенства следуmHV гилналпв г( 7 7(г) 7() ™ 6 n1 4 П5

Z

Согласно табл.3 суммирование 32 единиц суммы цифр десятичных эквивалентов 11,16,17,18 разрядов, относящихся к разряду 0,1 сводится к записи в разряд l не более 3 единиц переноса и к записи в разряд 0,1 8 V 6 V 4 V 2 единиц за время, не превышающее 4 такта Kl(i) при двухвесовом число-импульсном кодиро НИИ вместо 16 тактов XI (1), необходимых в том случае, если не использовать сумматор по модулю два и дешифратор.

Следует отметить, что в случае, суммирования цифр 5, относящихся кдесятичным разрядам выходного кода, и цифр 3, отйосящихся к шестиричным разрядам 10 и 10 выходного кода, нет необходимости в дешифраторе .

В. этом случае сигналы логических единиц, снимаемые непосредственно с выходов У; двоичного счетчи- ка Ст2, используются в качестве управлдющих ,-np записи 5 единиц в младший десятичный разряд (при ), при записи 3 единиц в младший шестиричный разряд (при ) и при записи 1 или 2 единиц переноса в соответствующие старшие разряды (при Y, 1 или ).

Аналогично строятся сумматоры по

5 модулю два и дешифраторы других групп разрядов.

Логические функции, выполняемые сумматорами по модулю два и дешифраторами 9 групп в соответствии

0 с табл.2, приведены в табл,4 из которой следует, что каждый из дешифраторов III и IV групп, .взятых в отдельности, состоит из двух элементов 2И. Соответственно, в 1,1Г1,У,

5 1Х группах в дешифраторах нет необходимости и соответствующие управляю. щие сигналы снимаются непосредственно с выходов счетчиков Y,,,Y,

Y i

I3«

Q На основе рассмотренных одноступенчатых сумматоров по модулю два и дешифраторов компонуются двухступенчатые блоки при незначительном усложнении исходных схем.

Рассмотрим работу двухступенчатого

5 сумматора по модулю два и дешифратора, построенного на основе одноступенчатых схем I,Iir,V, групп двоичных разрядов.,

Реализуется на основе одноступенчатых схем 5М-ДС1Г1 и IV групп двоичных разрядов входного кода путем замены элемента 4-2И-ИЛИ на элемент 5- 2И-5ИЛИ сумматора по модулю два и дешифратора III труппы и введения

5 элемента 4 ИЛИ между выходами сумматора ч V. группы и первым входом введенного элемента 2И, входящегх в состав элемента 5-2И-5ИЛИ, второй вход которого подключен к выходу

0 К1(5) первого распределителя импульсов.

После четырех тактов К1(4) на выходах одноступенчатого сумматора по. модулю два и дешифратора IV груп5 п формируются управляющие сйгйалы Z, которые могут использоваться для непосредственной записи 9v 8v 7v б единиц в разряд l в случае, если двухступё-нчатая схема не реализована. .

60

В случае использования двухступенiWV

чатой схемы управляющие сигналы Z

на выходах дешифратрра IV группь разрядов используются для записи 45 4 V 3 V 2 V 1 единиц в разряд l ,

а управление записью пяти единиц, дополняющих значения цифр 4,3,2,1 До 9,8,7,5, соответственно, ведется с выходов Zf(3) дешифратора III группы разрядов входного кода.

Рассмотренное преобразование одноступенчатых су Ф1аторов по модулю два и дешифраторов в двухступенчатую позволяет уменьшить количество-тактовых импульсов Kl(i) записи информации в разряда выходного счетчика на 5 единиц. ,; Логические функции, выполняемые дёухступенчатыми сумма:торамя и дешифраторами III и IVгрупп раэрят дов входного кода, приведены в табл.4.

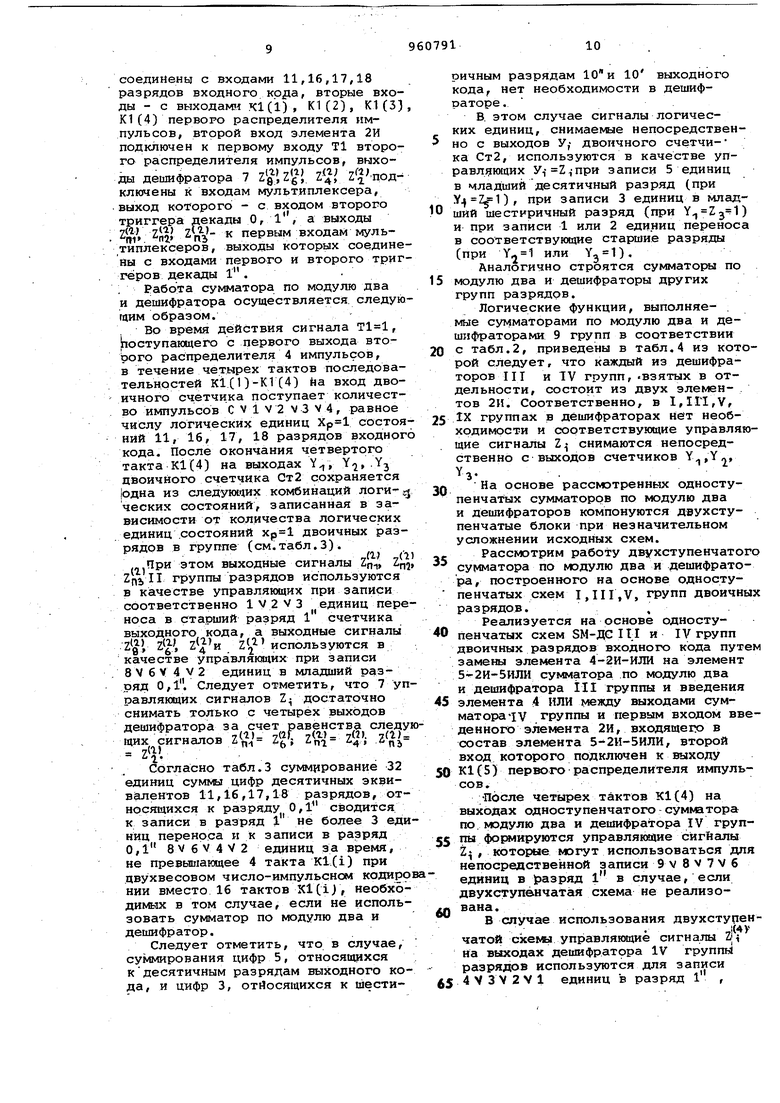

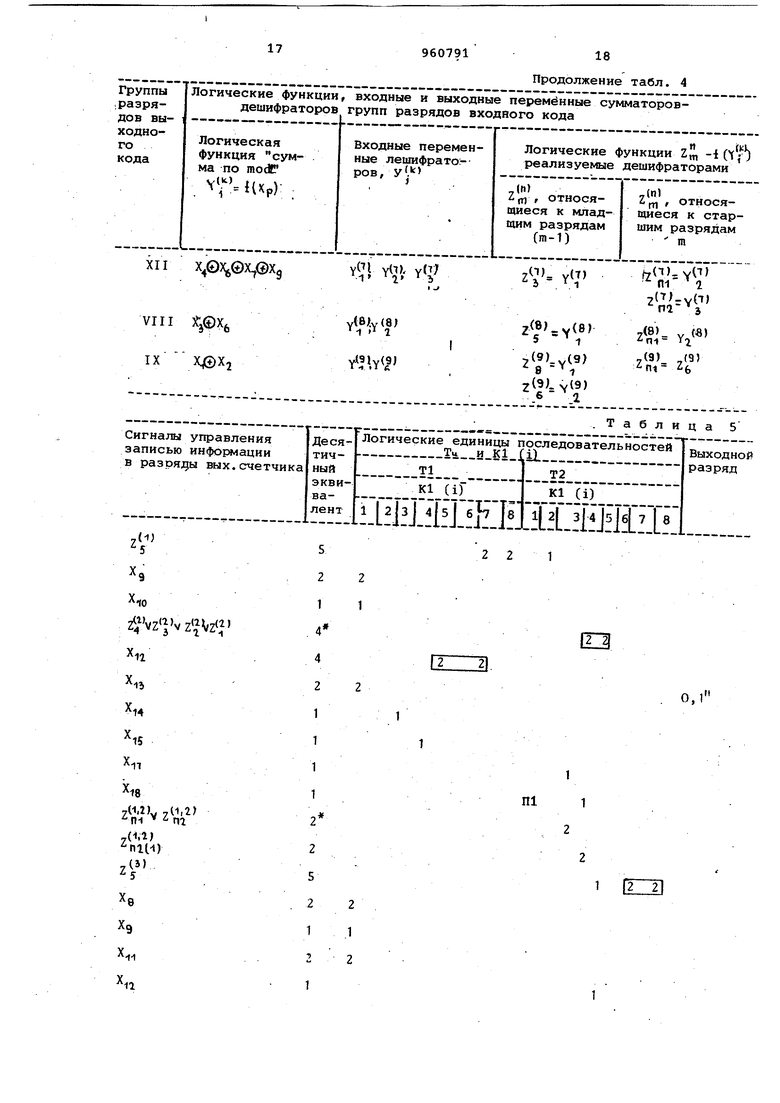

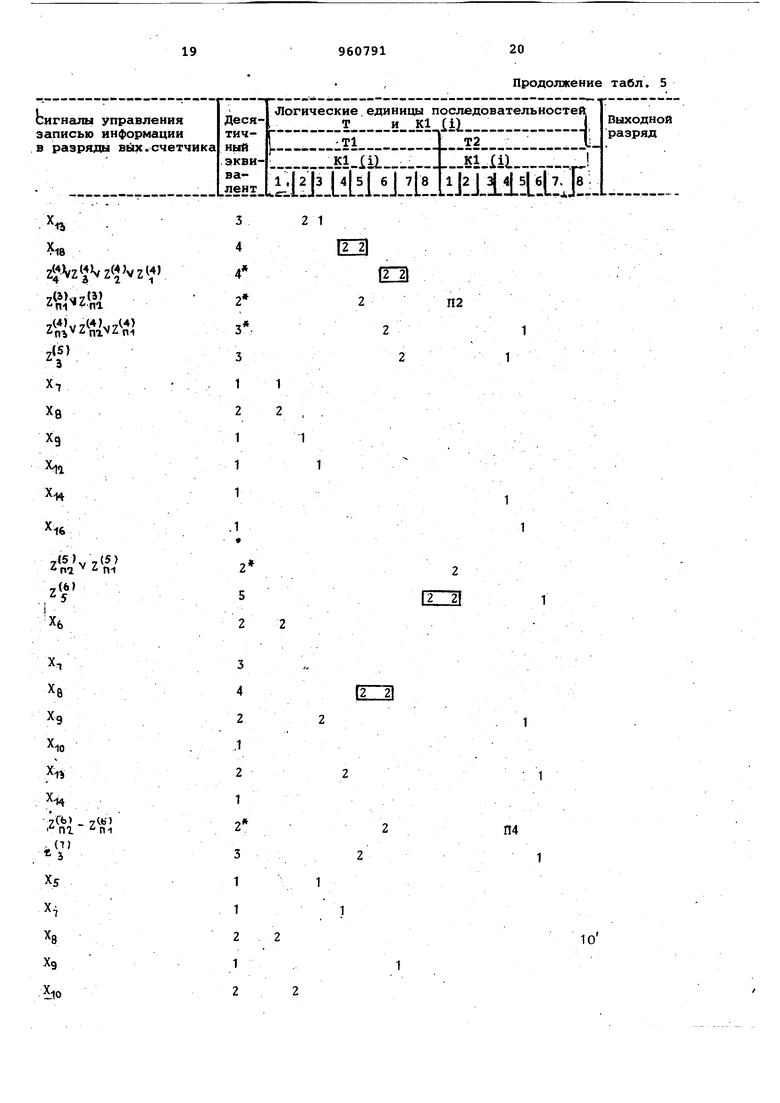

Распределение, кодовых посыпок на входы разрядов счетчика выходного кода предлагаемого преобразователя кодов с введенными сукматорами 91 дешифраторами приведено в табл .5, из которой следует, что запись суммируешлх кодотсс посилок двухвесового число-импульсного кода цифр десятичных эквивалентов 18-разрядного входного двоичного кода с помозыо предлагаемого преобразОВ ятеля кодов производится за 16 тактов KlCi), где ,2,3,7,8. При этом достаточно фо «ировать 3 последовательности импульсов Т1,Т2,ТЗ на выходе второго распределителя импуль-сов. В интервале времени, когда ТЗ-1 при К1(1)1, КТ{2}«Т К1(3)1, К1(4)1, К1(5).1 осущестйляется перепись в старшие тех единиц переноса П1, Л2, ПЗ, 114, П5, которые остались храниться в триггерах 13 соответствующих синхронизаторов после окончания суммирования в прелп шущем интервале времени когда

Так как перед началом цикла преобразования кодов во время, пред шествующее сигналу , разряды счетчика устанавливаются в нулевое состояние импульсов , то на протяжении интервала допускается запись в десятичн«51й разряд не более 19 единиц, а в шестйряч-ный разряд - не более 11 единиц. Кроме того, в этом случае при Т1«1 и К1С1)1 в первые и вторы триггеры всех разрядов можно одновремейнб записать коды чисел 1 и 2 (см. .ВУ. : . - , ; , ....

В табй.5 , цифрами.1 и 2 обОзначены кодовыё посылки, распределяемые на входы первого и второго 1 | иггеров разрядов выходного счетчика,соответственно. Ргкмками очерчены ; кодовые посыпки К4С1) К4(2), К4(3) и К(8), формируекиё на выходе ишфхзатора число-импульсного кода За а тактов К1(1), К1 (2) ,.. .,К1 (8) при в рассматриваемой реализации преобразователя может бытЬ

осушествлена запись 17. единиц в деся ичные разряды счетчика выходного кода. В табл.5 показано, что при в предлагаемом преобразователе кодов предусмотрен запрет поступления кодов суммируемых чисел в соответствуквдие разряды во время .формирования синхронных импульсов переноса: в разряде 0, при К1С1) Ь в разряде при kl(V) 1. И К1(2) , в разряде 1о - при К1(2) 1 и К1(3)1, в разряде 1 при К1(3)1 и К1С4)1, в разряде 10:- пои К1С4)1 и К1(5) 1, в разряде 1° - при К1(5)1. В рассмотренной реализации предлагаемого преобразователя кодов нет необходимости в синхронизаторе межразрядных переносов кюжду разрядами 1 и 10

V .. .,. ,, .--,

Таким образом, за счёт введения™ в предлагаемый преобразователь шифртора эталонных кодов группы триггеров, переполнения ц сукматоров по модулю два и дешифраторов сумм состояний логических 1 групп разрядов входного двоичного кода количество тактов 1феобраз6ван}{я 18-разрядного двоичного кода в код .градусов, ежнут, секунд, десятых долей секунд сводится к 21 такту при двухвесоврм число-чмпульсном кодаровании.

Яри унитарном кодировании информации число тактов преобразования кодов не превышает 40. Следуйт отметить, что при существенном упрощении сумматоров-дешифраторов, Koirда, например,ограничиваются суммированием т«лпько И и III групп J BOичнык разрядов входного кода, количество тактов преобразования при двухвёоовом чисяо-импульсном йодировании не npeBtaiiaeT 50 / при унитарном коддаро вании - не превш т 80,

Таким Образом, с помо1лыо предлаraetftix схемши р€(шений преоб разователя кодов .обеспечивается ;независимост структуры предлагаемого преобразователя кодов от типа двоично-десятичного кодирования и наличия внешних выводов Счетных входов второго третьего и четвертого триггеров декад,; выходного счетчика что суибствено уПрощает стыковку предлагаемого преобразователя кодов с внешними абонентами, позволяет широко использоватб микросхемы, повьйаенной

.интеграции, в то как код 2-4-2-1, Исйояьзуемый в известном преобразователе, не имеет микросхемной ресйиаациК и широкого рас: пространенйя. Кроме тогог существен но повышено быстродействие - коли:чество тактов преобразования кодов уменьшается в 4 раза (с б4 ,тг1ктов до 21) при прочих равных условиях

.{минимальная длительность периода

следования t импульсов на выходе

генератора тактовых импульсов в предлагаемом преобразователе кодов при использовании кода 8-4-1-1 в 3 раза меньше минимальной длительности пе- .

риода зтих импульсов при нспользовании кода 2-4-2-1, а надежность используемых декад выше за счет .исключения междутактовых импульсов.

.Т а б л и д а 1

Таблица 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1976 |

|

SU646327A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1985 |

|

SU1396280A2 |

х /-V IX) (а(+)г,

gVX toigf ff

. . vllJ

X jr7)X

II 1

.-,0X,02

XJ)X(4

10 12 1 5 ч 1 л

X..(

(i),feCiJX,Y(4) у(4) Y(4)

IV

,i(i)X,.

V VI

, Y.-

Т а б л и ц а

7(1Д) m 2 ni .

YtiJi 2 nl

7ИД) -Y(4v:z v2 ., .

ni г

7(-1.2) -у( п1(2Г п-1

(

П1 2

7(Ь.у(5)

П1 Э , .

2

3

7(4)-7(4) П2 2

7(4). 7

:15).у15 п-1 , 2

П2 1

(ь

П-1 2

zC-LyCb)

П2 51

17

X,

10 2tt)

п 15

XH

15 Хп

18

7С1ЛЬ

П1 - пг

7(.i) 2п1И)

ЛЗ)

5 8

Хэ

X,. Хп

18

960791 Продолжение табл. 4

Таблица 5

221

12 21.

. 0.11П11

2 2

1 12 Л Сигналы управления записью информации в разряды вйх.счетч

21

3

4

vzW)

4

2

3

1

2

1

1

1

.1

2 5

2

3

4

2 ,1

2

1

2

П1

3

1

1

2

1

2

Продолжение табл. 5

П2

2 21

П4

10 Логические единицы последовательноете ..Ти.К1 Ш iilia. .. Выходной разряд iillil. lUiLlHliJ:

Сигналы управления записью информации в разряды вых.счетчика Минимальное из возможных значений эквивалента. Формула изобретения Преобразователь двоичного кода угла в двоично-десятично-шестидесят ричный код градусов,минут,секунд,сод жащий счетчик выходного кода,состоящий из декад, генератор импульс в, последовательно соединенные первый и второй распределители импульсов, тактовые входы которых сое динены с первым и вторым выходами генератора импульсов соответственно, и элемент И, выход которого соединен со входами сброса счетчика вы ходного кода, первый вход элемента соединен с выходом старшего разряда второго распределителя импульсов, а второй вход элемента И является входом синхронизации преобразовател первую и вторую группы мультиплексеров, выходы которых соединены с первыми и вторыми счетными входами соответствующих декад счетчика в.ыПродолжение табл. 5

Логические единицы последовательностей (11

Т2

Т1

.- Kl-Iil

.Ki.Iil

1 6j

...

«.-. L-L.-J. - - - соответствукхцего десятичного ходного кода, выходы которого являются выходами преобразователя, первая группа входов мультиплексеров первЬй и второй групп соединена с группой информационных входов преобразователя, вторая и,третья группы входов мультиплексеров первой и второй групп соединены с выходами первого и второго распределителей импульсов соответственно, отличающийся тем, что, с целью повышения быстродействия, в него введены cyive aTop по модулю два, дешифратор, шифратор эталонных кодов, группа триггеров переполнения и группа элементов дифференцирования, причем четвертые и пятые группы входов мультиплексеров обоих групп соединены с выходами дешифратора и шифратора эталонных кодов соответственно, выход старшего разряда каждой декады счетчика выходного кода соелинен с управляющим

Т-входом соответствующего триггера переполнения группы, R-вход которого схэединен с соответствующим выходом первого распределителя импульсов, а выход 1-го триггера пе;репрлнения группы (isl - (п-1), где п число декад счетчика илходного кода) - со входом ()-oro когльтиг плёксера первой группы,-инверсный .выход второго разряда каждой декады счефчика выходного кода сюединен ;через элемент дифференцирования 1т упп|ь| с управляющим входом соответствуюt ero мультйплексера второй группы, входы дешифратора соединены с выхо|Д;ами сумматора по модулю два, первая группа входов которого соединена (СО старшими разрядами группы инфор1мационных входов преобразователя, вторая Группа входов сумматора по модулю два соединена с младшими разрядами группы выходов первозх распределителя импульсов, старшие разряды группы выходов которого соединены со входами шифратора эталонных кодов сиихровход сумматора по модулю два , соединен .с выходом младацёго втсфого рйспределителя импульсов.

Источники информации. Принятые во внимание при экспертизе 1. свидетельство СССР 400891, кл. G 06 F 5/02, 1970.

1

4i

f(1l «1(2;

KtU)

Kil7)|H1{8)

Ti ГЗ ym

Авторы

Даты

1982-09-23—Публикация

1980-01-04—Подача