Изобретение относится к области радиоэлектроники и предназначено для дискретного изменения фазы сигнала в радиоэлектронных устройствах автоматики, измерительной техники, радионавигации.

Р1звестны фазовращатели дискретного типа, содержащие делители частоты, коммутатор, устройство управления и логнческие схемы «И и «ИЛИ.

Действие указанных фазовращателей основано на принциие нереключеиня нескольких импульсных иоследовательностей, сдвинутых по фазе друг относительно друга на требуемый днскрет изменения фазы. При необходимости получения малого дискрета изменення фазы приходится увеличивать число переключаемых последовательностей, что приводит к усложнению устройств формирования сдвинутых последовательностей, коммутнрующнх устройств и. следовательно, всего устройства.

В предлагаемом фазовращателе заранее не формируется весь набор переключаемых последовательностей. Формирование второй последовательности происходит только лищь при поступлении команды на изменение фазы сигнала па дискрет в ту илн иную сторону, что уменьщает число коммутируемых временных последовательностей, сокращает число 3).лементов коммутатора, уменьщает размеры всего устройства, что, в свою очередь, новыщает надежность. Это достигается благодаря следующим функцнональным связям.

. Выходы делителей частоты через логические схемы «П. соедннеиы со входами схемы «ИЛИ, выход которой является выходом фазовращате;гя. Вторые входы этих схем «1-1 подключены к выходал; переключаюн1его триггера, соединенным также со входами схем «И, включенных в цепн синхронизации одного делителя частотьгдругнм.

2) Вторые входы послед1И1х нз уномянутых схем «М соедпнепы попарно с соответствуюилими синхронизирующими выходами устройства управлеиия. При этол счетный вход иереключающего триггера соединен с переключающим выходо1 устройства управления, а выход синхронизации устройства управления соединен с выходом одного нз каскадов делителя частоты, вырабатывающего сигнал, соответствующнй требуемому фазовому сдвпгу.

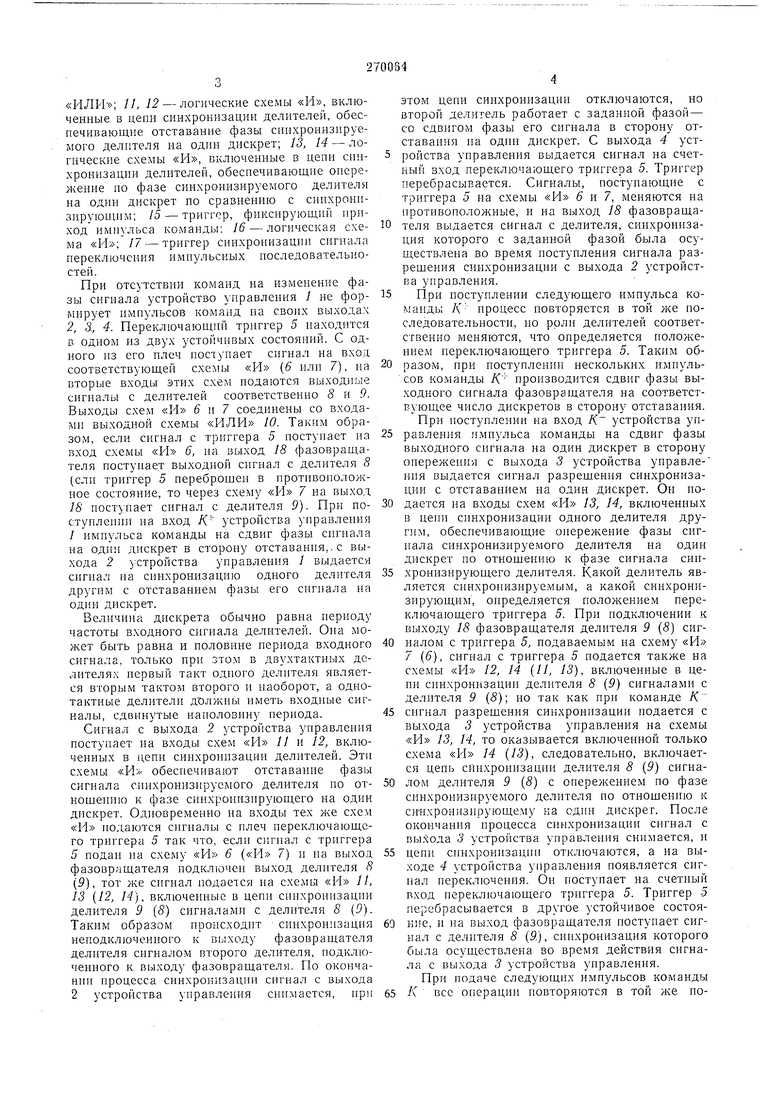

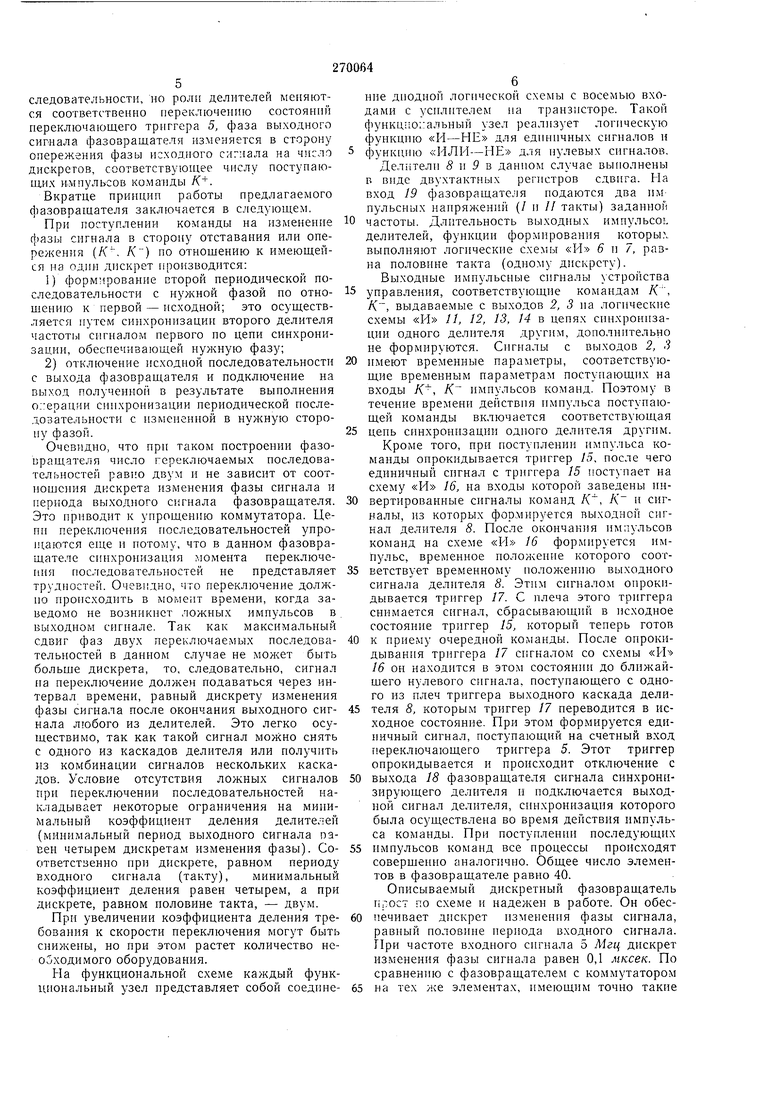

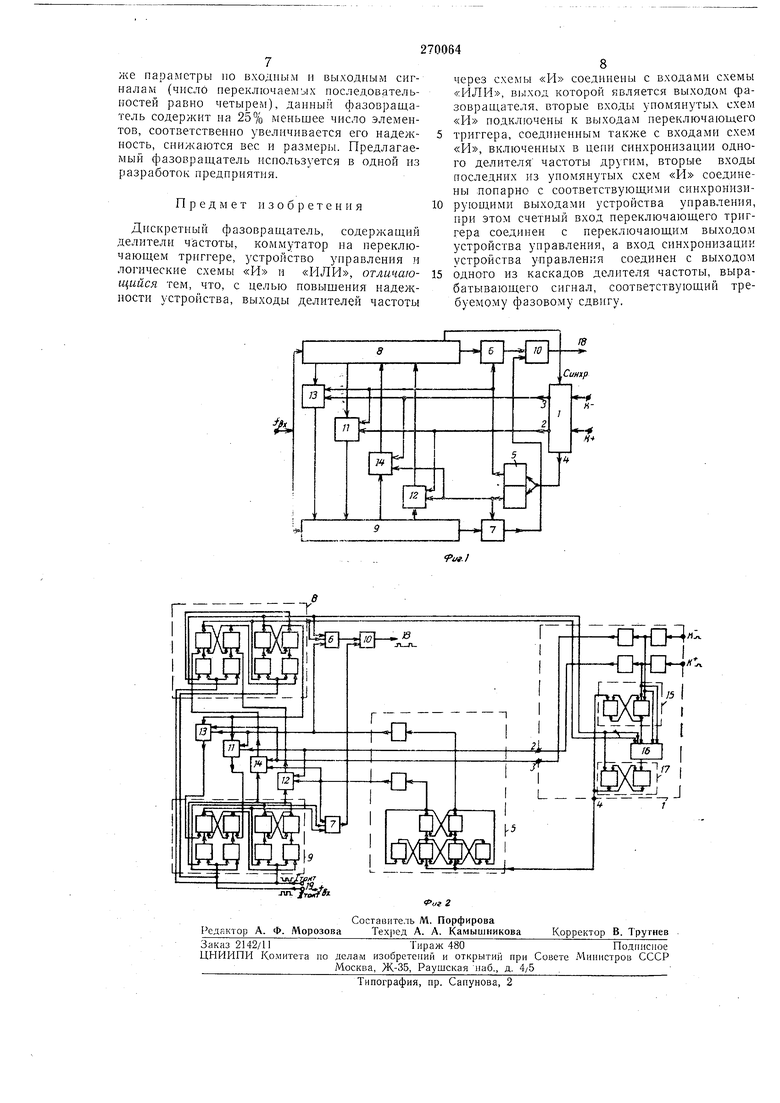

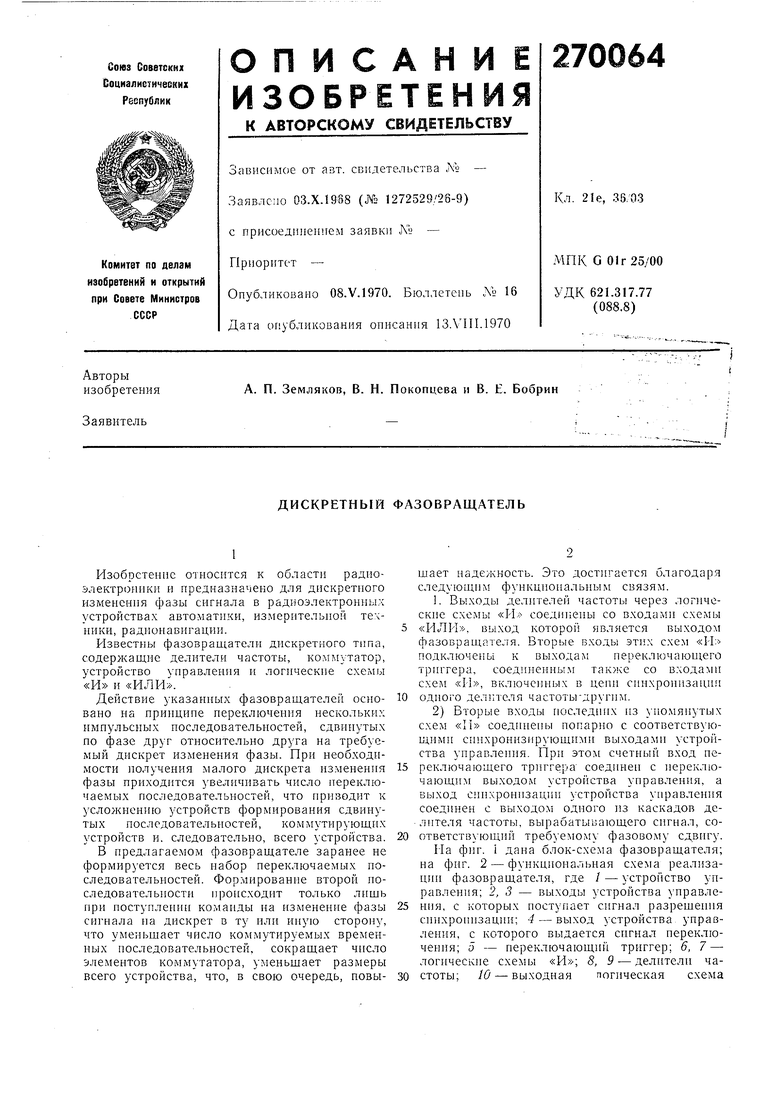

Па фиг. 1 дана блок-схема фазовращателя; на фиг. 2 - функциональная схема реализацнн фазовращателя, где / - устройство управления; 2, 3 - выходы устройства унравления, с которых иоступает сигнал разрещеиия синхронизации; 4-выход устройства управления, с которого выдается сигнал переключения; 5 - переключающнй триггер; 6, 7 - логнческне схемы 8, 9 - делнтели частоты; 10 - выходная логическая схема «Р1ЛИ- ; 11, 12 - логические схемы «И, включенные в цепи синхронизации делителей, обеспечивающие отставание фазы синхронизируемого делителя на один дискрет; 13, 14 - логические схемы «И, включенные в цепн сннхронизации делителей, обесиечиваюш,ие оиережение по фазе синхронизируемого делителя на один дискрет по сравнению с синхронизирующим; 15 - триггер, фиксирующий приходимпульса команды; 16 - логическая схема 17 - триггер синхронизации сигнала иереключения импульсных носледовательностей. При отсутствии команд на изменение фазы сигиала устройство управления 1 не формирует импульсов команд на своих выходах 2, 3., 4. Переключающий триггер 5 паходнтся в одном из двух устойчивых состояний. С одного из его нлеч поступает снгнал на вход соответствующей схемы «И (6 или 7), па вторые входы этих схем подаются выходные сигпалы с делителей соответственно 8 и 9. Выходы схем «И 6 и 7 соедипены со входамп выходной схемы «ИЛИ 10. Таким образом, если сигнал с триггера 5 поступает на вход схемы «И 6, на выход 18 фазовращателя поступает выходной снгнал с делителя 8 (ели триггер 5 нереброщен в противоположное состояние, то через схему «И 7 и а выход 18 поступает сигнал с делителя 9. При поступлении на вход К.- устройства уиравлеиия 1имиульса команды на сдвиг фазы сигиала на один дискрет в сторону отставания,, с выхода 2 устройства управления / выдается сигиал на синхронизацию одного делителя другим с отставаннем фазы его сигнала иа один дискрет. Велимииа дискрета обычно равиа иериоду частоты входного сигнала делителей. Она может быть равна и иоловиие иериода входного сигнала, только при этом в двухтактных делителях первый такт одпого делителя является вторым тактом второго и иаоборот, а однотактиые делители должны иметь входиые сигналы, сдвинутые наполовииу периода. Сигнал с выхода 2 устройства унравления поступает на входы схем «И 11 и 12, включенных в цепи сиихроинзации делителей. Эти схемы «И обесиечивают отставание фазы сигиала синхронизируемого делителя ио отнощепию к фазе синхронизирующего на один дискрет. Одновременно на входы тех же схем «И подаются сигналы с плеч переключающего триггера 5 так что, если сигнал с триггера 5 подап па схему «И 6 («И 7) и иа выход фазовращателя подключен выход делнтеля 8 (5), тот же сигнал подается иа схемы «И 11, 13 (12, 14), включенные в цепн сннхроиизации делителя 9 (8) сигналами с делителя 8 (9. Таким образом происходит синхронизация неподключенного к в ;1ходу фазовращателя делителя сигиалом второго делителя, подключенного к выходу фазовращателя. По окончанни процесса синхронизации сигнал с выхода этом цепи синхронизации отключаются, но второй делитель работает с заданной фазой- со сдвигом фазы его сигнала в сторону отставания иа один дискрет. С выхода 4 устройства уиравления выдается сигнал на счетный вход переключающего триггера 5. Триггер перебрасывается. Сигналы, ностунающие с триггера 5 на схемы «И 6 и 7, меняются на противоположные, и иа выход 18 фазовращателя выдается сигнал с делителя, синхронизация которого с заданной фазой была осуществлена во время ноступления сигнала разрещения синхронизации с выхода 2 устройства управления. При поступлении следующего импульса комаиды / процесс повторяется в той же последовательности, но роли делителей соответственно меняются, что определяется положением иереключающего триггера 5. Таким образом, ири поступлении нескольких импульсов команды }( производится сдвиг фазы выходного сигнала фазовращателя на соответствующее чнсло дискретов в сторону отставания. При поступлении на вход К устройства управления импульса команды на сдвиг фазы выходного сигнала на один дискрет в сторону выхода 3 устройства управлеопережения с ПИЯ выдается сигнал разрещеиия синхронизации с отставаиием на один дискрет. Он нодаетея на входы схем «И 13, 14, включенных в цепн сннхронизации одного делителя другим, обеспечивающие онережение фазы сигнала сннхроннзируемого делителя на один дискрет по отнощению к фазе сигнала сиихроннзирующего делителя. Какой делитель является сиихропизируемым, а какой синхронизирующим, онределяется положением переключающего триггера 5. При подключении к выходу 18 фазовращателя делителя 9 (8) сигналом с триггера 5, подаваемым на схему «И 7 (б), сигнал с триггера 5 нодается также на схемы «PI 12, 14 (11, 13), включенные в цепи синхронизации делителя 8 (9) сигналами с делителя 9 (8); но так как при команде К снгнал разрещения синхроиизации иодается с выхода 3 устройства управления на схемы «И 13, 14, то оказывается включенной только схема «И М (13), следовательно, включается цепь сипхроиизацни делителя 8 (9) сигналом делителя 9 (8) с опережением ио фазе синхронизируемого делителя по отнощенпю к синхронизирующему на один дискрет. После окончания процесса синхронизации сигнал с выхода 6 устройства управления снимается, и цеии сиихронизации отключаются, а на выходе 4 устройства управления ноявляется сигнал переключения. Оп поступает на счетный вход переключающего трнггера 5. Триггер 5 перебрасывается в другое устойчнвое состояК1 е, и па выход фазовращателя поступает сигнал с делителя 8 (и), сиихроиизация которого была осуществлена во время действия сигнала с выхода 3 устройства уиравления. следовательности, но роли делителей меняются соответственно переключению состояний переключающего триггера 5, фаза выходного сигнала фазовращателя изменяется в сторону опережения фазы исходного сигмала на число дискрегов, соответствуюн1,ее числу поступающих нмпульсов команды К. Вкратце принцип работы предлагаемого фазовращателя заключается в следующем. При поступлении команды на изменение фазы сигнала в сторону отставания или опережения (Л , К) по отношению к имеющейся на один дискрет 1 роизводится: 1)формирование второй периодической последовательности с нужной фазой по отношению к первой - исходной; это осуществляется путем синхроиизации второго делителя частоты сигналом первого но цепи синхронизации, обеспечивающей нужную фазу; 2)отключение исходной последовательности с выхода фазовращателя и подключение на выход полученной в результате выполнения о::ерации синхронизации периодической последовательности с измененной в нужную сторону фазой. Очевидно, что прп таком построении фазовращателя число переключаемых последовательностей равно двум и не зависит от соотнощения дискрета изменения фазы сигнала и периода выходного сигнала фазовращателя. Это ириводит к уирощению коммутатора. Цепи переключения иоследовательностей упро цаются еще и потому, что в данном фазовращателе спнхронизация момента переключения последовательностей не представляет трудностей. Очевидно, что переключение доллчпо происходить в момент времени, когда заведомо не возникнет ложных имнульсов в выходном сигнале. Так как максимальный сдвиг фаз двух переключаемых последовательностей в данном случае не может быть больше дискрета, то, следовательно, сигнал на переключение должен подаваться через интервал времени, равный дискрету изменения фазы сигнала после окончания выходного сигнала любого из делителей. Это легко осуществимо, так как такой сигнал можно снять с одного из каскадов делителя или получить из комбинации сигналов нескольких каскадов. Условие отсутствия ложных сигналов при переключении последовательностей накладывает некоторые ограничения на минимальный коэффициент деления делителей (минимальный период выходного сигнала павен четырем дискретам изменения фазы). Соответственно при дискрете, равном периоду входного сигнала (такту), минимальный коэффициент деления равен четырем, а при дискрете, равном половине такта, - двум. При увеличении коэффициента деления требования к скорости переключения могут быть снижены, но при этом растет количество нео5ходимого оборудования. ние диодной логической схемы с восемью входами с усилителем на транз 1сторе. Такой функц1;о;:альный узел реалнзует логическую функцию «И-НЕ для единичных сигналов и функцию «ИЛИ-НЕ для нулевых сигналов. Делители 5 и 9 в данном случае выполнены в виде двухтактных регистров сдвига. На вход 19 фазовращателя иодаются два им пульсных нанряжени.й (/ и // такты) заданной частоты. Длительность выходных импульсоь делителей, функцин формирования которых выполняют логические схелия «И 6 и 7, равна половине такта (одному дискрету). Выходиые импульсные сигналы устройства управления, соответствующие командам /С, К., выдаваемые с выходов 2, 3 на логические схемы «И 11, 12, 13, 14 в цепях синхронизации одного делителя другим, дополнительно не формируются. Сигналы с выходов 2, 3 имеют временные параметры, соответствующие временным параметрам поступающих на входы , К импульсов команд. Поэтому в течение времени действия импульса поступающей команды включается соответствующая цень синхронизации одного делителя другим. Кроме того, при поступлении импульса команды опрокидывается триггер /5, после чего единичный сигнал с триггера 15 поступает на схему «И 16, на входы которой заведены инвертированные снгналы команд /, Л и сигналы, из которых форлшруется выходной сигнал делителя 8. После окончания имлульсов команд на схеме «И 16 формнруется нмпульс, временное нoлoлveннe которого соответствует временному иолол-сению выходного сигнала делителя 8. Этим сигналом опрокидывается триггер 17. С плеча этого триггера снимается сигнал, сбрасывающий в исходное состояние 15, который теперь готов к приему очередной команды. После опрокидывания триггера /7 сигналом со схемы «И 16 он находится в этом состоянни до ближайщего нулевого сигнала, поступающего с одного из плеч триггера выходного каскада делителя 8, которым триггер 17 переводится в исходное состояние. При этом формируется единичный сигнал, поступающий на счетный вход переключающего триггера 5. Этот триггер оирокидывается и происходит отключение с выхода 18 фазовращателя сигнала синхронизирующего делителя и иодключается выходной сигнал делителя, синхронизация которого была осуществлена во время действия имиульса команды. При поступлении последующих импульсов команд все процессы происходят совершенно аналогично. Общее число элементов в фазовращателе равно 40. Онисываемый дискретный фазовращатель прост по схеме и надежен в работе. Он обес 1ечивает дискрет изменения фазы сигнала, равный половине нериода входного сигнала. При частоте входного сигнала 5 Мгц дискрет изменения фазы сигнала равен 0,1 мксек. По сравнению с фазовращателем с коммутатором же параметры по входным и выходным сигналам (число переключаемых последовательностей равно четырем), данный фазовращатель содержит на 25% меньшее число элементов, соответственно увеличивается его надежность, снижаются вес и размеры. Предлагаемый фазоврагцатель используется в одной из разработок предприятия. Предмет изобретения Дискретный фазовращатель, содержащий делители частоты, коммутатор па переключающем триггере, устройство управления и логические схемы «И и «ПЛИ, отличающийся тем, что, с целью новыщения надежности устройства, выходы делителей частоты через схемы «И соединены с входами схемы «ИЛИ, которой является выходом фазовращателя, вторые входы упомянутых схем «Р1 подключены к выходам переключающего триггера, соединенным также с входами схем «И, включенных в цепи синхронизации одного делителя частоты другим, вторые входы последних из упомянутых схем «И соединены попарно с соответствующими синхронизирующими выходами устройства управления, при этом счетный вход переключающего триггера соединен с переключающим выходом устройства управления, а вход синхронизации устройства управления соединен с выходом одного из каскадов делителя частоты, вырабатывающего сигнал, соответствующий требуемому фазовому сдвигу.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДИСКРЕТНОГО ИЗМЕНЕНИЯ ФАЗЫСИГНАЛА | 1971 |

|

SU306559A1 |

| Устройство для управления инвертором | 1978 |

|

SU764094A1 |

| УСТРОЙСТВО ДИСКРЕТНОГО ИЗМЕНЕНИЯ ФАЗЫ СИГНАЛА | 1969 |

|

SU254650A1 |

| Многоканальная система счета фотонов | 1988 |

|

SU1573352A1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| Фазовращатель | 1981 |

|

SU993150A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Устройство для управления инвертором | 1980 |

|

SU938355A1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ АППАРАТУРЫ ПРИЕМА и ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1971 |

|

SU308533A1 |

| ВПТБ | 1973 |

|

SU408355A1 |

Даты

1970-01-01—Публикация