Известное устройство для синхронизации аппаратуры приема и обработки дискретной информации без непосредственного воздействия на задающий генератор содержит управляемый делитель частоты следования импульсов, фазовый дискриминатор и источник синхронизирующих импульсов, подключенный к первому входу фазового дискриминатора, выходы которого подключены к реверсивному счетчику.

Цель изобретения - уменьшение рабочей тактовой частоты и повышение точности синфазирования синхронизируемых импульсных последовательностей.

Для этого в предлагаемом устройстве на выходе управляемого делителя включена линия задержки на время, равное периоду следования импульсов задающего генератора, отводы которой подсоединены к первым входам схем «И, вторые входы которых подключены к реверсивному счетчику через дешифратор, а выходы схем «И через схему «ИЛИ соединены со вторым входом фазового дискриминатора, при этом с выходов дешифратора поданы импульсы на управляемый делитель частоты для изменения его коэффициента деления при переходе реверсивного счетчика из состояния, соответствующего нахождению импульса задающего генератора на одном из крайних отводов линии задержки, в состояние,

соответствующее нахождению импульса задающего генератора на другом крайнем ее отводе.

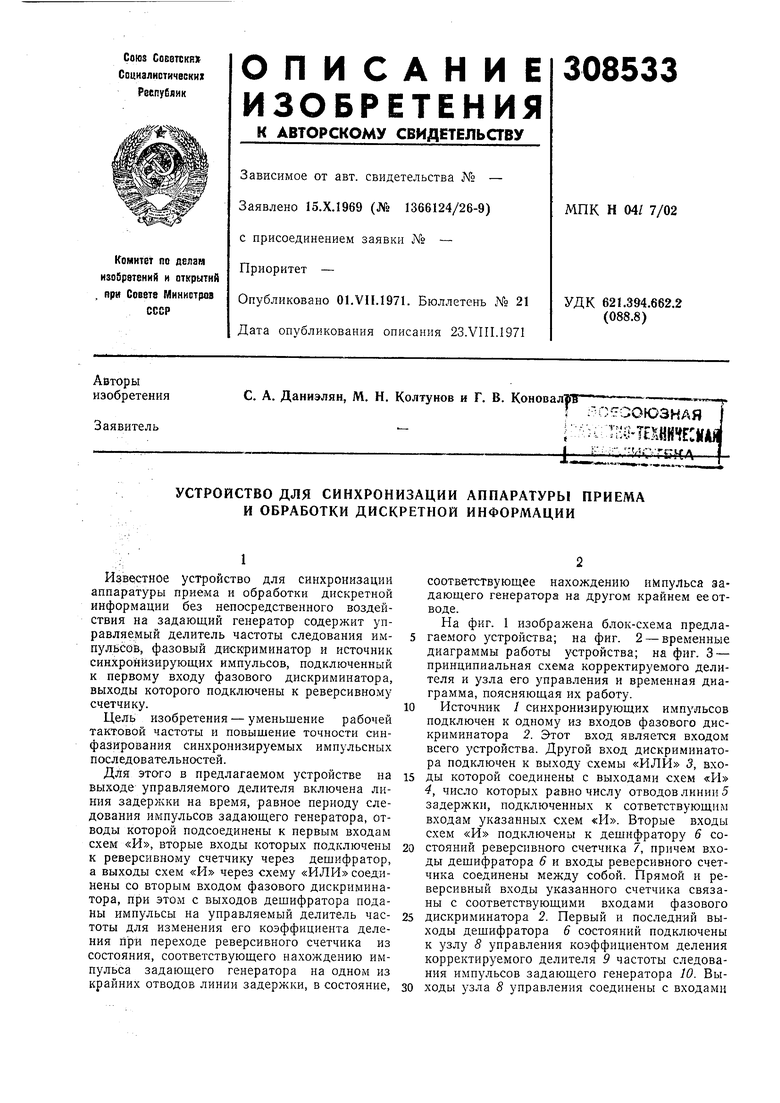

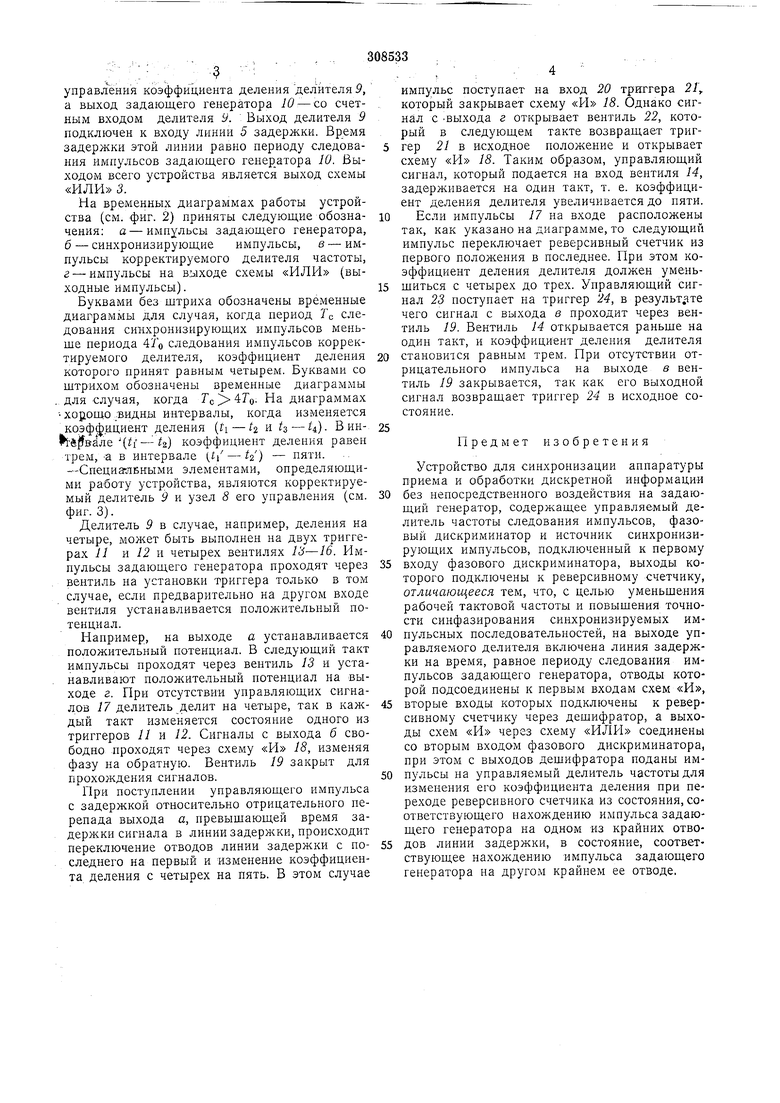

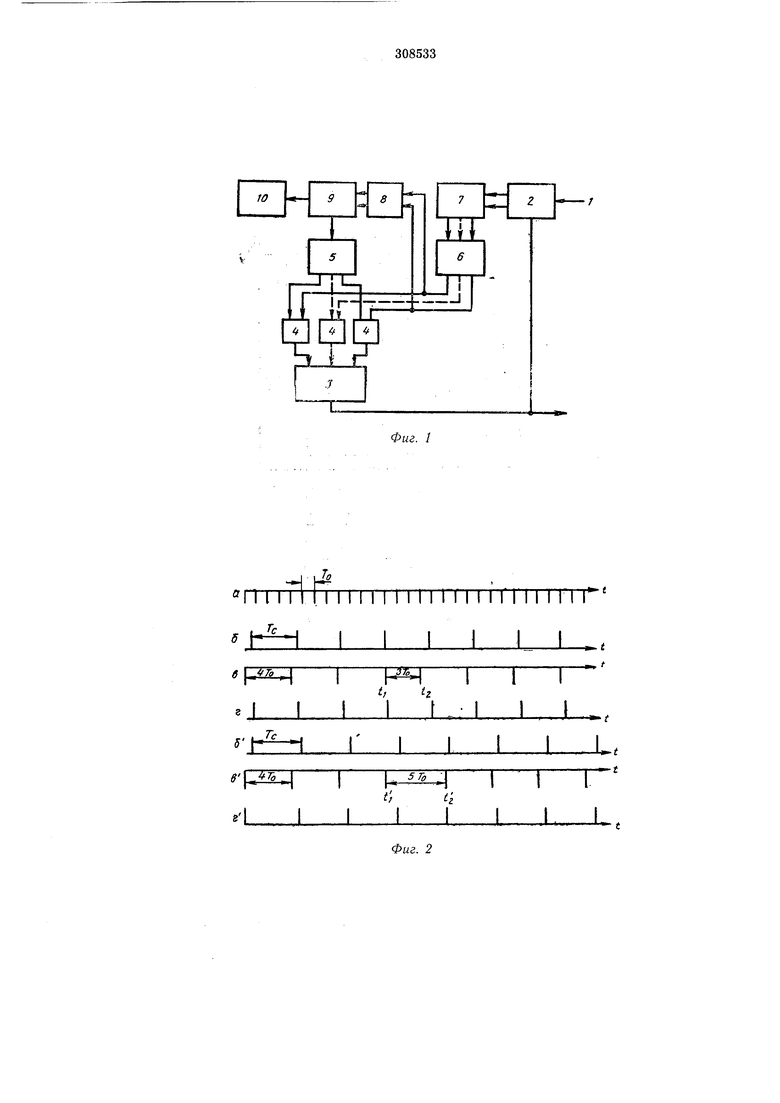

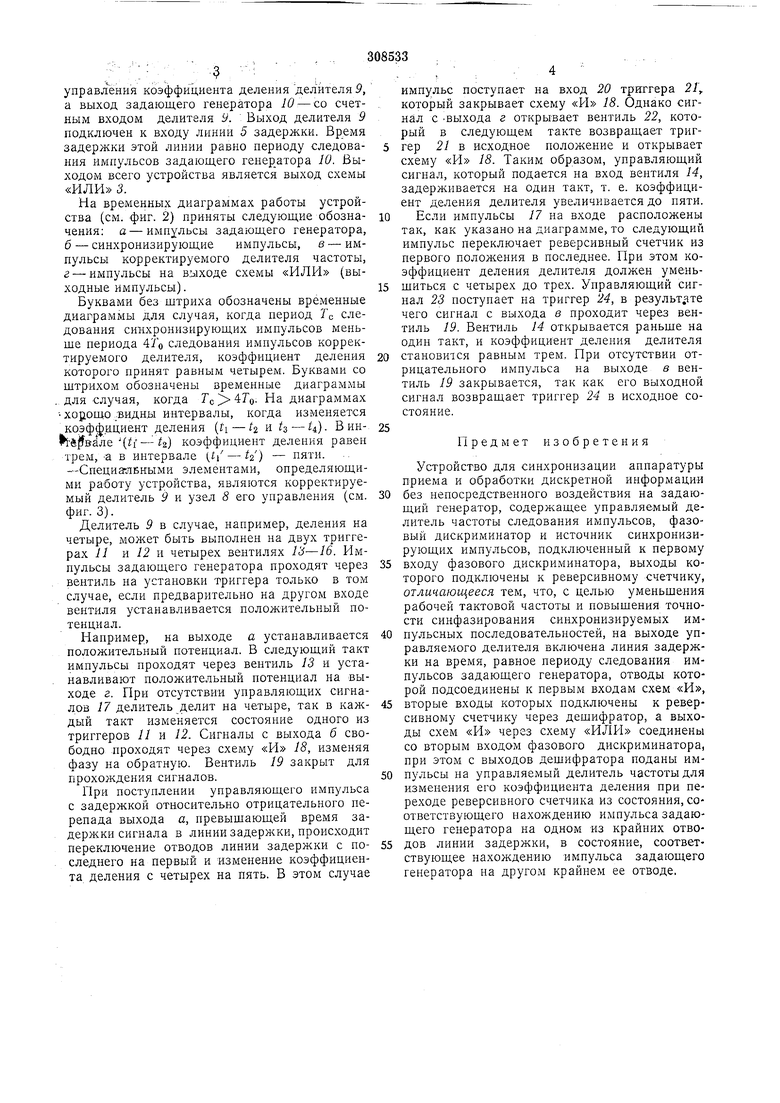

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы у-стройства; на фиг. 3 - принципиальная схема корректируемого делителя и узла его управления и временная диаграмма, поясняющая их работу.

Источник 1 синхронизирующих импульсов подключен к одному из входов фазового дискриминатора 2. Этот вход является входом всего устройства. Другой вход дискриминатора подключен к выходу схемы «ИЛИ 3, входы которой соединены с выходад и схем «И 4, число которых равно числу отводов линии 5 задержки, подключенных к сответствующим входам указанных схем «И. Вторые входы схем «И подключены к дешифратору 6 состояний реверсивного счетчика 7, причем входы дешифратора 6 и входы реверсивного счетчика соединены между собой. Прямой и реверсивный входы указанного счетчика связаны с соответствующими входами фазового дискриминатора 2. Первый и последний выходы дешифратора 6 состояний подключены к узлу 8 управления коэффициентом деления корректируемого делителя 9 частоты следования импульсов задающего генератора 10. Выходы узла 8 управления соединены с входами ; ;,;,;: - ; ; ; управления коэффициента деления делителя Р, а выход задающего генератора 10 со счетным входом делителя У. Выход делителя 9 подключен к входу линии 5 задержки. Время задержки этой линии равно периоду следования импульсов задающего генер атора 10. Выходом всего устройства является выход схемы «ИЛИ 3. На временных диаграммах работы устройства (см. фиг. 2) приняты следующие обозначения: а-импульсы задающего генератора, б - синхронизирующие импульсы, в - импульсы корректируемого делителя частоты, 2 -импульсы на выходе схемы «ИЛИ (выходные импульсы). Буквами без штриха обозначены временные диаграммы для случая, когда период 7с следования синхронизирующих импульсов меньще периода 1 следования импульсов корректируемого делителя, коэффициент деления которого принят равным четырем. Буквами со штрихом обозначены временные диаграммы .для случая, когда Гс 4Го. На диаграммах хорющо .видны интервалы, когда изменяется коэф(ициент деления (fi - t и tz - t). В ин Иё вйле(if- 2) коэффициент деления равен трем, -а в интервале (.г/ - - пяти. --Специа-лБными элементами, определяющими работу устройства, являются корректируемый делитель 9 и узел 8 его управления (см. фиг. 3). Делитель 9 в случае, например, деления на четыре, может быть выполнен на двух триггерах 11 } 12 II четырех вентилях 13-16. Импульсы задающего генератора проходят через вентиль на установки триггера только в том случае, если предварительно на другом входе вентиля устанавливается положительный потенциал. Например, на выходе а устанавливается положительный потенциал. В следующий такт импульсы проходят через вентиль 13 и устанавливают положительный потенциал на выходе г. При отсутствии управляющих сигналов 17 делитель делит на четыре, так в каждый такт изменяется состояние одного из триггеров 11 и 12. Сигналы с выхода б свободно проходят через схему «И 18, изменяя фазу на обратную. Вентиль 19 закрыт для прохождения сигналов. При поступлении управляющего импульса с задержкой относительно отрицательного перепада выхода а, превышающей время задержки сигнала в линии задержки, происходит переключение отводов линии задержки с последнего на первый и изменение коэффициента деления с четырех на пять. В этом случае . . - 4 импульс поступает на вход 20 триггера 21 который закрывает схему «П 18. Однако сигнал с Выхода г открывает вентиль 22, который в следующем такте возвращает триггер 21 в исходное положение и открывает схему «И 18. Таким образом, управляющий сигнал, который подается на вход вентиля 14, задерживается на один такт, т. е. коэффициент деления делителя увеличивается до пяти. Если импульсы 17 на входе расположены так, как указано на диаграмме, то следующий импульс переключает реверсивный счетчик из первого положения в последнее. При этом коэффициент деления делителя должен уменьшиться с четырех до трех. Управляющий сигнал 23 поступает на триггер 24, в результ.чте чего сигнал с выхода в проходит через вентиль 19. Вентиль 14 открывается раньще на один такт, и коэффициент деления делителя становится равным трем. При отсутствии отрицательного импульса на выходе в вентиль 19 закрывается, так как его выходной сигнал возвращает триггер 24 в исходное состояние. Предмет изобретения Устройство для синхронизации аппаратуры приема и обработки дискретной информации без непосредственного воздействия на задающий генератор, содержащее управляемый делитель частоты следования импульсов, фазовый дискриминатор и источник синхронизирующих импульсов, подключенный к первому входу фазового дискриминатора, выходы которого подключены к реверсивному счетчику, отличающееся тем, что, с целью уменьшения рабочей тактовой частоты и повышения точности синфазирования синхронизируемых импульсных последовательностей, на выходе управляемого делителя включена линия задержки на время, равное периоду следования импульсов задающего генератора, отводы которой подсоединены к первым входам схем «И, вторые входы которых подключены к реверсивному счетчику через дешифратор, а выходы схем «И через схему «ИЛИ соединены со вторым входом фазового дискриминатора, при этом с выходов дешифратора поданы импульсы на управляемый делитель частоты для изменения его коэффициента деления при переходе реверсивного счетчика из состояния, соответствующего нахождению импульса задающего генератора на одном из крайних отводов линии задержки, в состояние, соответствующее нахождению импульса задающего генератора на другом крайне.м ее отводе.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1984 |

|

SU1215185A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

°ггп

МП I I I I 1 I I I I I I Ml 1ТП

I I I I I I

h I I

elIiIt - Ii1

J±

HM I I 1 I

г IIIIIiI

t

t, if

JL.

t f,

Фиг. 2

ГТТГТТIII1IIITTIIIII1II

Даты

1971-01-01—Публикация