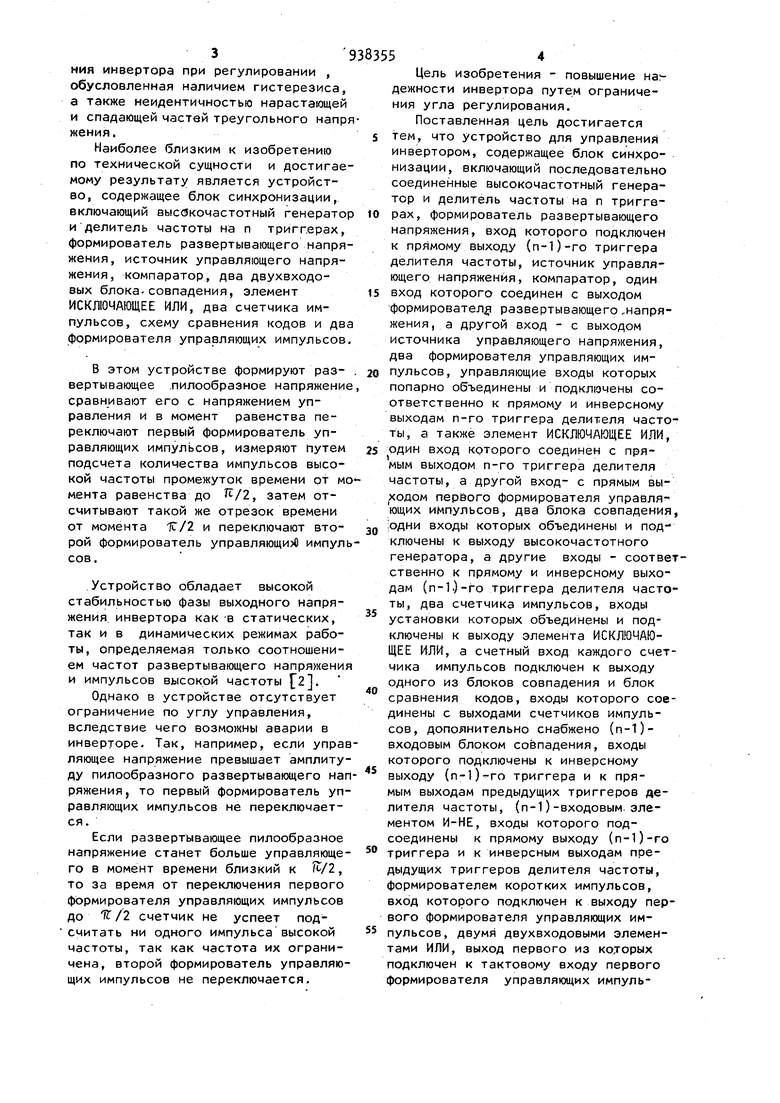

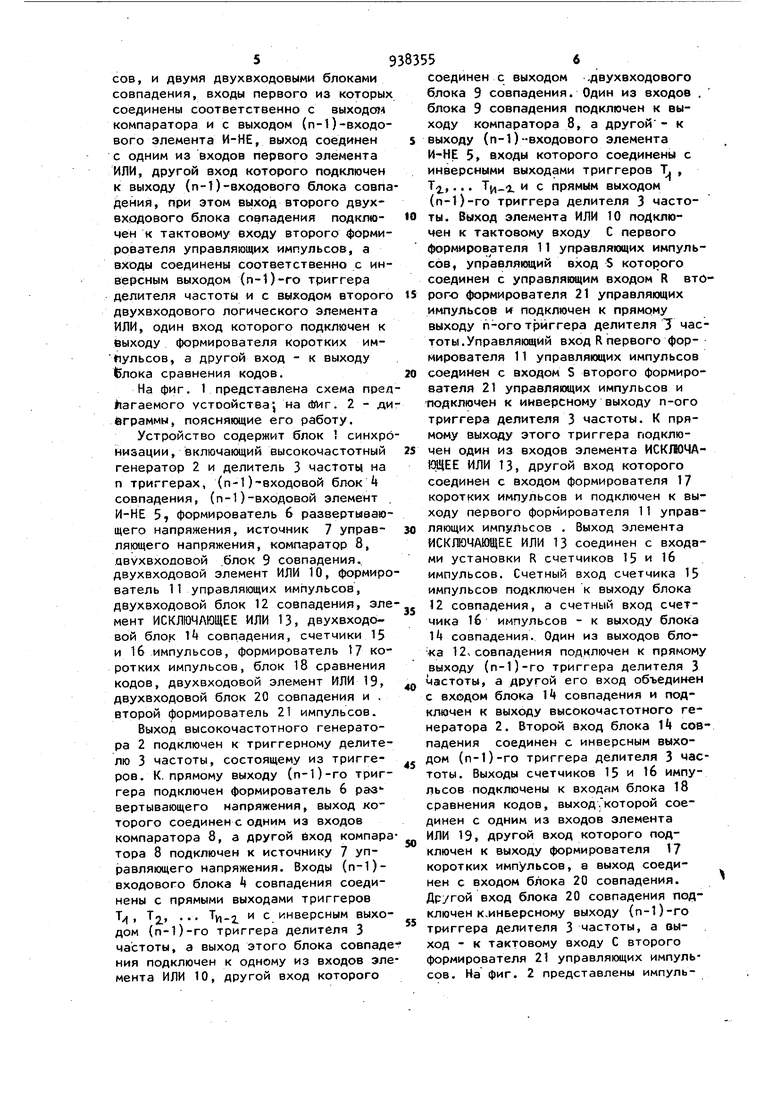

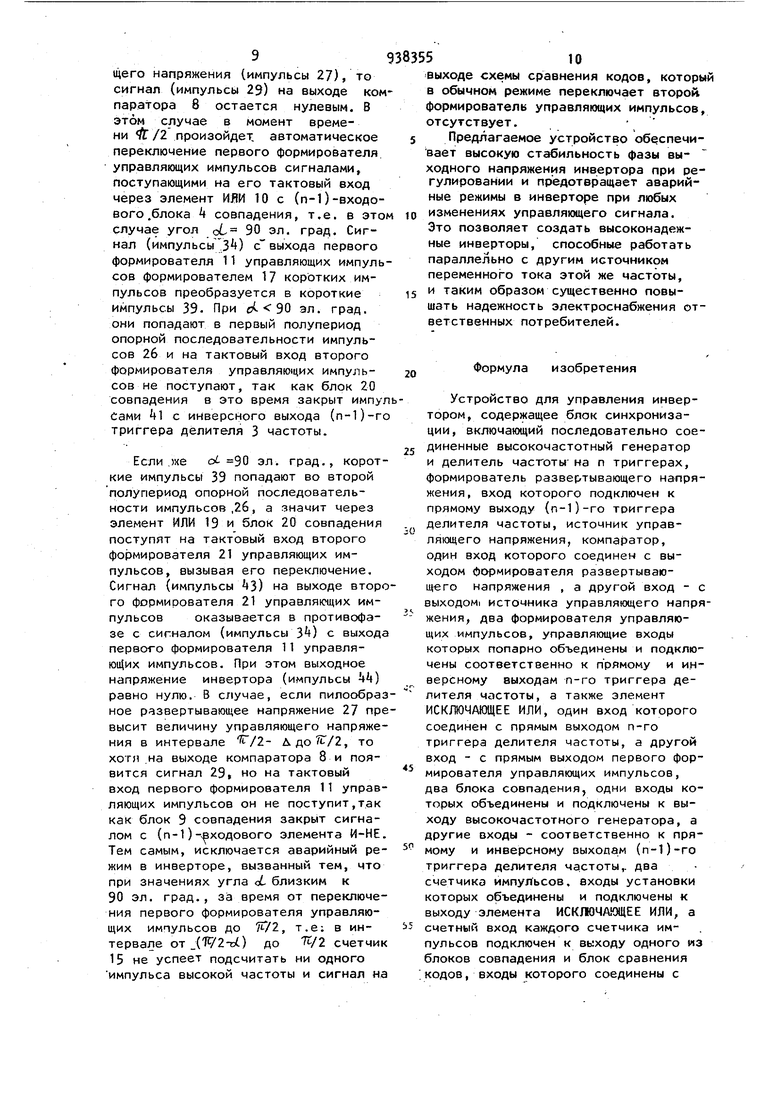

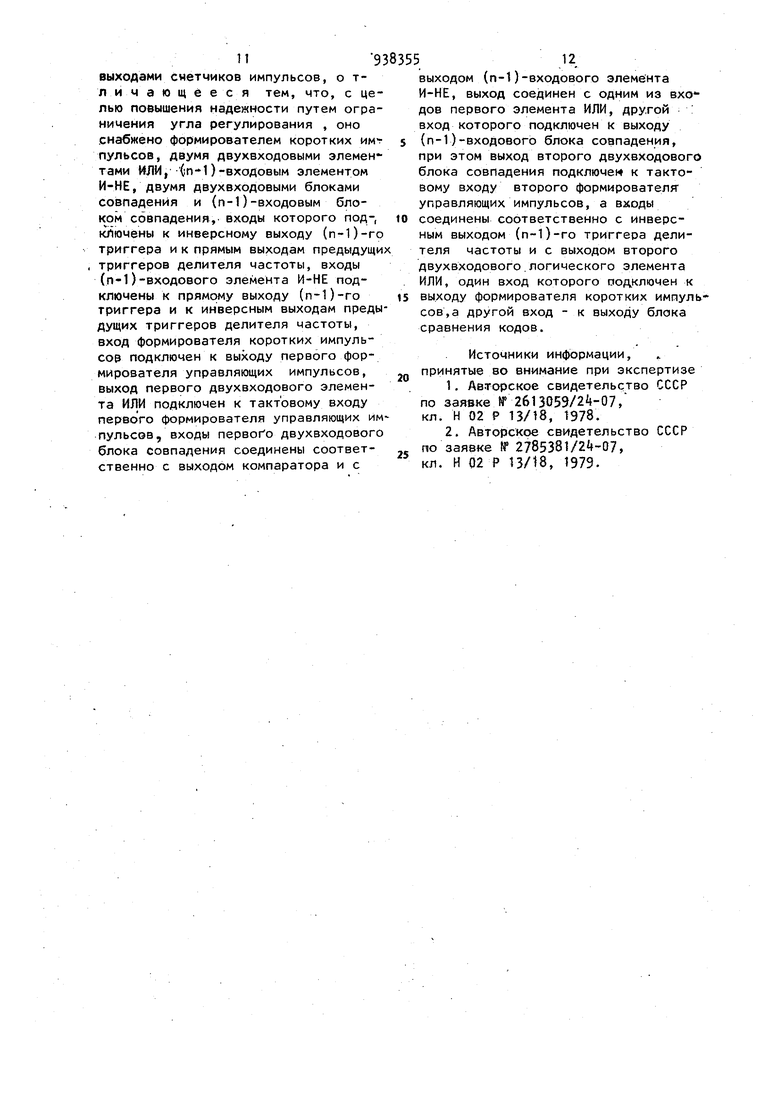

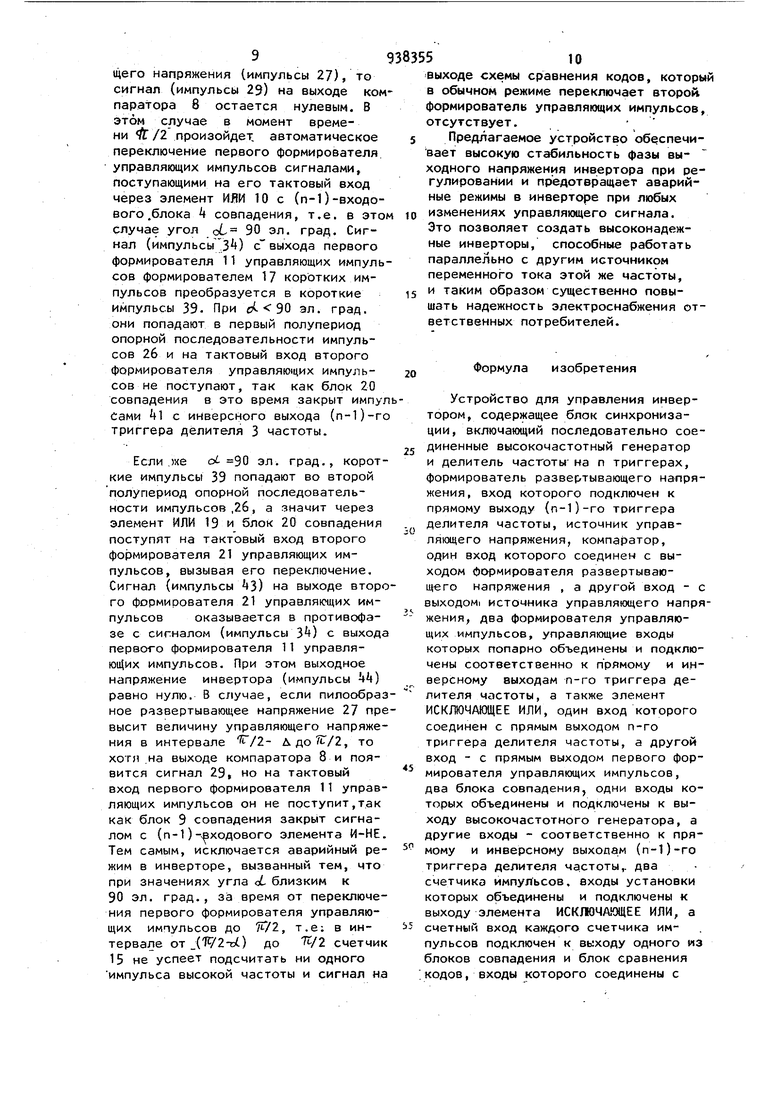

Изобретение относится к преобра зовательной технике, а именно к сие темам управления вентильными преобразователями, и может быть использовано для управления автономными инверторами напряжения. Известно устройство для управления инвертором, содержащее задающий генератор прямоугольных импульсов, делитель на два, формирователь треугольного напряжения, сравнивающее устройство, два формирователя коротких импульсов, две схемы ИЛИ и два синхронизируемых формировател выходных импульсов. В этом устройстве формируют из синхронизирующего напряжения треугольное, сравнивают его с напряжением управления, формируя таким образом регулируемые по ширине импульсы, ho перед нему фронту которых запускают первый, а по заднему фронту - второй .формирователь управляющих импульсов Таким образом, формируются две последовательности управляющих импульсов, одна из которых сдвинута в сторону отставания на угол, определяемый величиной напряжения управления, а другая сдвинута на такой же угол в сторону опережения. В результате . фаза выходного напряжения инвертора остаётся неизменной. Если даже напряжение управления превышает амплитуду треугольного-напряжения, то формирователь выходных импульсов запускается сигналами от формирователя коротких импульсов ввиду чего исключаются аварии в инверторе. Устройство ограничивает максимагьный и минимальный углы регулиробания в пределах 0-180 эл. град, в результате чего повышается надежность работы инвертора 1 . Недостаток устройства - низкая стабильность фазы выходного напряже39мия инвертора при регулировании , обусловленная наличием гистерезиса, а также неидентичностью нарастающей и спадающей частей треугольного напря жения. Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство, содержащее блок синхронизации, включающий высокочастотный генератор и делитель частоты на п триггерах, формирователь развертывающего напряжения, источник управляющего напряжения, компаратор, два двухвходовых блока-совпадения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два счетчика импульсов, схему сравнения кодов и два формирователя управляющих импульсов. В этом устройстве формируют развертывающее .пилообразное напряжение сравнивают его с напряжением управления и в момент равенства переключают первый формирователь управляющих импульсов, измеряют путем подсчета количества импульсов высокой частоты промежуток времени от мо мента равенства до Tt/2, затем отсчитывают такой же отрезок времени от момента и переключают второй формирователь управляющими импуль сов. Устройство обладает высокой стабильностью фазы выходного напряжения, инвертора как в статических, так и в динамических режимах работы, определяемая только соотношением частот развертывающего напряжения и импульсов высокой частоты f2. Однако в устройстве отсутствует ограничение по углу управления, вследствие чего возможны аварии в инверторе. Так, например, если управ ляющее напряжение превышает амплитуду пилообразного развертывающего нап ряжения, то первый формирователь управляющих импульсов не переключается. Если развертывающее пилообразное напряжение станет больше управляющего в момент времени близкий к /2, то за время от переключения первого формирователя управляющих импульсов до /г:/2 счетчик не успеет подсчитать ни одного импульса высокой частоты, так как частота их ограничена, второй формирователь управляющих импульсов не переключается. Цель изобретения - повышение нa дежности инвертора путем ограничения угла регулирования. Поставленная цель достигается тем, что устройство для управления инвертором, содержащее блок синхронизации, включающий последовательно соединенные высокочастотный генератор и делитель частоты на п триггерах, формирователь развертывающего напряжения, вход которого подключен к прямому выходу (n-l)-ro триггера делителя частоты, источник управляющего напряжения, компаратор, один вход которого соединен с выходом формирователе развертывающего ,напряжения, а другой вход - с выходом источника управляющего напряжения, два формирователя управляющих импульсов, управляющие входы которых попарно объединены и подключены соответственно к прямому и инверсному выходам п-го триггера делителя частоты, а также элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, ОДИН вход которого соединен с прямым выходом п-го триггера делителя частоты, а другой вход- с прямым выходом первого формирователя управляющих импульсов, два блока совпадения, ;одни входы которых объединены и подключены к выходу высокочастотного генератора, а другие входы - соответственно к прямому и инверсному выходам (п-1.)-го триггера делителя частоты, два счетчика импульсов, входы установки которых объединены и подключены к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а счетный вход каждого счетчика импульсов подключен к выходу одного из блоков совпадения и блок сравнения кодов, входы которого соединены с выходами счетчиков импульсов, дополнительно снабжено (п-1)входовым блоком совпадения, входы которого подключены к инверсному выходу {п-1) триггера и к прямым выходам предыдущих триггеров делителя частоты, (п-1)-входовым элементом И-НЕ, входы которого подсоединены к прямому выходу (п-1)-го триггера и к инверсным выходам предыдущих триггеров делителя частоты, формирователем коротких импульсов, вход которого подключен к выходу первого формирователя управляющих импульсов, двумя двухвходовыми элементами ИЛИ, выход первого из которых подключен к тактовому входу первого формирователя управляющих импульсов, и двумя двухвходовыми блоками совпадения, входы первого из которых соединены соответственно с выходо - компаратора и с выходом {п-1)-входового элемента И-НЕ, выход соединен с одним из входов первого элемента ИЛИ, другой вход которого подключен к выходу (п-1)-входового блока совпа дения, при этом выход второго двухвходового блока совпадения подключен к тактовому входу второго формирователя управляющих импульсов, а входы соединены соответственно с инверсным выходом {п-1)-го триггера делителя частоты и с выходом второго двухвходового логического элемента ИЛИ, один вход которого подключен к выходу формирователя коротких имлульсов, а другой вход - к выходу сравнения кодов. На фиг, 1 представлена схема пред йагаемого устоойства, на dJHr, 2 - ди аграммы, поясняющие его работу. Устройство содержит блок 1 синхро низации , включающий высокочастотный генератор 2 и делитель 3 частоты на п триггерах, (п-1)-входовой блок А совпадения, (п-1)-входовой элемент И-НЕ 5, формирователь 6 развертывающего напряжения, источник 7 управляющего напряжения, компаратор 8, явухвхоповой .блок 9 совпадения., двухвходовой элемент ИЛИ 10, формиро ватель 11 управляющих импульсов, двухвходовой блок 12 совпадения, эле мент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, двухвходовой блок t совпадения, счетчики 15 и 16 импульсов, формирователь 17 коротких импульсов, блок 18 сравнения кодов, двухвходовой элемент ИЛИ 19, двухвходовой блок 20 совпадения и . второй формирователь 21 импульсов. Выход высокочастотного генератора 2 подключен к триггерному делителю 3 частоты, состоящему из триггеров. К. прямому выходу (n-l)-ro триггера подключен формирователь 6 развертывающего напряжения, выход которого соединен с одним из входов компаратора 8, а другой йход компара тора 8 подключен к источнику 7 управляющего напряжения. Входы (п-1)входового блока k совпадения соединены с прямыми выходами триггеров Ty,ji и с инверсным выхоЧ 2. ; дом {п-1)-го триггера делителя 3 частоты, а выход этого блока совпаде ния подключен к одному из входов эле мента ИЛИ 10, другой вход которого 56 соединен с выходом .двухвходового блока 9 совпадения. Один из входов блока 9 совпадения подключен к выходу компаратора 8, а другой- к выходу (п-1)--входового элемента И-НЕ 5, входы которого соединены с инверсными выходами триггеров Т.,... Tj.-j. и с прямым выходом (п-О-го триггера делителя 3 частоты. Выход элемента ИЛИ 10 подключен к тактовому входу С первого формирователя 11 управляющих импульсов, управляющий вход S которого соединен с управляющим входом R второго формирователя 21 управляющих импульсов и подключен к прямому выходу п-ого триггера делителя Т частоты. Управляющий входRпервого формирователя 11 управляющих импульсов соединен с входом S второго формирователя 21 управляющих импульсов и подключен к инверсному выходу л-ого триггера делителя 3 частоты. К прямому выходу этого триггера подключен один из входов элемента ИСКЛОЧАЮЩЕЕ ИЛИ 13, другой вход которого соединен с входом формирователя 17 коротких импульсов и подключен к выходу первого формирователя 11 управляющих импульсов , Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 соединен с входами установки R счетчиков 15 и 16 импульсов. Счетный вход счетчика 15 импульсов подключен к выходу блока 12 совпадения, а счетный вход счетчика 16 импульсов - к выходу блока 14 совпадения. Один из выходов блока 12 совпадения подключен к прямому выходу (п-1)-го триггера делителя 3 частоты, а другой его вход объединен с входом блока k совпадения и подключен к выходу высокочастотного генератора 2. Второй вход блока совпадения соединен с инверсным выходом (п-1)-го триггера делителя 3 частоты. Выходы счетчиков 15 и 1б импульсов подключены к входам блока 18 сравнения кодов, выход .которой соединен с одним из входов элемента ИЛИ 19, другой вход которого подключен к выходу формирователя V7 коротких импульсов, а выход соединен с входом блока 20 совпадения. Другой вход блока 20 совпадения подключен к.инверсному выходу (п-1)-го триггера делителя 3 частоты, а выход - к тактовому входу С второго формирователя 21 управляющих импульсов. На фиг. 2 представлены импульсы 22- на выходах элементов схемы. Устройство работает следующим об разом. Импульсы высокой частоты 22 от в сокочастотного генератора 2 поступа ют на вход делителя 3 частоты, сост ящего из п триггеров. При этом на прямом выходе первого триггера делителя 3 частоты появляются импульс 3, на прямом выходе (п-2)-го триггера делителя частоты - импульсы на прямом выходе (п-О-го триггера делителя частоты - импульсы 25, а на прямом выходе п-г6 триггера де лителя частоты появляются импульсы 2б с выходной частотой инвертора. Импульсы 25 поступают на вход форми рователя 6 развертывающего напряжения, с выхода которого снимается пилообразное развертывающее напряже ние (импульсы 27), которое поступае на вход компаратора 8. На другой вход компаратора поступает управляю щее напряжение (импульсы 28) с источника 7 управляющего напряжения. Когда пилообразное напряжение (импульсы 27) становится больше управляющего напряжения (импульсы 28) на выходе компаратора 8 появляются импульсы 29 которые поступанцт на вход блока 9 совпадения. На другой вход этого блока совпадения подается импульс 30 с элемента И-НЕ 5, ввиду чего запрещается прохождение импульсов 29 с компаратора на выход блока 9 совпадения в интервале от /2 - Д до . Сигнал с выход блока 9 совпадения поступает на оди из входов элемента ИЛИ 10, на друго вход которого подается сигнал 32 с выхода (п-1)-входового блокад совпадения. Импульсы 33 с выхода элемента ИЛИ 10 поступают на тактовый вход С первого формирователя 11 управляющих импульсов. В результате на его прямом выходе появляются им пульсы 3, сдвинутые относительно опорной последовательности импульсов 2б в сторону отставания на угол cL , определяемый величиной управляющего напряжения. На вход блок 12 совпадения поступают импульсы 25 с прямого вь1хода (п-1)-го триггера делителя частоты и импульсы 22 с вы сокочастотного генератора 2.В результате с выхода блока 12 совпаден на счетный вход С счетчика 15 импульсов поступают пачки импульсов высокой частоты в первой половине каждого полупериода. Аналогично с выхода блока 1 совпадения на счетный вход счетчика 16 Импульсов поступают пачки импульсов высокой частоты во второй половине каждого полупериода опорно- го сигнала (импульсы 26). На один вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 поступает опорная последовательность ИМПУЛЬСОВ 26 с делителя частоты, на другой вход - сигналы с формирователя 11 управляющих импульсЪв. Если эти сигналы различны, то с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 на входы установки R счетчиков 15 и 16 поступает сигнал (импульсы 37) логической 1, счетчики удерживаются в нулевом состоянии.Как только первый формирователь управляющих импульсов переключится и сигнал (импульсы 3) на его выходе станет синфазен с опорнь1м сигналом (импульсы 2б), сигнал (импульсы 37) на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 примет значение логического- О и счетчик 15 начнет подсчитывать импульсы 35, поступающие на его счетный вход. В момент времени 1с/2 прекращается поступление импульсов 35 на счетный вход счетчика 15, а счетчик 16 начинает, в свою очередь,заполняться импульсами Зб, поступающими на его счетный вход во второй половине каждого полупериода опорного сигнала (импульсы 26).Как только в счетчик 16 запишется такое же количество импульсов высокой частоты, какое записано в счетчик 15 за время 7E/2-o , на выходе блока 18 сравнения кодов появится сигнал (импульсы 38), поступающий через элемент ИЛИ 19 и блок 20 совпадения на тактовый вход С второго формирователя 21 управляющих импульсов. В результате на выходе второго формирователя 21 управляющих импульсов появится сигнал (импульсь 3), сдвинутый относительно опорной последовательности импульсов 26 на тот же самый угол с{ ,что и сигнал (импульсы 3) с первого формирователя 11 управляющих импульсов, но только в сторону опережения. Таким образом, фаза выходного напряжения инвертора (импульсы kk) не/изменяется в процессе регулирования. Если управляющее напряжение (импульсы 28) окажется больше, чем амплитуда пилообразного развертывающего напряжения (импульсы 27), то сигнал (импульсы 29) на выходе ком паратора 8 остается нулевым, В этом случае в момент времени /2 произойдет автоматическое переключение первого формирователя управляющих импульсов сигналами, поступающими на его тактовый вход через элемент ИЙИ 10 с (п-1)-входового .блока 4 совпадения, т.е. в это случае угол pL 90 эл. град. Сигнал (импульсыЗ) свыхода первого формирователя 11 управляющих импуль сов формирователем 17 коротких импульсов преобразуется в короткие импульсы 39. При с 90 эл. град, они попадают в первый полупериод опорной последовательности импульсов 2б и на тактовый вход второго формирователя управляющих импульсов не поступают, так как блок 20 совпадения в это время закрыт импу сами 1 с инверсного выхода (п-1)-г триггера делителя 3 частоты. Если ,же эл. град., корот кие импульсы 39 попадают во второй полупериод опорной последовательности импульсов ,26, а значит через элемент ИЛИ 19 и блок 20 совпадения поступят на тактовый вход второго формирователя 21 управляющих импульсов, вызывая его переключение. Сигнал (импульсы 3) на выходе второ го формирователя 21 управляющих импульсов оказывается в противофазе с сигналом (импульсы 3) с выхода первого формирователя 11 управляЮ1Дих импульсов. При этом выходное напряжение инвертора (импульсы -tk равно нулю. В случае, если пилообраз ное развертывающее напряжение 27 пре высит величину управляющего напряжения в интервале 11- ,, то хотя ,на выходе компаратора 8 и появится сигнал 29, но на тактовый вход первого формирователя 11 управляющих импульсов он не поступит,так как блок 9 совпадения закрыт сигналом с (п-1)- входового элемента И-НЕ Тем самым, исключается аварийный режим в инверторе, вызванный тем, что при значениях угла об близким к 90 эл. град., за время от переключения первого формирователя управляющих импульсов до 7172, т.е; в интервале от (Р72тз(.) до /2 счетчик 15 не успеет подсчитать ни одного импульса высокой частоты и сигнал на Выходе схемы сравнения кодов, который в обычном режиме переключает второй формирователь управляющих импульсов, отсутствует. Предлагаемое устройство об спечивает высокую стабильность фазы выходного напряжения инвертора при регулировании и предотвращает аварийные режимы в инверторе при любых изменениях управляющего сигнала. Это позволяет создать высоконадежные инверторы, способные работать параллельно с другим источником переменного тока этой же частоты, и таким образом существенно повышать надежность электроснабжения ответственных потребителей. Формула изобретения Устройство для управления инвертором, содержащее блок синхронизации, включающий последовательно соединенные высокочастотный генератор и делитель частоты на п триггерах, формирователь развертывающего напряжения , вход которого подключен к прямому выходу (n-l)-ro триггера делителя частоты, источник управляющего напряжения, компаратор, один вход которого соединен с выходом формирователя развертывающего напряжения , а другой вход - с ВЫХОДОМ1 источника управляющего напряжения, два формирователя управляющих импульсов, управляющие входы которых попарно объединены и подключены соответственно к прямому и инверсному выходам п-го триггера делителя частоты, а также элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, один вход которого соединен с прямым выходом п-го триггера делителя частоты, а другой вход - с прямым выходом первого формирователя управляющих импульсов, два блока совпадения, одни входы которых объединены и подключены к выходу высокочастотного генератора, а другие входы - соответственно к прямому и инверсному выходам (п-1)-го триггера делителя частоты,, два счетчика импульсов, входы установки которых объединены и подключены к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а счетный вход каждого счетчика импульсов подключен к выходу одного из блоков совпадения и блок сравнения кодов, входы которого соединены с

выходами снетчиков импульсов, о тл и ч а ю щ е е с я тем, что, с целью повышения надежности путем ограничения угла регулирования , оно снабжено формирователем коротких им-г пульсов, двумя двухвходовыми элементами ИЛИ, (п-1)-входовым элементом И-НЕ, двумя двухвходовыми блоками совпадения и (п-1)-входовым блоком совпадения, входы которого под-, кЛючены к инверсному выходу (п-1)-го триггера и к прямым выходам предыдущи триггеров делителя частоты, входы (п-1)-входового элемента И-НЕ подключены к прямому выходу (n-l)-ro триггера и к инверсным выходам предыдущих триггеров делителя частоты, вход формирователя коротких импульсор подключен к выходу первого формирователя управляющих импульсов, выход первого двухвходового элемента ИЛИ подключен к тактовому входу первого формирователя управляющих импульсов, входы первого двухвходового блока совпадения соединены соответственно с выходом компаратора и с

ВЫХОДОМ (п-1)-входового элемента И-НЕ, выход соединен с одним из вхо дов первого элемента ИЛИ, другой : вход которого подключен к выходу (п-1)-вхоДового блока совпадения, при этом выход второго двухвходового блока совпадения подключен к тактовому входу второго формирователя управляющих импульсов, а входы соединены соответственно с инверсным выходом (п-1)-го триггера делителя частоты и с выходом второго двухвходового.логического элемента ИЛИ, один вход которого подключен к выходу формирователя коротких импульсов, а другой вход - к выхоДу блока сравнения кодов.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР

по заявке № 2б13059/2 -07, кл. Н 02 Р 13/18, 1978.

2.Авторское свидетельство СССР по заявке № 2785381/2 1-07,

кл. Н 02 Р t3/t8, 1979.

flflnflimnil

дояп. шшмш. iiiminima шплпппп ш

ХП

г

Ш

Л

. Л

HZJ

fpntl

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления инвертором | 1979 |

|

SU961097A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Многоканальное устройство для управ-лЕНия -фАзНыМ иНВЕРТОРОМ | 1979 |

|

SU813669A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Асинхронный электропривод | 1989 |

|

SU1697252A1 |

| ДВУХВХОДОВОЙ ЧАСТОТНЫЙ МОДУЛЯТОР | 2003 |

|

RU2248090C2 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

Авторы

Даты

1982-06-23—Публикация

1980-11-11—Подача