Динамический логический элемент может быть нрименен в электронных вычислительных машинах и устройствах цифровой автоматики.

В известных динамических логических элел{ентах задержка сигнала осуществляется либо линией задержки (при однофазной системе импульсного питания), либо за счет заряда или разряда накопительной емкости (при многофазной системе импульсного питания). Наличие реактивностей затрудняет изготовление элементов методами современной микроэлектроники и увеличивает потребление мощности по цепи импульсного питания.

С целью задержки входного сигнала без применения реактивных элементов (расширения технологических возможностей), снижения потребляемой элементом мощности по.цепи импульсного питания и увеличения коэффициентов объединения по входам «Я и «ИЛИ (расширения логических возможностей) в предложенном элементе в качестве схемы задержки сигнала применен ждущий мультивибратор и использовано постоянное напряжение для питания входной логической сборки, имеющей на выходе эмиттерный повторитель.

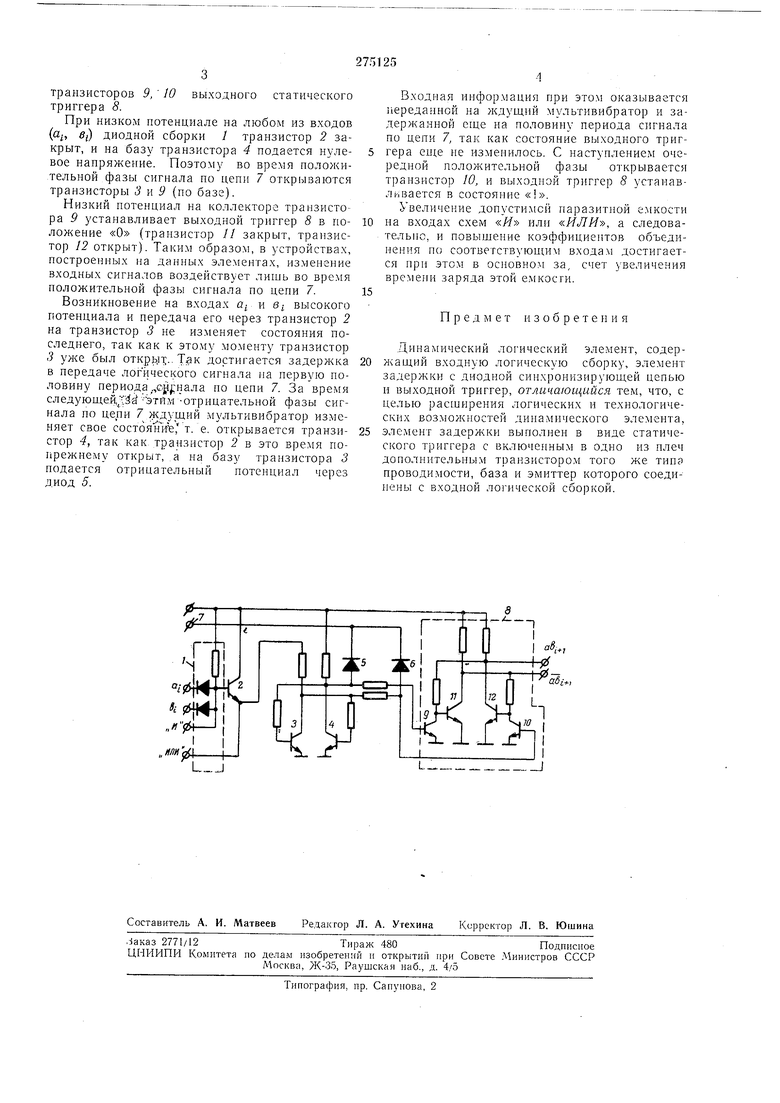

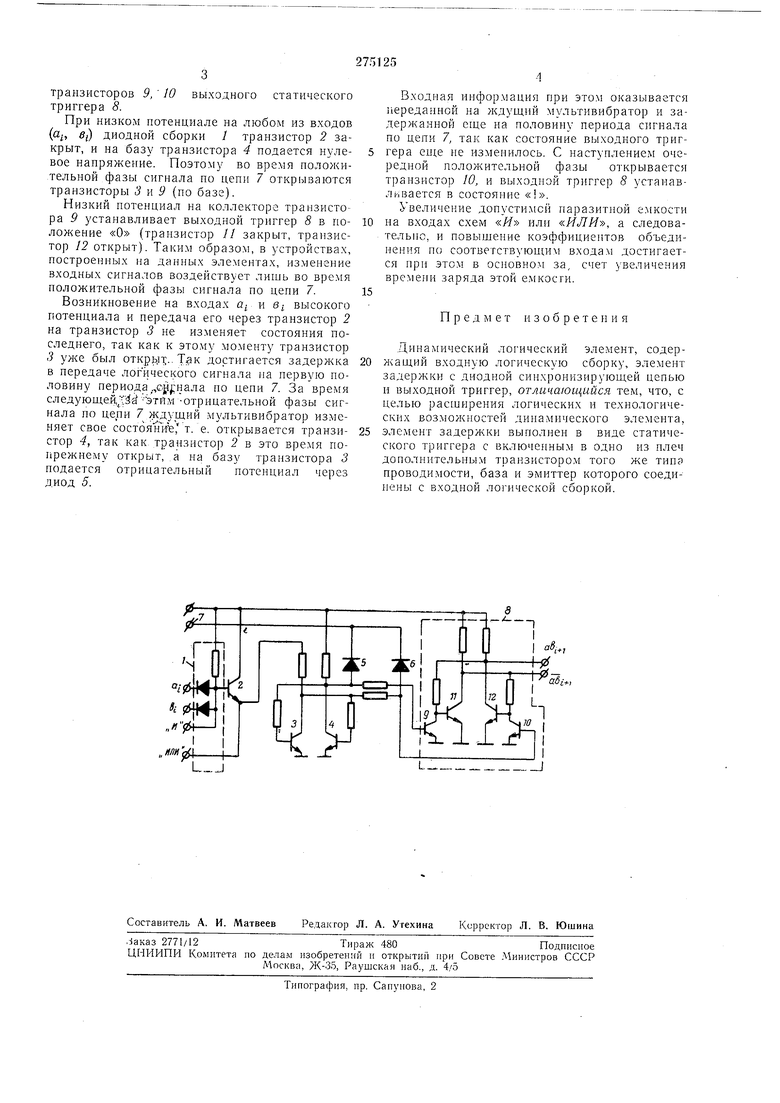

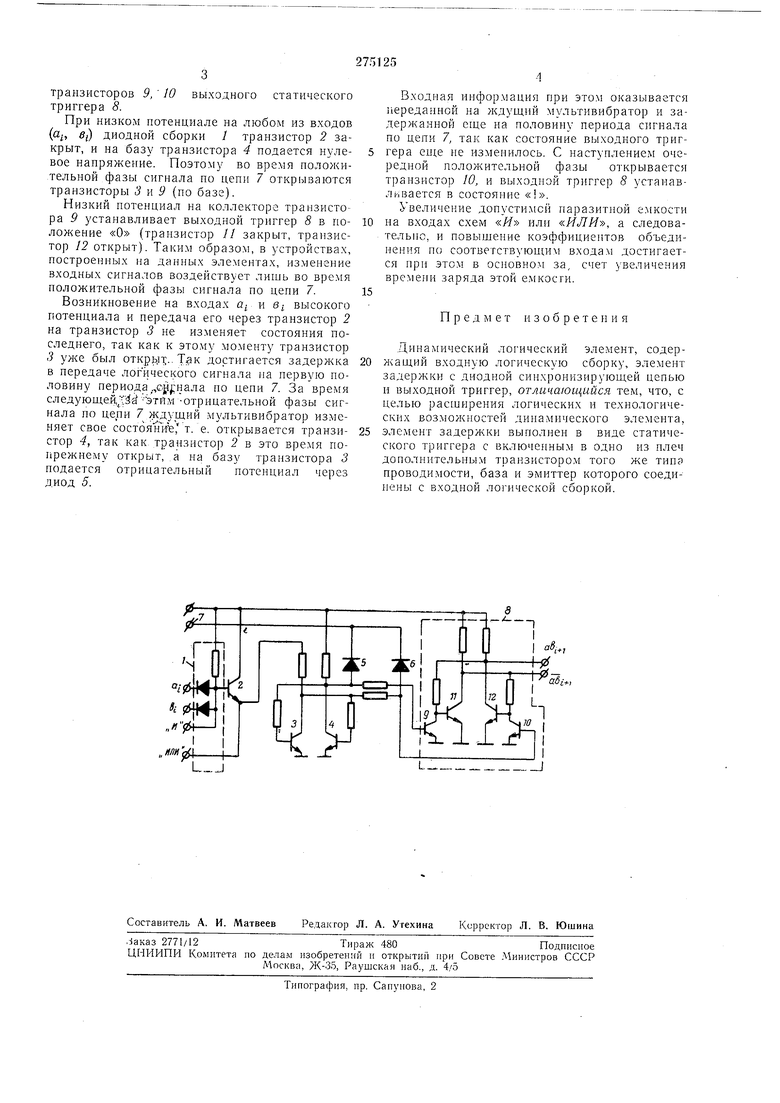

ный в коллекторную цепь триггера по схеме эмиттерного повторителя, транзисторы 3 и 4 триггера, диоды 5 и 6 синхронизирующей цепи, синхронизирующую цепь 7, выходной статический триггер 8, транзисторы запуска 9 и 10 и транзисторы // и 12 выходного триггера.

На чертеже обозначение выходных зажимов ив и ав отражает логическую зависимость выходных сигналов от входных а и в; а индексы /и (г + 1) -временную зависимость сигналов (где i - порядковый номер периода синхронизирующих импульсов).

Входная диодная сборка / соединена с базой транзистора 2 (схема «Я) и его эмиттером (схема «ИЛИ), содержит входную диодную сборку /, соединенную с базой транзистора 2 (схема «Я) и его эмиттером (схема «ИЛИ).

Транзистор 2 включен последовательно в коллекторную цепь транзистора 3 триггера. Такое включение преобразует триггер в л-сдущий мультивибратор, так как питание одного из плеч (3) осуществлено через транзистор, т. е. является функцией входной информации, а на коллектор транзистора 4 другого плеча, помимо постоянного напряжения, подается еще и отрицательная фаза импульсного питания через диод 5. Выходы ждущего мультивибратора соединены с базами управляющих

транзисторов 9, W выходного статического триггера 8.

При низком потенциале на любом из входов (а, б() диодной сборки 1 транзистор 2 закрыт, и на базу транзистора 4 подается нулевое напряжение. Поэтому во время положительной фазы сигнала по цепи 7 открываются транзисторы 3 9 (по базе).

Низкий потенциал на коллекторе транзистора 9 устанавливает выходной триггер 8 в положение «О (транзистор // закрыт, транзистор 12 открыт). Таким образом, в устройствах, построенных на данных элементах, изменение входных сигналов воздействует лишь во время положительной фазы сигнала по цепи 7.

Возникновение на входах О; и б/ высокого потенциала и передача его через транзистор 2 на транзистор 3 не изменяет состояния последнего, так как к этому моменту транзистор 3 уже был открьд.. Так достигается задержка в передаче логического сигнала на первую половину периода .., ал а по цепи 7. За время следуюш;ей, -отрицательной фазы сигнала по цепи 7 } дущий мультивибратор изменяет свое сост6ян1те,т. е. открывается транзистор 4, так как транзистор 2 в это время попрежнему открыт, а на базу транзистора 3 подается отрицательный нотенциал через диод 5.

Входная информация при этом оказывается переданной на ждущий мультивибратор и задержанной еще на половииу периода сигнала по цепи 7, так как состояние выходного триггера еще не изменилось. С наступление.м очередной положительной фазы открывается транзистор 10, и выходной триггер 8 устанавливается в состояние «.

Увеличение допустимей паразитной емкости на входах схем «Я или «ИЛИ, а следовательно, и повышение коэффициептов объединения по соответствующим входам достигается при этом в основном за, счет увеличения времени заряда этой е.мкосги.

Предмет изобретения

Динамический логический элемент, содержащий входную логическую сборку, элемент задержки с диодной синхронизирующей цепью и выходной триггер, отличающийся тем, что, с целью расщирения логических и технологических возможностей динамического элемента, элемент задержки выполнен в виде статического триггера с включенным в одно из плеч дополнительным транзистором того же тиц проводимости, база и эмиттер которого соединены с входной ло1ической сборкой.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU298072A1 |

| Двухтактный релаксатор | 1978 |

|

SU765987A1 |

| Устройство дифференциальной защиты | 1985 |

|

SU1272392A1 |

| Ч-П ^ . 1^.- . . . —. .пТ[»ЬЬ;;-ПЛ;:. ^1ЁИБЛИС L^-AА. Ф. Третьяков | 1971 |

|

SU290390A1 |

| Система впрыска топлива для двигателя внутреннего сгорания | 1970 |

|

SU442613A1 |

| Ждущий мультивибратор | 1979 |

|

SU864501A1 |

| Коммутирующее устройство | 1987 |

|

SU1515361A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Стабилизированный преобразователь постоянного напряжения | 1989 |

|

SU1700539A1 |

| ЖДУЩИЙ МУЛЬТИВИБРАТОР | 1970 |

|

SU425313A1 |

П i

, Т Тi-i3

Даты

1970-01-01—Публикация