Изобретенне относится к области вычислительной те.хипкн, в частности к заиомннающим устройствам цифрсвых вычислительных маИ1ИН.

Известны запоминающие устройства, содержащие матрицу запоминающих элементов, ключи записи, ключи оироса и усилители запрета.

Целью изсбретеппя является повышенпе быстродействия и снижение потребляемой мощностп.

Для этого ключи записи подключены к источнику питания через дроссель и интегрирующее устройство, выход которого подключен к усилителям запрета и устройству управления.

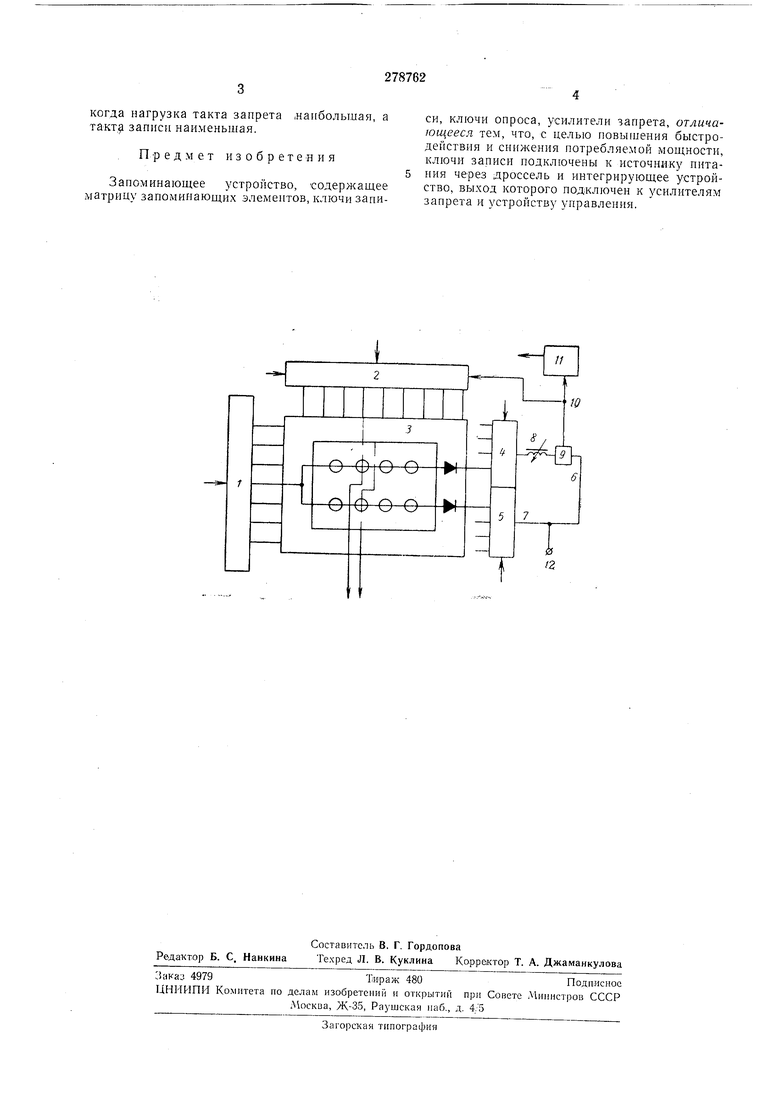

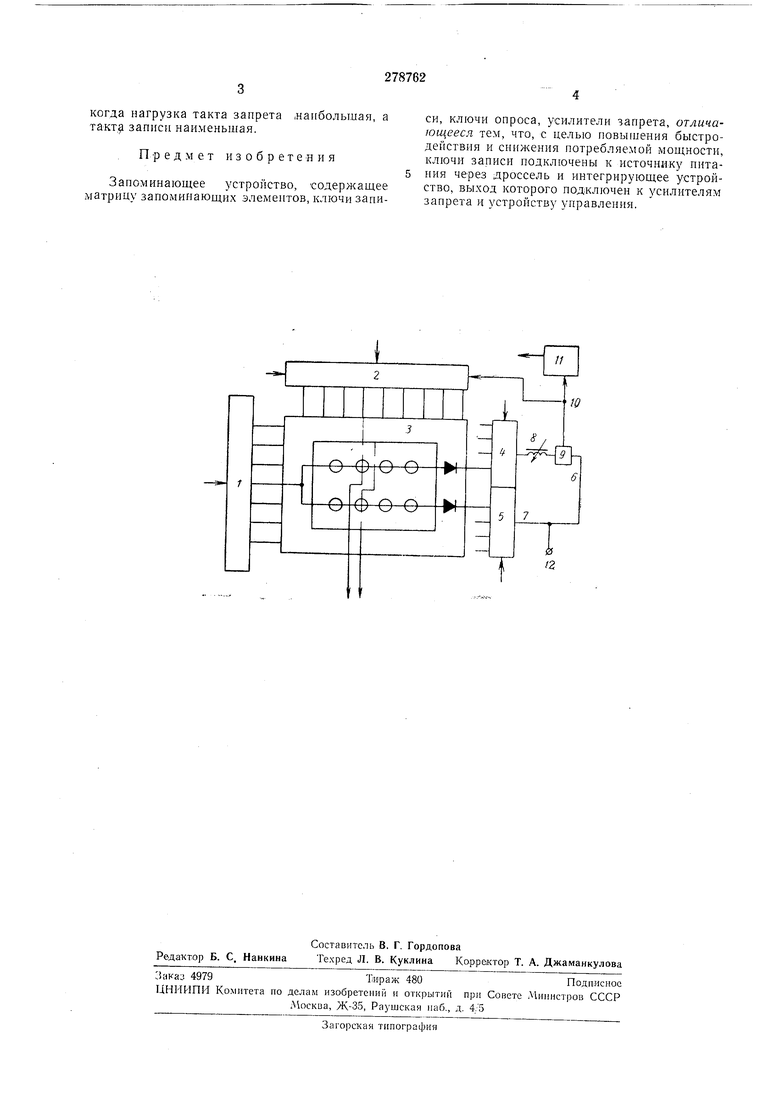

На чертеже показана принциииальная электрпческая схема описываемого запоминающего устройства, где: / - числовые ключи; 2 - усилители заирета (разрущеиия); 3 - |куб намяти на феррито-вых пластинах; 4 - ключей опроса; 8 - дроссель; 5 - иптегрииитания ключей записи; 7 - шина пигания ключей опроса; 8 - дроссель; 9 - интегрирующее устройство; 10 - выход интегрирующего устройства; // -устройство управления; 12 - клемма источника питания.

бранным оказывается одно из чисел куба памяти 3. Цикл обращения к выбранному числу в аналогичных устройствах состоит из четырех тактов: такта опроса, списывающего информацию с выбранного числа по цепи: ключ 1- выбранное чпсло - ключ 5 - щина 7-клемма 12 такта записи, следующего за тактом опроса по цепи: ключ / - выбранное число-шина 6 - клемма 12 такта заирета, следующего с некоторым опережением по времеии в момент такта записи ио цепи: усилитель 2 - разряд всех чисел куба 3 такта разрушения, следующего за. тактом заииси по цепп: усилитель 2 - разряд всех чисел куба 3.

В данном устройстве такт разрушения подается не в каждом цикле, а через несколько дясятков цнклов ио сигналу с интегрирующего устройства, например счетчика импульсов. Сигнал с интегрпрующего ycTpoiicTBa поступает на усилители 2 и на устройство 11, которое вырабатывает задержку перед прохождением следующего цикла, необходимую для прохождения такта разрущения.

Прн этом задержка переднего фронта сигнала записи относительно переднего фронта сшнала запрета отсутствуег, так как введенный дроссель обеснечивает необходимый фронт сигнала записи, повторяющий фронт сигнала заирета при иаихудщедГ сочетании.

наибольшая, а

когда нагрузка такта запрета такт. записи наименьшая.

Предмет изобретения

Запоминающее устройство, содержащее матрицу запоминающих элемеитов, ключи записи, ключи опроса, усилители запрета, отличающееся тем, что, с целью повьииения быстродействия и снижения потребляемой мощности, ключи записи подключены к источнику питания через дроссель и интегрирующее устройство, выход которого подключен к усилителям запрета и устройству управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ТИПА ЗД | 1971 |

|

SU427380A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Запоминающее устройство | 1973 |

|

SU474848A1 |

| Устройство для управления замещением информации | 1975 |

|

SU651413A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236862A1 |

| Устройство для группового сравнения двоичных чисел | 1975 |

|

SU650071A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА ЧИСЛА В ПОСЛЕДОВАТЕЛЬНОСТЬИМПУЛЬСОВ | 1970 |

|

SU272669A1 |

| СИНХРОНИЗАТОР | 1967 |

|

SU191226A1 |

/2

Даты

1970-01-01—Публикация