Предлагаемое устройство относится к области телеграфной связи, а к радиотелеграфным система.м с автоматическим запросом ошибочно принятой информации.

Известны запоминающие устройства для телеграфных систем с автоматическим переоиросом ошибочио принятой информации, соде.ржащие с.хему согласования с матрицей, матрицу памяти, схемы формироваргая адреса записи и считывания и выходную схему. Однако в известных устройствах воз.можны искажения из-за отсутствия автоматической установки минимального времени залаздывання считывания В начальный момент включения и .носле случайных сбоев. Эти устройства недостаточно надежды при изменении внешних условий и не располагают схемами автоматического контроля работоспособности.

Предлагаемое запоминающее устройство обеспечивает автоматическую установку минимального времени запаздывания, позволяет осуществлять автоматический -контроль ;работосиособности и новысить надежность устройства. Достигается это тем, что между выходом «старта схемы согласования и выходом «старта матрицы включена схема управления записью «старта, а между .выходом матрицы и входо.м выходного устройства включена схема восстановления «старта, причем выход кстарта матрицы и выход импульсов стартовой Полярности выходного устройства соединены соответственно с двумя входами опециальной схемы контроля.

В схеме согласования с матрицей выход сердечиика «старта регистра последовательнопараллельного преобразователя соединен цепью с соответствующим входом схемы стартстоиного пуска, выход которой подключеп на один вход схемы совпадения импульсов, соедп.ценной вторым входом с цепью нмиульсов .первого такта, а выходом - со входом ключевой схемы разрещенпя заппсп, включепной носледовательно в цепь иерезал.исп импульсов всех сердечииков регисгра.

В схеме матрицы последовательно с нмиульсным иеточн: :ком записи и считывания включен нсточнпк ностоя.цного тока определениой величнны, п;1юсо1;ой контакт которого заземлен, прнчем матрица разделена на секции,

связанные между собой по цепям заппсп и считывания через раздслительиые диоды.

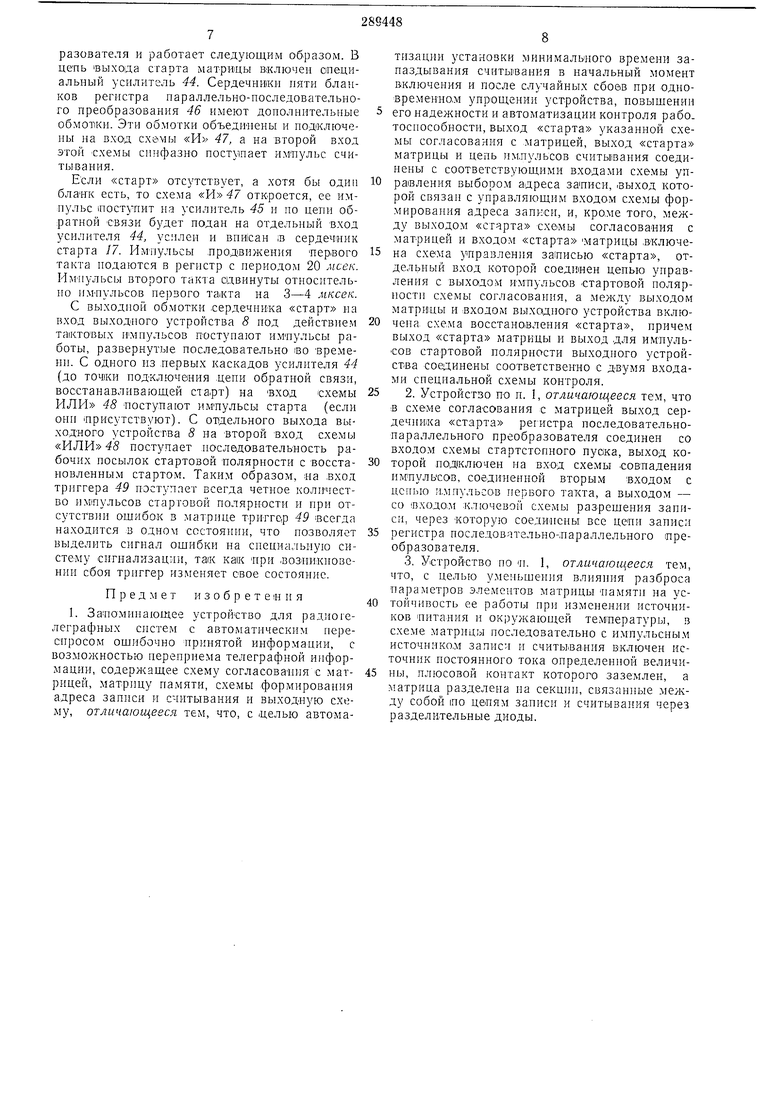

Па фнг. 1 ирнведепа блок-схе га заномииающето устройства; iia фнг. 2 - функцнональная схема согласоБан 1я с матр.ицей; иа фиг. 3 -

ирннцнниальная схема матрнцы; на фиг. 4 - фуп кциональная схема зааюмннающего устройства.

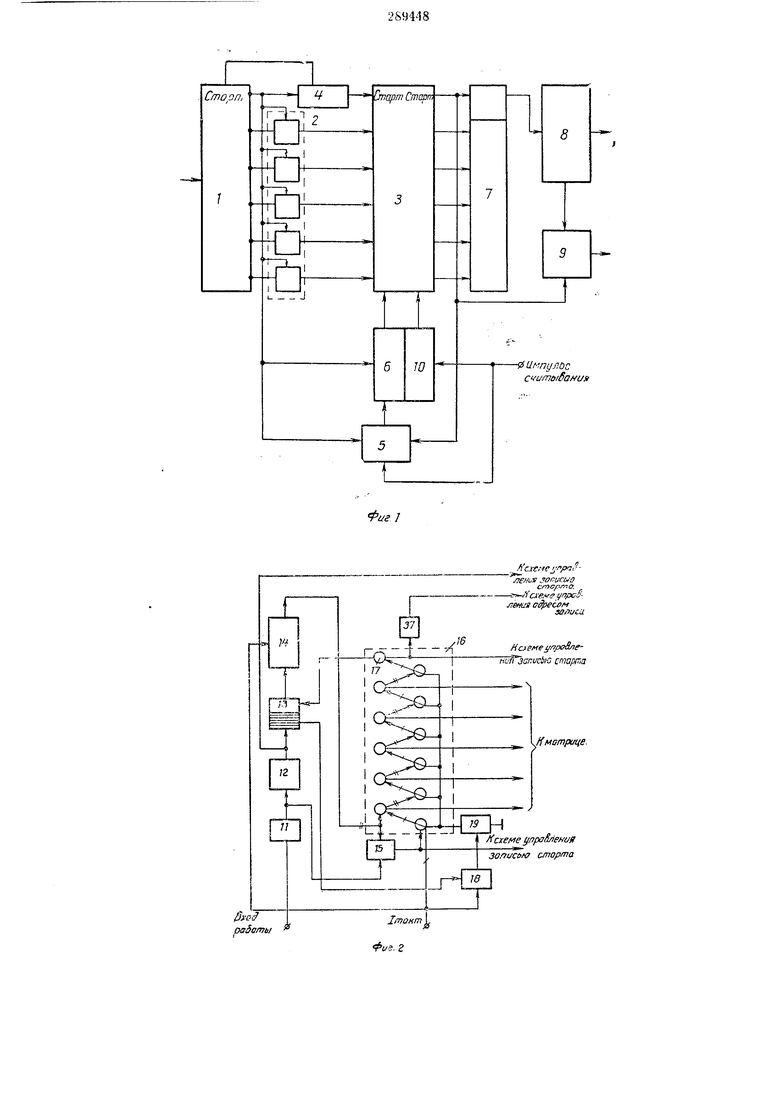

Предлагаемое устройство (см. фнг. 1) содержнт схему согласования /, нмеюи1ую щесть бинации, Соединенных через схемы «И 2 с соответствующими входами матрицы памяти 3. Выход «ста.рта схемы согласования 1 соединен с Соответствующим входом матрицы 3 через схему управления заиисыо 4. Эта схема связана со схемой согласования отдельной цепью управлеп11Я. Выход «старта схемы согласования н выход «старта матрицы соединены с двумя входами схемы уиратления выбо ром адреса записи 5. Третий вход схемы 5 связан с имиульсов считывания, а выход - с уиравляющнм ВХОдом схемы формирования адреса записи- 6. Схема 6 связана с выходом «старта схемы согласования /. В цепь выхода «старта матрицы 3 Включена схема восстановления «старта 7, соединенная с соответствующим входом выходного устройства 8, а специальная схема контроля .9 соединена одвим входом с отдельным выходом выходного устройства 8, а другим входом-с выходом «старта матрицы 3. Для уиравления считыванием запоминающее устройство содержит схему формирования адреса считывания 0, соединенную выходом с ценью считывання матрицы 3, а входом-с цепью имнульсов счнтьпвания. Схема согласования (см. фиг. 2) содержит входной усилитель-ограннчнтель //, выход которого соединен со входом схемы фазирования 12. Выход схемы фазирования 12 соединен с соответствующим входом схемы стартстопного нуска ЛЗ. Один из выходов этой схемы связан со входом формир01вавия стробирующих нмнульсоВ 14. Выход схемы формирования стробнрующнх имнульсов соединен с одиим из входов схемы «И 15 и цепью импульсов второго такта регистра последовательнопараллельного нреобразования 16. Выход сердечника «старта 17 регистра 16 соединен с соответствующим входом схемы стартстопного пуска 13. Второй выход схемы 13 соедннен со входом схемы «И 18, а на второй вход этой схемы нодключена цепь имиульсов первого такта. На второй вход схемы «И 15 подключеи также выход усилителя-ограничителя //. Выход схемы «PI 18 соедииен со входом ключевой схемы 19, которая включена носледовательио в цепи перезаписл импульсов всех сердечниKOiB регистра 16, а выход схемы 14 соединен со входом записи информации регистра 16 и входом схемы управления заннсью «старта /. Матрица намяти 3 (см. фиг. 3) выполнена по схеме полных токов. Входы матрицы соединены с соответствующими усилителями заниси 20-25. Элемент .памяти содержит адин сердечник с прямоугольной петлей гистерезнса |И днод. Шесть элементов памятн нредставляют собой числовую ячейку для записи одной кодовой комбинации. Каждый элемент намятн 26-31 соединен с коллектором соответствующего входного усилителя записи 20-25. Цени записи ще:ти элементов намяти 26- 31 и коллекторная цень усилителя считывания 32 подсоединены через диоды к одному концу выходной обмотки нмнульсного трансформатора 33. Этот трансформатор является им нульсным источником литания цепи заииси и считывания. Каждая числовая ячейка .имеет свой имиульсный источник нитания. Вторые концы выходных обмотак нмнульсных трансформаторов соедннены в одну точку и поданы на отрицательную клемму отдельного источника постоянного тока, плюсовой конец которого заземлен. Для уменьшения щу 1тирующего действия элементов намяти они разделены на секции, каждая из которых соединена с цепями записи и считывания через разделительные диоды 34-36. Заномииающее устройство (см. фиг. 4) действует следующим образом. Стартстонные сигналы с Л|Ннии иостуиают на вход усилителяограничителя // схемы согласования. С усилителя-ограничителя нмнульсы работы Постуиают иа схему фазироваиия 12, которая обеспечивает установку стробирующих имиульсов иа середине рабочих посылок. Кроме того, схема фазирования защищает от ложных запусков при наличии иомех в канале связи. Если стартовая посылка была не меньше половины нормальной длительности, с выхода схемы фазирования поступает импульс на запуск схемы стартстоиного пуска 13, -которая воздействует на схему формнровання стробирующнх имнульсоз 14. Эта схема содержит схему «И- и бинарные делители частоты. На схему «Н (иа один нз входов) иостунает отрицательный нотенциал триггера схемы стартстаиного пуска 13, а на другой вход - отрицательные имнульсы с частотой 800 гц с блока опорных частот. В результате с выхода схемы «И на вход бина рного делителя частоты поступают импульсы с частотой 800 гц ,в течение времени действ 1я схемы стартстопиого нуска. С выхода .иоследиего триггера бинарного делителя частоты нмпульсы с частотой следова.ния 50 гц идут на схему формирования импульсов второго такта и на двухтактный регистр -иоследовательно-иараллельцого нреобразоваиня 16. Импульсы первого такта поступают с частотой 800 гц с блока опорных частот. Импульсы второго такта поступают также на схему «И 15, на второй вход которой подаются нматульсы работы с усилителя-ограннчителя //. Имнульсы второго такта совнадают с серединами рабочих посылок и являются регенерирующими. Оии совиадают «а схеме «И 15 с отрицательиыми пьедесталами рабочих посылок в соответствии с пришедшей кодавой ко.мбипацией и последовательно вписывают «1 в регистр последовательно-параллельного преобразования 16 в моменты временн, когда в поступившей кодовой комбинации идет отрицательная посылала. Импульсы первого такта через схему «И 18, открываемую схемой стартстонного нуска 13, поступают на ключемую схему 19, которая разрешает нрод в и ж &11 и е и М1И у л ьс ов. В 1Иредложеином устройстве функции циклоного преобразователя совмещены в одном регистре на сердечниках с прямоугольной ,неглей гистерезиса. Под воздействием тактовых имоульсо.з происходит Нродвижение затканной кодовой комбинации по регистру 16 до тех пор, пока в момент второго такта со «стартового сердечника не появится положительный импульс, соответсизующий стартовому бланку. Этот нмлульс возвратит схему стартстолного пуска в исходное состояние, после чего закрывается ключевая схема 19 и за.прещает продвижение информации то регистру 16. ОдноЗременно возвращаются В исходное состояние триггеры делителя частоты.

Копда 1на выходе сердечника «старта появляется импульс, ОднОВременно поя;вляются импульсы на выходнрлх обмотках тех сердечников бланков, в которых была затшсана «1, и на выходе специального ключа 37. Импульсы с выходов ключа 37 и соответствующих сердечников (Поступают на схемы «И 2 -и одновременно записываются в матрицу 3. Запись старта происходит следующим образом. Триггер 38 соединен со схемой «И 15 (по счетному входу. Если в регистр 16 поступает нечетное число «1 (нечетное число им-пульсов стартовой полярности), то триггер останется в таком положении, что подключенпая к нему схема «И 39 будет открыта и стартовый импульс пройдет 1на запись в матрицу 3. Если число четное, то «старт з&писан не будет, так как схема «И 39 будет заперта.

Поскольку ключ 37 управляет схемой формирования адреса записи 6, которая каждый раз при поступлении «старта изменяет адрес на один отсчет, то запись информации произойдет в ту ячейку матрицы, на которую будет подано импульсное папряжеиие коммутаторного трансформатора (см. фиг. 3), связанного с соответствующим адресом (выходом) схемы формирования адреса записи.

Ймпульсы считывания формируются в блоке опорных частот 40, а управление их подачей осуществляться от внещнего источника, наПри.мер от радиотелеграфной аппаратуры с цереспросом. При поступлении импульса считывания «а схему формирования адреса считывания 10 последняя изменяет адрес иа один отсчет. Считывается та ячейка матри)цы, на которую будет подано импульсное напряжение с коммутаторного трансформатора, связанного с соответствующим выходом схемы формирования адреса считывания, и одновременно поступит импульс считывания на вход усилителя считывания 32 (см. фиг. 3).

Для повышения устойчивости работы матрицы ири изменении внещних условий последовательно с импульсными трансформаторами 33 включен ИСТОЧНИК постоянного тока, который приоткрывает диоды ячеек, устанавливая рабочую точку в начале линейного участка характеристики. Эта мера позволила значительно уменьщить неоднородность характеристик диодов, жоторая особенно заметна «а нелинейном участ1ке, и амплитуды имлульсов, проходящих через диоды, выравниваются. Кроме того, ячейки памяти под-ключены к усилителям записи секциями по несколько десятков ячеек, разделенными специальиьгми диодами 34, 35 и 36. Это сущестзепно уменьшает паразитную емкость и увеличивает эквивалентное обратное сопротивление ячеек памяти, не работающих в даппый момент, что позволяет увеличить объем памяти матрицы.

Минимальный фазовый сдвиг между записью и считыва}1ием 1.25 мсек. в начальный момеит схемы формироваипя адреса записи и считывания находятся в одинаковом положенитг, то зашись п считывание происходят практически без задержки. Если отсутствует считывание, то запоминающее устройство заполняется. Однако, в начальный момент в:ключения или в силу случайной помехи во время работы схемы формирования адреса записи считызпиия могут оказаться в разных положспия.х, а это привод1 т к нежелательному запаздыванию считывания п дансе нскажениям, например в том случае, когда импульсы считывания заблокированы, а запись продолжается, причем «обгоняет ту ячейку, с которой должно начаться считывание. Устраняет этот эс|)фект специальная схема управления выбором адреса записи, включенная между выходом «старта схемы согласования (ключ 57) и выходом «старта матрицы 3.

Схема уира,ленпя содержит схему «запрет 41; триггер 42 и схему «П 43. Если адреса записи и считывания в момеит включения разощлись, то первый же импульс «старта с выхода ключа 37 подготовит триггер 42. Когда адрес считывания дойдет до ячейки, в которую была записана кодовая комбинация, на выходах усилителей 44 и 45 импульс «старта. При этом импульс считывания пе пройдет через схему «запрет 41, а трпггер 42 возвратится в исходное состояние. Если очередного импульса старта в момент считывания не возникнет (что означает выборку нз матрицы всей информации), то импульс считывания поступит на схему «И 43 и на ее выходе возникнет импульс, обеспечивающий работу схемы формирования адреса записи от импульсов считывания.

Таким образом, если .в матрице отсутствует информация, то изменение адресов записи и считывания осуществляется с нфазно от импульсов считывания. Если в матрицу записана хотя бы одна комбинацня, то измеиение адреса записи происходит только от «старта ; при этом считывание «догоняет запись, и толико после считывания последней записаниой комбинации изменение адресов записи и считывания снова осуществляется от имиульсов считывания.

Импульс «старта вписьгаается в матрицу только при нечетном количестве импульсов стартовой полярности в кодовой комбинации. На выходе матрицы включена схема восстановления старта 7. Эта схема совмещена со схемой параллельно-последовательного иреобразователя и работает следующим образом. В цепь выхода сгарта матрицы включен сиециальный усилитель 44. Сердечники пяти бланков регистра параллельно-последовательного преобразования 46 имеют дополнительные обмот1ки. Эти обмотки объединены и пода лючепы на вход схемы «И 47, а на второй вход этой схемы спнфазно постушает импульс считываиия.

Если «старт отсутствует, а хотя бы один бланк есть, то схема «И 47 откроется, ее импульс (Поступит на усилитель 45 и по цепи обратной связи будет подан на отдельный вход усилителя 44, усилен и виисан IB сердечник старта 17. Импульсы .продвижения первого такта нодаются в регистр с иернодом 20 мсек. РЬшульсы второго такта сдвинуты относительно импульсов первого на 3-4 мксек.

С выходной обмотки -сердечника «старт на вход выходного устройства 5 иод дергствием TaiKTOBbix импулъсов поступают импульсы работы, развернутые последовательно во времени. С одного из .первых каскадов усилителя 44 (до точки подключения .цепи обратной связи, восстаиавливающей ста.рт) на вход схемы ИЛИ 48 цоступают имиульсы старта (если они присутствуют). С от1дельиого выхода выхо.дного устройства 8 на второй вход схемы «ИЛИ 48 поступает носледовательность рабочих посылок стартовой полярности с восстановленным стартом. Таким образом, «а .вход триггера 49 поступает всегда четное колнчество им1пульсов стартовой полярности и при отсутствии ошибо.к в матрице тритге.р 49 всегда находится в одном состоянии, что позволяет выделить сигнал ошибки на спеииальиую систему сигнализации, та1К ка1к ири .возцикиовеиии сбоя триггер изменяет свое состояние.

Иредмет изобретения

1. Запоминающее устройство для радиотелеграфных снстем с автоматнческим переспросом ошибочно прииятой информации, с возможностью иереприема телеграфной информации, содержащее схему согласования с матрицей, матрицу памяти, схемы формирования адреса записи п считывания и выходную схему, отличающееся тем, что, с .целью автоматизации установки минимального времени запаздывания считывания в начальный момент включения и после случайных сбоев при одновременио,м упрощении устройства, иовыщении его иадел ности и автоматизации коитроля работоспособности, выход «старта указанной схемы согласования с матрицей, выход «старта матрицы и цепь пмлульсов считьивания соединены с соответствующими входами схемы управления выбором адреса записи, выход которой связан с управляющим входом схемы формирования адреса записи, и, кроме того, между выходом «старта схемы согласования с матрицей и входом «старта матрицы .Включена схема управления записью «старта, отдельный вход которой соединен цепью управления с выходом импульсов стартовой поляр}1ости схемы согласования, а между выходом матрииы и входом выходного устройства включена схема восстановления «старта, причем выход «старта матрицы и выход для импульсов стартовой иоляриости выходпо.го устройства соединены соответственно с двумя входами сиециальиой схемы коитроля.

2. Устройство по п. 1, отличающееся тем, что в схеме согласоваиия с матрицей выход сердечиика «старта регистра последовательнопараллельного преобразователя соединен со входом схемы стартстопного иуака, выход которой подключен на вход схемы совпадения импульсов, соединенной вторым входом с цепью импульсов первого такта, а выходом - со входом ключевой схемы разрешения записи, через -которую соединены все цепи записи

регистра последовательно-параллельного преобразователя.

3. Устройство по П. 1, отличающееся тем, что, с целью уменьшения влияиня разброса параметров элементов матрицы памяти на устойчнвость ее работы нри изменении источников Питания и окружающей температуры, в схеме матрицы последовательно с имнульсны.м источиикол записи и считывания включен источник ностоянного тока определенной величины, плюсовой контакт которого заземлен, а матрица разделена на секции, связанные между собой по цепям записи и считывания через разделительные диоды.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Приемное устройство дополнительной цифровой информации, передаваемой в составе кадрового гасящего импульса полного телевизионного сигнала | 1988 |

|

SU1653179A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИ ОТВЕТНЫХ СИГНАЛОВ | 1970 |

|

SU259132A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310308A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| УСТРОЙСТВО КОММУТАЦИИ ТЕЛЕГРАФНЫХ КАНАЛОВ | 1970 |

|

SU270804A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

:icte,, jonctjo

Cf Cf7-r Q.

yrtfxfj emis сфесем

НаемеупррйлеHu ar.ucbi-s cmapiTia

({мотрсще.

f(схеме упро&пения

3oniict f cmopfna

rw/77. Старт

ВгоЗы

Даты

1971-01-01—Публикация