сл

ел ю со ю ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

| Сигнатурный анализатор | 1987 |

|

SU1499349A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

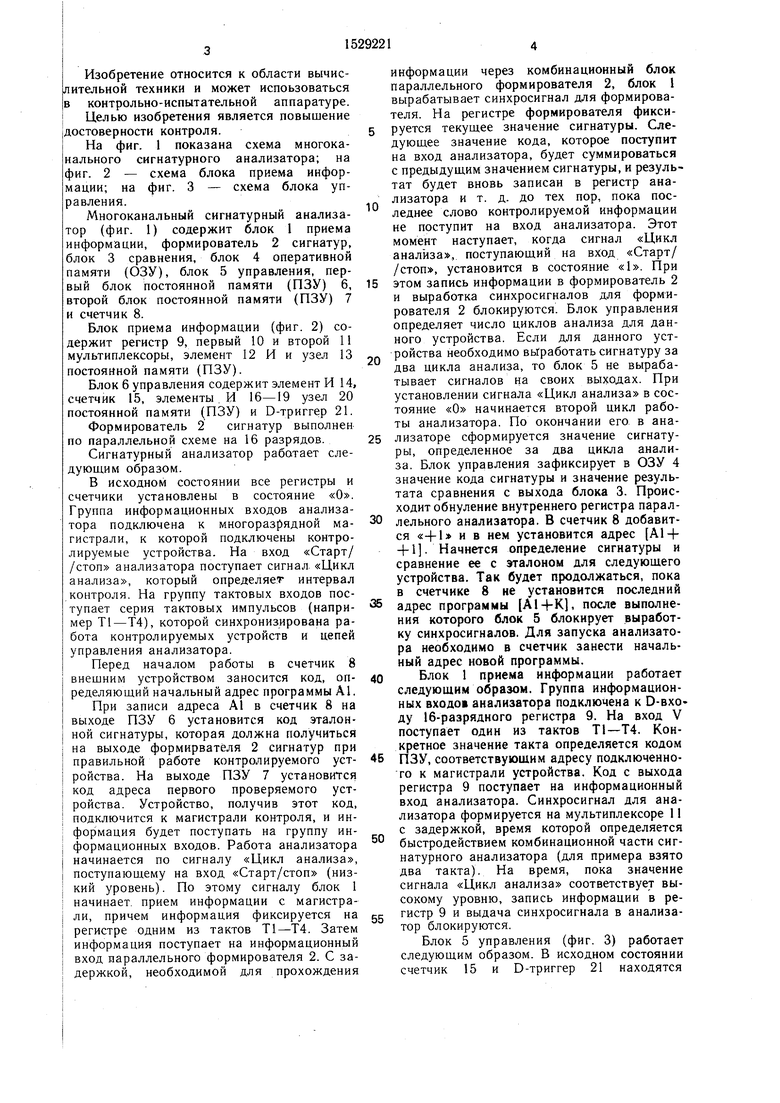

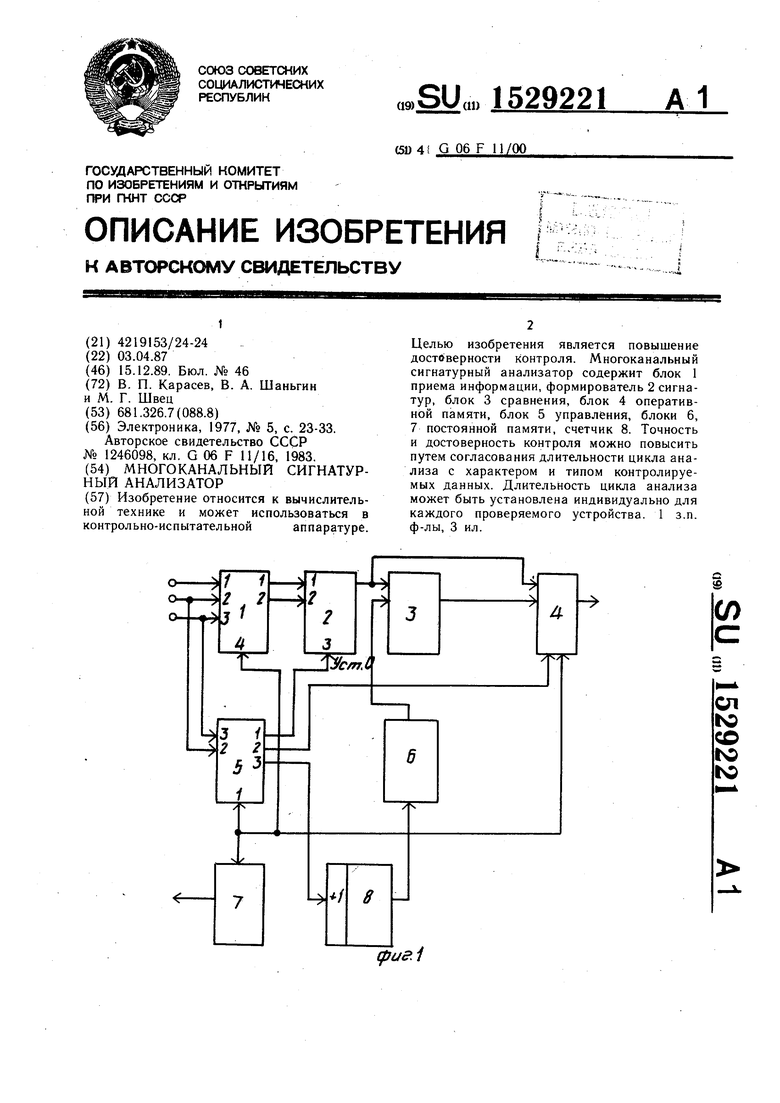

Изобретение относится к вычислительной технике и может использоваться в контрольно-испытательной аппаратуре. Целью изобретения является повышение достоверности контроля. Многоканальный сигнатурный анализатор содержит блок 1 приема информации, формирователь 2 сигнатур, блок 3 сравнения, блок 4 оперативной памяти, блок 5 управления, блоки 6,7 постоянной памяти, счетчик 8. Точность и достоверность контроля можно повысить путем согласования длительности цикла анализа с характером и типом контролируемых данных. Длительность цикла анализа может быть установлена индивидуально для каждого проверяемого устройства. 1 з.п. ф-лы, 3 ил.

gjuai

Изобретение относится к области вычислительной техники и может испоьзоваться в контрольно-испытательной аппаратуре. I Целью изобретения является повышение |достоверности контроля.

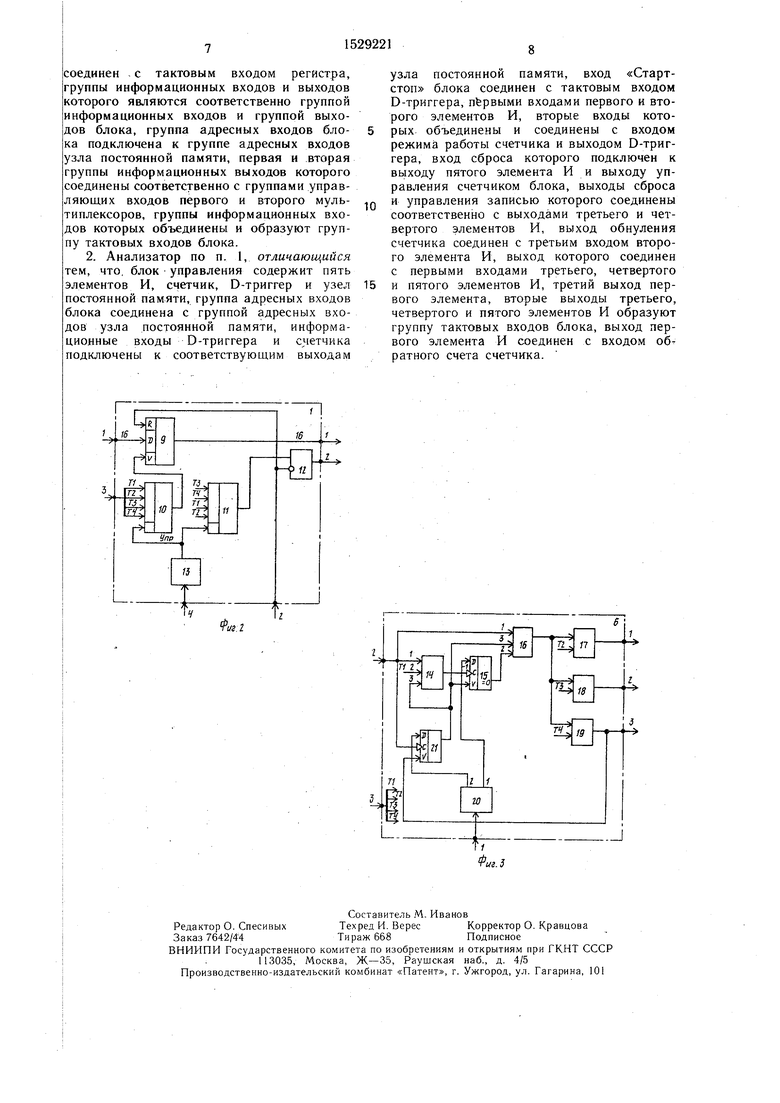

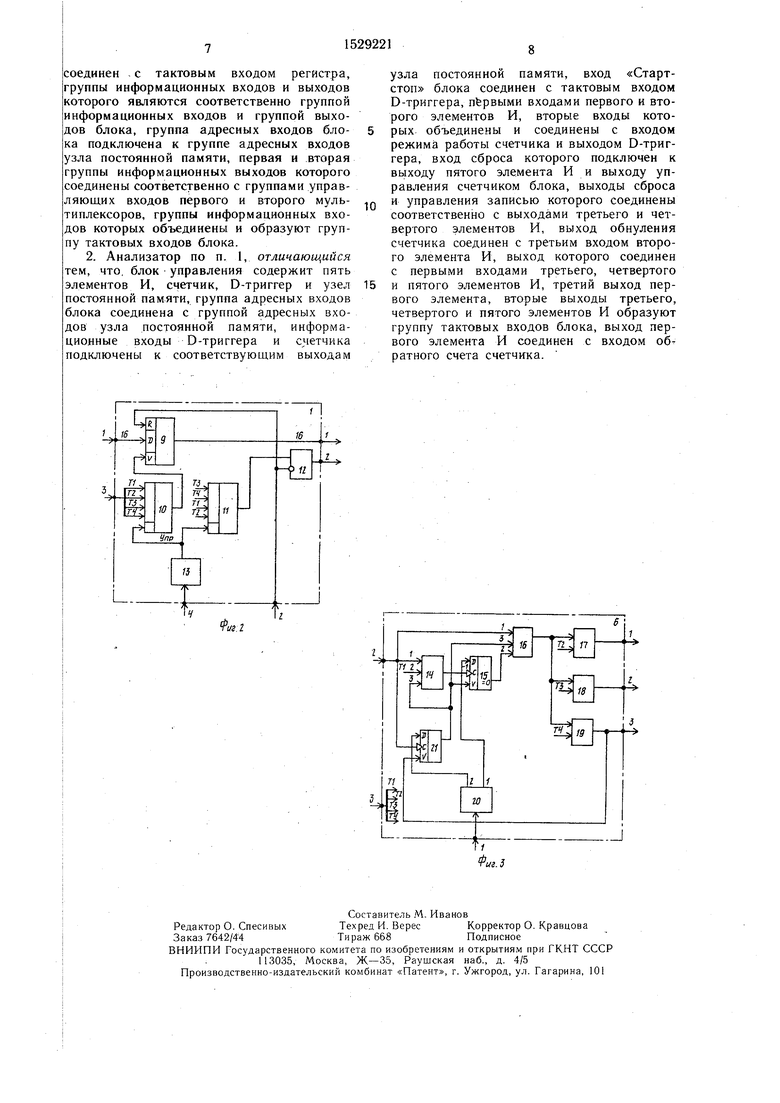

На фиг. 1 показана схема многоканального сигнатурного анализатора; на фиг. 2 - схема блока приема информации; на фиг. 3 - схема блока управления.

Многоканальный сигнатурный анализатор (фиг. 1) содержит блок I приема информации, формирователь 2 сигнатур, блок 3 сравнения, блок 4 оперативной памяти (ОЗУ), блок 5 управления, первый блок постоянной памяти (ПЗУ) 6, второй блок постоянной памяти (ПЗУ) 7 и счетчик 8.

Блок приема информации (фиг. 2) содержит регистр 9, первый 10 и второй 11 мультиплексоры, элемент 12 И и узел 13 постоянной памяти (ПЗУ).

Блок 6 управления содержит элемент И 14, счетчик 15, элементы . И 16-19 узел 20 постоянной памяти (ПЗУ) и D-триггер 21.

Формирователь 2 сигнатур выполнен по параллельной схеме на 16 разрядов.

Сигнатурный анализатор работает следующим образом.

В исходном состоянии все регистры и счетчики установлены в состояние «О. Группа информационных входов анализатора подключена к многоразрядной магистрали, к которой подключены контролируемые устройства. На вход «Старт/ /стоп анализатора поступает сигнал «Цикл анализа, который определяет интервал контроля. На группу тактовых входов поступает серия тактовых импульсов (например Т1-Т4), которой синхронизирована работа контролируемых устройств и цепей управления анализатора.

Перед началом работы в счетчик 8 внешним устройством заносится код, оп- ределяюш,ий начальный адрес программы А1.

При записи адреса А1 в счетчик 8 на выходе ПЗУ 6 установится код эталонной сигнатуры, которая должна получиться на выходе формирватёля 2 сигнатур при правильной работе контролируемого устройства. На выходе ПЗУ 7 установится код адреса первого проверяемого устройства. Устройство, получив этот код, подключится к магистрали контроля, и информация будет поступать на группу информационных входов. Работа анализатора начинается по сигналу «Цикл анализа, поступающему на вход «Старт/стоп (низкий уровень). По этому сигналу блок 1 начинает, прием информации с магистрали, причем информация фиксируется на регистре одним из тактов Т1-Т4. Затем информация поступает на информационный вход параллельного формирователя 2. С задержкой, необходимой для прохождения

информации через комбинационный блок параллельного формирователя 2, блок 1 вырабатывает синхросигнал для формирователя. На регистре формирователя фиксируется текущее значение сигнатуры. Следующее значение кода, которое поступит на вход анализатора, будет суммироваться с предыдущим значением сигнатуры, и результат будет вновь записан в регистр анализатора и т. д. до тех пор, пока пос- леднее слово контролируемой информации не поступит на вход анализатора. Этот момент наступает, когда сигнал «Цикл анализа, поступающий на вход «Старт/ /стоп, установится в состояние «1. При

этом запись информации в формирователь 2 и выработка синхросигналов для формирователя 2 блокируются. Блок управления определяет число циклов анализа для данного устройства. Если для данного устройства необходимо вьгработать сигнатуру за два цикла анализа, то блок 5 не вырабатывает сигналов на своих выходах. При установлении сигнала «Цикл анализа в состояние «О начинается второй цикл работы анализатора. По окончании его в ана5 лизаторе сформируется значение сигнатуры, определенное за два цикла анализа. Блок управления зафиксирует в ОЗУ 4 значение кода сигнатуры и значение результата сравнения с выхода блока 3. Происходит обнуление внутреннего регистра парал0 лельного анализатора. В счетчик 8 добавится «+1 и в нем установится адрес А14- -4-1. Начнется определение сигнатуры и сравнение ее с эталоном для следующего устройства. Так будет продолжаться, пока в счетчике 8 не установится последний

адрес программы Al-fK, после выполнения которого блок 5 блокирует выработку синхросигналов. Для запуска анализатора необходимо в счетчик занести начальный адрес HOBoti программы.

0 Блок 1 приема информации работает следующим образом. Группа информационных входе анализатора подключена к D-BXO- ду 16-разрядиого регистра 9. На вход V поступает один из тактов Т1-Т4. Конкретное значение такта определяется кодом

5 ПЗУ, соответствующим адресу подключенного к магистрали устройства. Код с выхода регистра 9 поступает на информационный вход анализатора. Синхросигнал для анализатора формируется на мультиплексоре 11 с задержкой, время которой определяется

быстродействием комбинационной части сигнатурного анализатора (для примера взято два такта). На время, пока значенне сигнала «Цикл анализа соответствует высокому уровню, запись информации в per гистр 9 и выдача синхросигнала в анализатор блокируются.

Блок 5 управления (фиг. 3) работает следующим образом. В исходном состоянии счетчик 15 и D-триггер 21 находятся

в состоянии «о. Кроме того, по адресу ПЗУ записан код «0...0, поэтому при поступлении .сигнала «Цикл анализа (по высокому уровню) продубли- руется установка D-триггера 21 в состоя- ние «О (так как на вход D) подан сигнал «О с выхода ПЗУ 20).

При установке в счетчике 8 кода начального адреса программы на первом выходе ПЗУ 20 установится код, который определяет, сколько циклов анализа будет подключено к магистрали данное устройство. На втором выходе ПЗУ 20 установится код «1. По отрицательному перепаду сигнала «Цикл анализа D-триггер 21 установится в состояние «1, а в счетчик 15 занесется код с выхода ПЗУ 20, соответствующий числу циклов анализа.

Кроме того, высокий уровень с выхода D-триггера 21 поступит на входы элементов 14 и 16. В течение цикла анали- за сигнал «Цикл анализа представляет собой «О, и на выходе элементов 14 и 16 сигнал тоже соответствует состоянию «О. По окончании цикла анализа на входе «Старт/стоп установится уровень «1. При этом по такту Т1 на вход «-1 счетчика 15 поступит сигнал, по которому его состояние уменьшится на единицу. Формирование синхросигналов для блока ОЗУ 4 и счетчика 8 блокировано, пока содержимое счетчика не будет равно нулю и на выходе «-0 не появится высокий уровень. Это произойдет, когда выпалнится установленное число циклов анализа. По такту ТЗ на выходе элемента 18 появится сигнал, по которому произойдет запись в блок ОЗУ 4. По такту Т4 на выходе эле- мента 19 появится сигнал, которым содержимое счетчика 8 увеличивается на единицу, и D триггер 21 устанавливается в состояние «О. Конец программы определяется содержимым кодом ПЗУ 7, ПЗУ 13 и ПЗУ 20 при считывании по последнему адресу программы. В эти ячейки должны быть записаны коды, соответствующие состоянию «О. При этом к магистрали не будет подключено ни одно устройство. В блоке 1 все входы мульти- плексоров 10 и 11 будут отключены. В блоке 5 с выхода ПЗУ 20 на вход D D-триггера поступит сигнал, соответствующий состоянию «О. Схема будет находиться в состоянии ожидания записи следующего начального адреса программы. Результаты анализа проверяемых устройств будут храниться в блоке ОЗУ, которое позволяет повысить точность контроля за счет анализа результата по совокупности сигнатур.

Применение в блоке приема программируемого выбора такта фиксации информации на магистрали позволяет повысить точность и достоверность контроля за счет

выбора момента фиксации независимо для каждого контролируемого устройства.

Точность и достоверность контроля можно повысить путем согласования длительности цикла анализа с характером и типом контролируемых данных. В предлагаемом устройстве длительность цикла анализа может быть установлена индивидуально для каждого проверяемого устройства.

Формула изобретения

соединен .с тактовым входом регистра, группы информационных входов и выходов которого являются соответственно группой информационных входов и группой выходов блока, группа адресных входов блока подключена к группе адресных входов узла постоянной памяти, первая и вторая руппы информационных выходов которого соединены соответственно с группами управляющих входов первого и второго мультиплексоров, группы информационных входов которых объединены и образуют группу тактовых входов блока.

узла постоянной памяти, вход «Старт- стоп блока соединен с тактовым входом D-триггера, первыми входами первого и второго элементов И, вторые входы которых объединены и соединены с входом режима работы счетчика и выходом D-триггера, вход сброса которого подключен к выходу пятого элемента И и выходу управления счетчиком блока, выходы сброса

и управления записью которого соединены соответственно с выходами третьего и четвертого элементов И, выход обнуления счетчика соединен с третьим входом второго элемента И, выход которого соединен с первыми входами третьего, четвертого

и пятого элементов И, третий выход первого элемента, вторые выходы третьего, четвертого и пятого элементов И образуют группу тактовых входов блока, выход первого элемента И соединен с входом обратного счета счетчика.

| Электроника, 1977, № 5, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1246098A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-15—Публикация

1987-04-03—Подача