Изобретение относится к области Вычислительной техники и предназначено для определения корреляционной функции стационарных случайных процессов.

Известный аналого-дискретный коррелятор, содержащий аналоговое запоминающее устройство, множительное устройство и интегратор, не позволяет получить заданную статистическую погрешность -при минимальном интервале наблюдения.

Предложенное устройство отличается тем, что между множительным устройством и многоканальным аналого-дискретным интегратором подключен блок коэффициентов; между блоком задания допустимой ошибки и накопительной ячейкой включен элемент сравнения, вход накопительной ячейки соединен с выходом блока коэффициентов, сигнальные входы первого коммутатора подключены к выходам упомянутого интегратора и аналогового запоминающего устройства, выход первого коммутатора соединен с первым входом множительного устройства; сигнальные входы второго Коммутатора соединены с выходами упомянутого интегратора и аналогового заиомпиающего элемента, а выход второго коммутатора подключен ко второму входу множительного устройства.

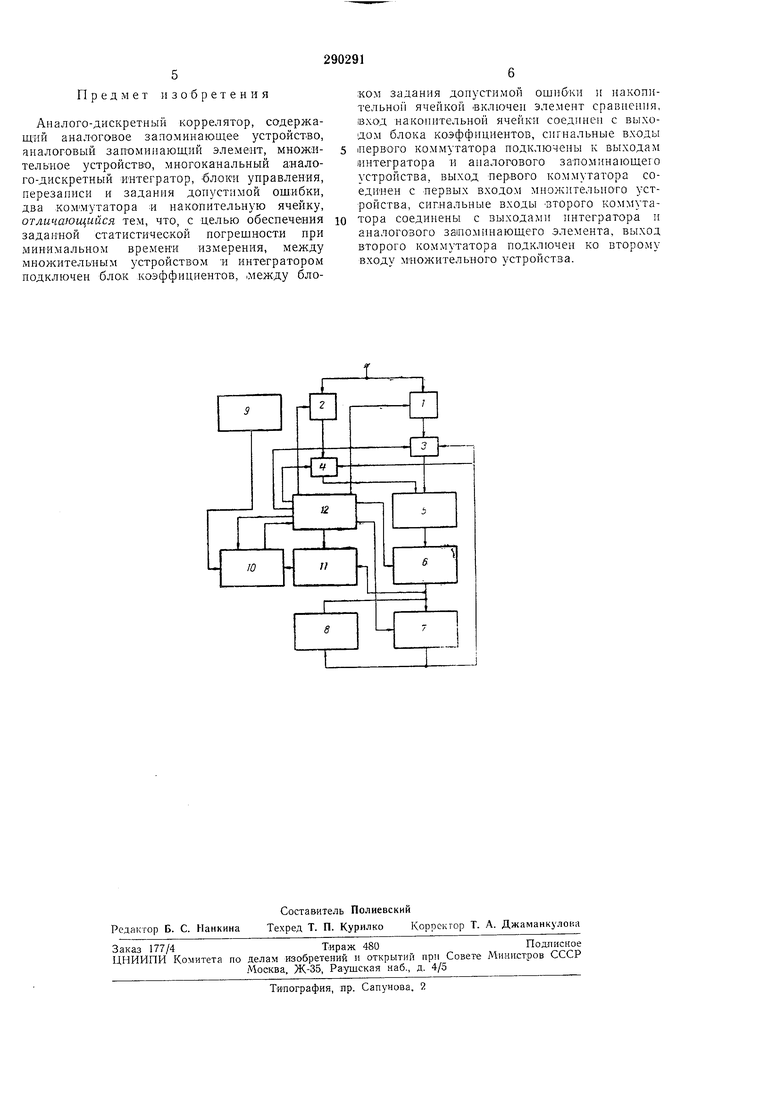

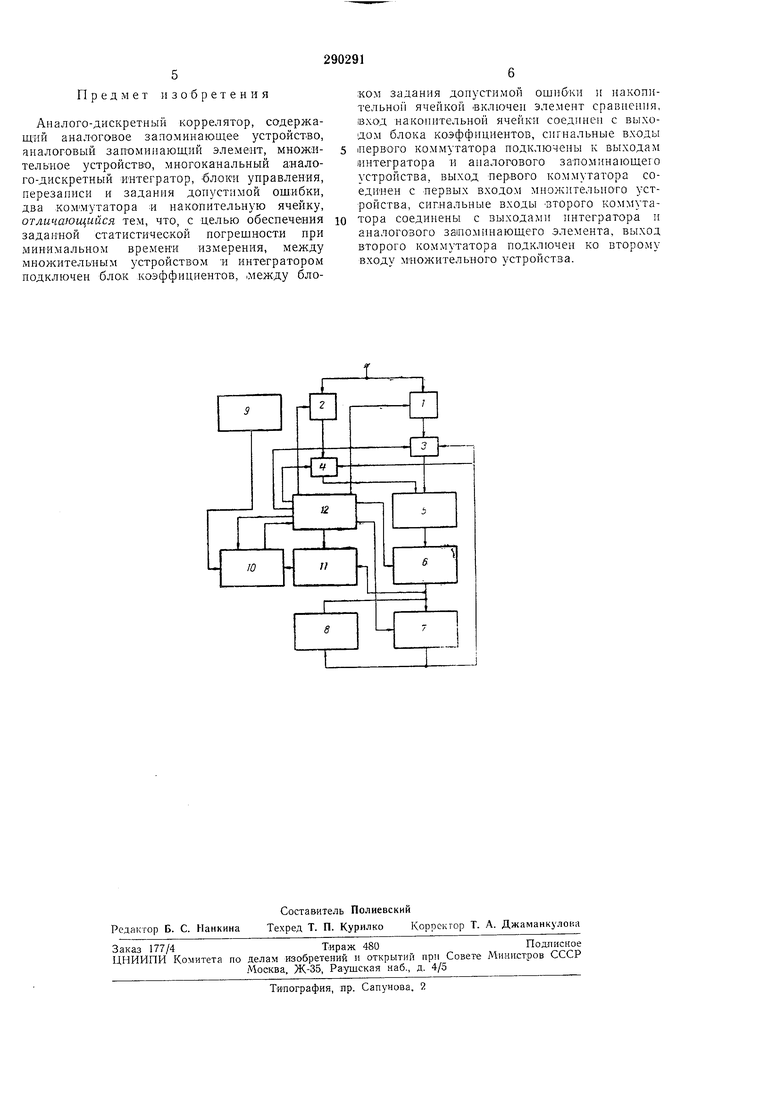

На чертеже изображена блок-схема описываемого коррелятора.

Аналоговое запоминающее устройство (блок 1) и аналоговый запоминающий элемент (блок 2) через коммутаторы 3 и 4 .подключены ко входам множительного устройства 5. Выход множительного устройства через блок коэффициентов 6, представляющий собой секционированный делитель с отводами и коммутатором, соединен со в.ходом многоканального аналого-дискретного интегратора 7. Между выходом и входом интегратора 7 включен блок перезаписи 8, позволяющий изменять масштаб величин, хранимых в интеграторе 7. Блок нерезаписи построеп аналогично элементу 2 с той разницей, что обеспечивает регулируемый коэффициент передачи. Выход блока 9 задания допустимой ошибки соединен с первым входом

элемента сравнения 10, второй вход элемента сравнения подключен к выходу накопительной ячейки 11. Вход накопительной ячейки // соединен с выходом блока коэффициентов 6. Сигнальные входы первого коммутатора 5 подключены к выходам интегратора 7 и аналогового запоминающего устройства /. Выход коммутатора 3 соединен с первым входом множительного устройства 5, сигнальные входы коммутатора 4 соединены с выхонающего элемента 2. Выход коммутатора 4 подключен «о второму входу множительного устройства 5. Выход блока управления 12 соединен со входами блоков 2, 3, 4, 6, 7, 10 и //.

В работе коррелятора предусмотрены два режима: режим вычисления оценки корреляционной функции и режим вычислеиия дисперсии оценки и сравнения ее с заданной допустимой статистической ногрешностью. Переход от первого режима ко ;второму и обратно осуществляется автоматически.

Работа коррелятора начинается с лервого режима. Посредством коммутаторов 3 и 4 выходы блоков 1 1 2 иодключаются ко входам множительного устройства 5. Блок коэффициентов 6 обеспечивает коэффициент передачи, где N - количество циклов, после

Л

йынолнения которых всякий раз производятся вычисления дисперсии оценки и сравнение ее с заданной статистической погрешностью.

Каждый г-й цикл вычисления начинается записью очередной ордииаты X(ti) процесса X(t) в блоки / и 2 (ii - момент начала t-ro цикла) и их перемножением с прибавлением полученного произведения, поделенного в блоке коэффициентов на N, к ранее накоп1

ленной сумме-р 2 (г)хранящейся в первой ячейке интегратора 7. В блоке 1, кроме вновь записанной ординаты /f(//), хранятся также т-1 ординаты процесса X(t), записанные ъ т-1 предыдущих циклах и соответствующие сдвигу друг относительно друга на время Дт, так как шаг дискретизации процесса А Ат- Эти т-1 ординаты также умножаются на X(ti), и полученные парные произведения, поделенные .в блоке коэффициентов на N, прибавляются к соответствующим суммам парных произведений, хранящимся в ячейках интегратора 7. После выполнения всех этих операций ордината X(ti) в блоке 2 и самая «старая ордината Af/i- - (т - 1)Ат в блоке 1 стираются, чем и заканчивается i-й цикл. (1-|-1)-й цикл начинается записью X(ti + i) в блоки 1 и 2, после чего повторяются все операции предыдущего цикла.

Проделав N циклов вычисления оценки, коррелятор автоматически переводится во второй режим. При этом коммутаторы 3 и 4 отключают входы устройства 5 от выходов блоков У и 2 и подключают к выходу интегратора 7. Вычисление дисперсии оценки производится в соответствии с формулой для вычисления дисперсии оценки корреляционной функции стационарного случайного процесса с нормальным распределением:

.:( /((0).(иЛ.) .

) 2 в блоке коэффициентов 6 делится на Л/ и через первый входной конденсатор на,ко.нительной ячейки с коэффициентом 2 запоминается в накопительном конденсаторе в цени обратной связи ячейки. Остальные значения оценки также возводятся в квадрат, делятся на Л в блоке коэффициентов 6, но затем подаются на второй входной конденсатор и добавляются к содержимому накопительного конденсатора с коэффициентом 4. Вычисленная таким образом дисперсия оценки с помощью элемента сравнения сравнивается с заданной допустимой ошибкой. Если при этом дисперсия не превышает

допустимой ошибки, то элемент сравнения выдает сигнал останова в блок управления. Если же она превышает допустимую ошибку, то содержимое ячеек интегратора 7 перезалисывается в эти же ячейки с коэффициентом 1/2- Одновременно с этой операцией в блоке коэффициептов 6 посредством переключения его выхода на другой отвод секционироваННОго делителя устанавливается коэффициент деления 2 Л , а также разряjKacTCH накапливающий конденсатор накопительной ячержи и, после чего коммутаторы 3 и 4 подключают входы устройства 5 к выходам блоков / и 2 и коррелятор начинает новую серию вычислений из N циклов.

Во время работы коррелятора по второму режиму, который занимает время трех циклов, блоки 1 v( 2 работают как и в первом режиме, т. е. в соответствующие моменты времени, отстоящие на Ат, в них стираются

старые значения отсчета случайного процесса и записывается новое. Поэтому временная задержка между ними остается все время равной Ат. После выполнения второй серии вычисления оценки коррелятор снова автоматически переводится во второй режим и -производятся вычисление дисперсии оценки и сравнение ее с заданной допусти.мой ошибкой. В случае выполнения неравенства (т)5 вычисления прекращаются, а в случае невыполнения происходят перезапись содержимого ячеек интегратора 7 с коэффициентом 2/3, установление в блоке коэффициентов 6 коэффициента деления 3 Л н разряд конденсатора накопительной ячейки, после чего коррелятор перейдет к третьей стадии вычисления оценки.

Работа коррелятора продолжается таким образом до тех пор, пока дисперсия оценки не станет меньше допустимой ошибки. При этом, в случае невыполнения этого условия после Л-ой серии вычисления оценки перезапись содержимого ячеек иитегратора 7 К

происходит с коэффициентом , и в блоА+1Предмет изобретения Аналого-дискретный коррелятор, содержащий аналоговое запоминающее устройство, аналоговый запоминающий элемент, множительное устройствО, многоканальный аналого-дискретный интегратор, блоки унравления, перезаписи и задания допустимой ошибки, два коММутатора и накопительную ячейку, отличающийся тем, что, с целью обеспечения заданной статистической иогрещности при минимальном времени измерения, между множительным устройством и интегратором подключен блок коэффициентов, ,между блоком задания допустимой ошибки п накопительной ячейкой -включен элемент сравнения, |вход накопительной ячейки соединен с выходом блока коэффициентов, сигнальные входы первого коммутатора подключены к выходам интегратора и аналогового запоминающего устройства, выход первого коммутатора соединен с первых входом множительного устройства, сигнальные входы Второго коммутатора соединены с выходами интегратора и аналогового запоминающего элемента, выход второго коммутатора подключен ко второму входу множительного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНА П | 1973 |

|

SU378892A1 |

| Коррелятор | 1975 |

|

SU525119A1 |

| Коррелятор | 1976 |

|

SU696474A1 |

| УСТРОЙСТВО для ОЦЕНКИ ВЕРОЯТНОСТНО- СТАТИСТИЧЕСКИХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1971 |

|

SU314215A1 |

| КОРРЕЛЯТОР ДЛЯ ОПЕРАТИВНОГО АНАЛИЗА СЛУЧАЙНЫХ ПРОЦЕССОВ | 1970 |

|

SU264789A1 |

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1972 |

|

SU357565A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРОЯТНОСТНЫХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU432512A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| КОРРЕЛЯТОР ДЛЯ АНАЛИЗА СЛУЧАЙНЫХ ПРОЦЕССОВ С ПЕРИОДИЧЕСКОЙ НЕСТАЦИОНАРНОСТЬЮ | 1971 |

|

SU292170A1 |

| КОРРЕЛЯТОР | 1973 |

|

SU374607A1 |

Даты

1971-01-01—Публикация