1

Изобретение относится к области вычислительной техники и является специализированным устройством для оперативного (в ходе случайного Процесса) вычисления корреляционной функции стационарного случайного процесса, заданного в виде непрерывно изменяющегося напряжения. Использование алгоритма, предусматривающего автоматическое определение интервала наблюдения в ходе вычисления оценки корреляционной функции, обеспечивает заданную статистическую погрешность при минимальном времени наблюдения. Устройство может быть применено в самонастраивающихся системах автоматического управления, в гидроакустике, в технической и медицинской диагностике.

Известный аналого-дискретный коррелятор с автоматическим онределением интервала наблюдения, обеспечивающим заданную статистическую погрещность, состоит из аналогового запоминающего устройства (АЗУ), аналогового запоминающего элемента (АЗЭ), многоканального авалого-дискретного интегратора (МАДИ) с блоком перезаписи, построенных на базе усилителей постоянного тока с коммутируемыми конденсаторами на входе и в цепи обратной связи, а также множительного устройства (МУ), блока коэффициентов, блока задания ощибки, накопительной ячейки и элемента сравнения.

В таком устройстве производится дискретизация входного сигнала по времени и обработка дискретных отсчетов в аналоговой форме. Вычисление производится циклически, причем в течение цикла вычисляются парные произведения для всех т точек оценки и накапливаются в конденсаторах МАДИ.

В корреляторе в ходе вычисления оценки корреляционной функции /Сх()гДт) производится автоматическое определение минимального при заданной статистической точности интервала наблюдения, для чего периодически, через каждые N циклов производится вычисление дисперсии оценки по формуле

15

т-1

- Kl(Q) + 2 2 К1( А .)

и сравнение ее с заданной статистической погрешностью. При этом накопление значения дисперсии оценки производится в отдельном аналого-дискретном накопителе (накопительная ячейка), построеннол1 аналогично Л1АДИ,

но одноканальном.

Цель изобретения - упростить устройство коррелятора.

Для этого в нем в качестве накопителя значения дисперсии оценки вместо накопительной

ячейки использован аналоговый запоминаю1ЦИЙ элемент, свободный при вычислении дисперсии оценки от вычисления корреляционной функции.

Услол нение функций АЗЭ достигается тем, что его второй вход связывают с выходом блока коэффициентов, а выход подсоединяют к одному из входов элемента сравнения.

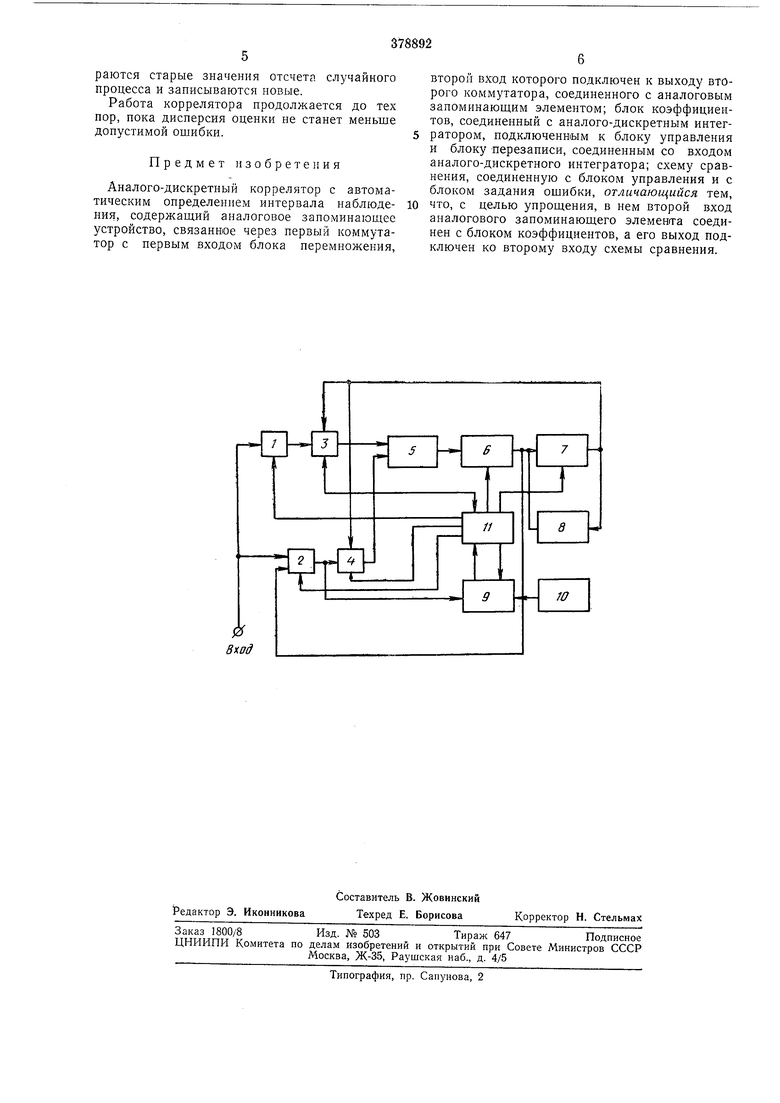

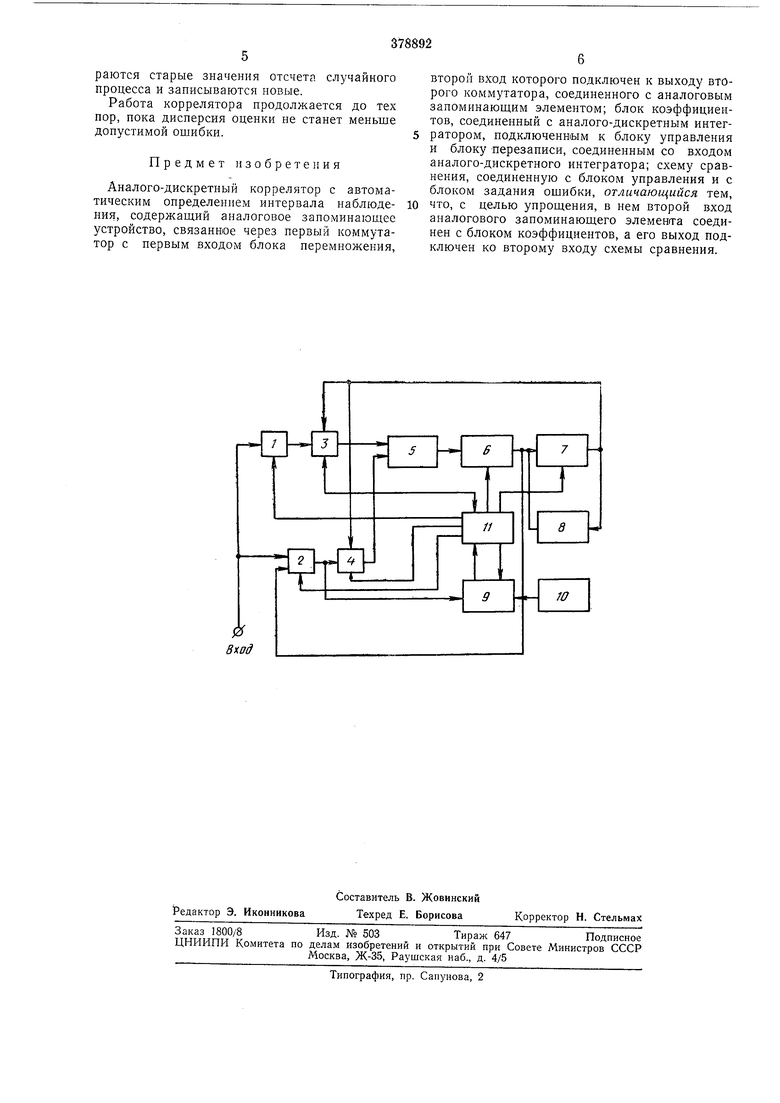

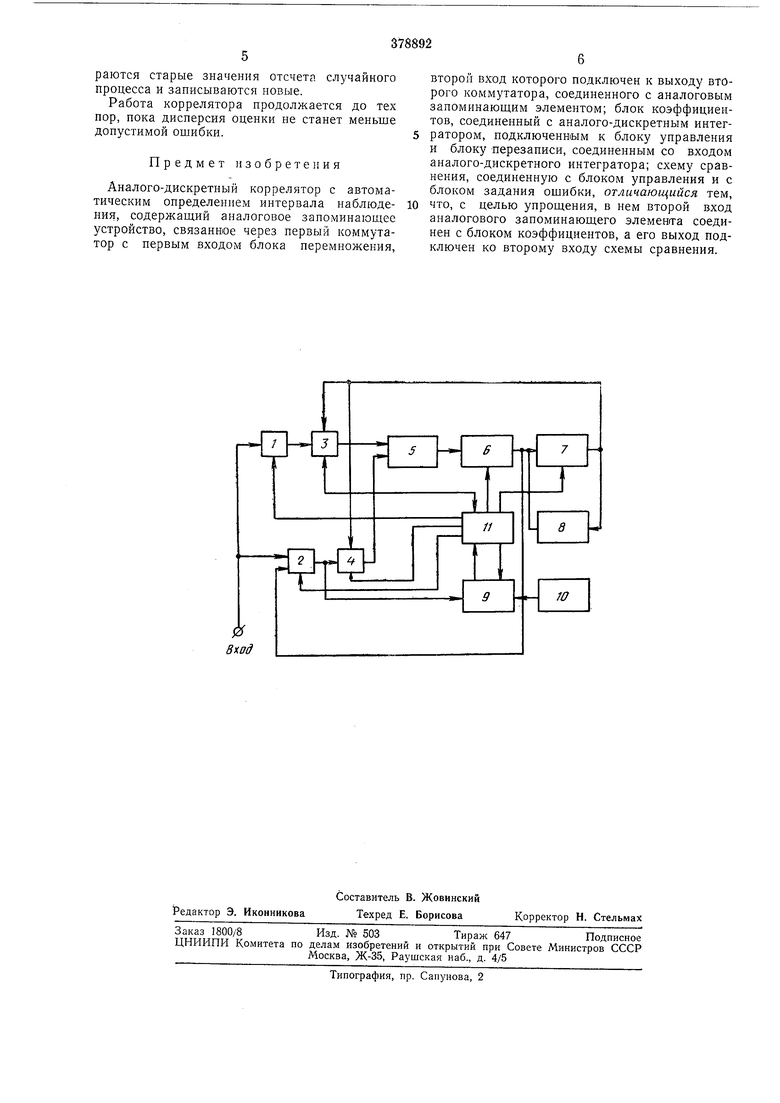

На чертеже изображена блок-схема предлагаемого коррелятора.

Коррелятор содержит аналоговые запоминающие устройства / н элемент 2, которые через коммутаторы 3 п 4 подключены ко входам блока 5 перемножения. Выход блока 5 через блок 6 коэффициентов, представляющий собой секционированный делитель напряжения с отводами и коммутатором, соединен со входом многоканального аналого-дискретного интегратора 7. Между выходом и входом этого интегратора включен блок перезаписи 8, аналогичный ему по устройству, но позволяющий изменять масштаб величин, хранимых в интеграторе 7, регулировать коэффициент нередачи. Выход блока 5 через блок 6 связан также со вторым входом блока 2, выход которого соединен со схемой сравнения 9. Второй вход схемы 9 соединен с выходом блока 10 задания ошибки.

Как видно из формулы, по которой вычисляется дисперсия оценки, первое слагаемое имеет коэффициент «2, а все остальные - «4. Поэтому на втором входе аналогового запоминающего элемента включены два конденсатора; емкость одного из них в два раза больше емкости конденсатора в цени обратной связи усилителя, а второго - в четыре. Первое слагаемое диснерсии оценки передается через -первый конденсатор, а все остальные - через второй. Работа всего устройства синхронизируется блоком управления 11.

В работе коррелятора предусмотрены два режима: режим вычисления оценки корреляционной функции и режим вычисления дисперсии оценки и сравнения ее с заданной допустимой статистической погрешностью.

Работа коррелятора начинается с первого режима. Выходы АЗУ и АЗЭ подключены ко входам множительного устройства 5 через коммутаторы 3 к 4. Блок коэффициентов обеспечивает коэффициент передачи, равный .

Каждый цикл вычисления начинается с записи очередной ординаты исследуемого процесса в блоках / и 2, их перемножения и прибавления полученного произведения с учетом коэффициента на блоке 6 к.ранее накопленной сумме квадратов отсчетов, хранящейся в цервой ячейке интегратора 7. В запоминающем устройстве кроме вновь записанной ординаты хранятся также все ординаты исследуемого процесса, записанные в предыдущих циклах с соответствующим сдвигом друг относительно друга на время Дт, так как щаг дискретизации процесса равен времени элеменггарной задержки. Все ординаты, кроме первой.

умножаются на первую, н полученные парные произведения после прохождения блока коэффициентов прибавляются к соответствующим сумм,ам парных произведений, хранящимся в ячейках интегратора 7. После выполнения всех этих операций ордината x(tj) в блоке 2 и самая «старая ордината - - (т-1):Ат в блоке / стираются, чем н заканчивается /-Й цнкл.

Проделав N циклов коррелятор автоматически переводится во второй режим. При этом коммутаторы отключают входы блока перемножения 5 от выходов блока / и 2 и подключают их к выходу интегратора 7. Вычисление дисперсии оценки производится в соответствии с основной формулой. Значение статистической дисперсии из первой ячейки блока 7 поступает на блок 5, затем квадрат этого

значения через первый конденсатор второго входа блока 2 с коэффициентом «2 запоминается в конденсаторе, включенном в цепь обратной связи блока 2. Остальные значения оценки также возводятся в квадрат, делятся

на Л в блоке коэффициентов, но затем подаются на второй конденсатор второго входа блока 2 и добавляются к содержимому накопительного конденсатора с коэффициентом «4. Аналоговый запоминающий элемент 2 при

этом работает в режиме аналого-днскретного интегратора, т. е. перед каждой подачей очередного слагаемого дисперсии оценки входной конденсатор блока 2 разряжается, а конденсатор Б цепн обратной связи - нет. Благодаря этому происходит накопление слагаемых дисперсии оценки.

Вычисленная таким образом дисперсия оценки с помонхью элемента сравнения сопоставляется с заданной донустимой ошибкой.

В случае, когда она не превышает допустимой ошибки, элемент сравнения выдает в блок управления сигнал останова. Если же она превышает допустимую ошибку, то содержимое ячейки блока 7 перезаписывается в эти же

ячейки с коэффициентом 0,5 с помощью блока 8. Одновременно в блоке коэффициентов переключением его выхода на другой отвод секционированного делителя устанавливается коэффициент деления 2N, в цепи обратной связи

блока 2 разряжается конденсатор, после чего коммутаторы 5 и 4 подключают входы блока перемножения к выходам блоков 1 и 2. Коррелятор начинает новую серию вычислений, затем вычисление дисперсии оценки и сравнение

ее с заданной допустимой погрешностью.

Работа коррелятора во втором режиме протекает но трем циклам: 1) вычисление диснерсии оценки, сравнение ее с заданной допустимой ошибкой; 2) запись значений точек оценкн нз интегратора 7 в блок перезаписи 8 с соответствуюшим коэффициентом; 3) перезапись содержимого блока перезаписи снова в блок 7. Блок / работает как и в первом режиме, т. е. в соответствующие моменты, отстоящие

на время элементарной задержки, в них стираются старые значения отсчета случайного процесса и записываются новые.

Работа коррелятора продолжается до тех пор, пока дисперсия оценки не станет меньше допустимой ошибки.

Предмет изобретения

Аналого-дискретный коррелятор с автоматическим определением интервала наблюдения, содержащий аналоговое запоминающее устройство, связанное через первый коммутатор с первым входом блока перемножения.

второй вход которого подключен к выходу второго коммутатора, соединенного с аналоговым запоминающим элементом; блок коэффициентов, соединенный с аналого-дискретным интегратором, подключенным к блоку управления и блоку перезаписи, соединенным со входом аналого-дискретного интегратора; схему сравнения, соединенную с блоком управления и с блоком задания ошибки, отличающийся тем,

что, с целью упрощения, в нем второй вход аналогового запоминающего элемента соединен с блоком коэффициентов, а его выход подключен ко второму входу схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ДИСКРЕТНЫЙ КОРРЕЛЯТОР | 1971 |

|

SU290291A1 |

| Коррелятор | 1975 |

|

SU525119A1 |

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1972 |

|

SU357565A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОЦЕНКИ ДИСПЕРСИИ ВЗАИМНОЙ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1967 |

|

SU224174A1 |

| Коррелятор | 1976 |

|

SU696474A1 |

| КОРРЕЛЯТОР | 1973 |

|

SU374607A1 |

| КОРРЕЛЯТОР ДЛЯ ОПЕРАТИВНОГО АНАЛИЗА СЛУЧАЙНЫХ ПРОЦЕССОВ | 1970 |

|

SU264789A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Цифровой коррелятор | 1979 |

|

SU851412A1 |

| Аналого-дискретный анализатор спектра | 1978 |

|

SU734740A1 |

Авторы

Даты

1973-01-01—Публикация