Изобретение относится к специализироваеньш средствам вычислительной техники и может быть использовано для решения ряда статистических задач радиоэлектроники, автоматики, физики, связи и в других областях науки и техники.

Известный коррелятор, работающий по условному математическому ожиданию совпадения знаков характеризуется сравнительно невысокой статистической точностью, что ограничивает его применение.

Для повышения точности предлагаемый коррелятор содержит сумматор, схему «ИЛИ, третий, четвертый, пятый и шестой вентили, второй тригер и второй счетчик; вход сумматора подключен к выходу аналого-цифрового преобразователя, управляюнхий вход которого соединен через третий вентиль со вторым вентилем; второй вход и выход сумматора подключены к входным и выходным вентилям запоминаюш.его устройства; один из выходов устройства управления через четвертый и пятый вентили соединены с одним из входов схемы «ИЛИ, второй вход которой через кнопочный контакт подключен к генератору импульсов, а выход соединен с единичным входом первого триггера, нулевой вход которого подключен к схеме сравнения и к единичному входу второго триггера, нулевой вход которого соединен с выходом пятого вентиля; второй

вход пятого вентиля через инвертор и второй переключатель подключен к выходу второго счетчика, вход которого через шестой вентиль соединен с последним выходом дешифратора, подключенным к второму входу четвертого вентиля выход инвертора соединен со вторыми входами третьего и шестого вентилей.

В корреляторе реализуется следуюш,ая зависимость:

р, (аД :.г С 2 у (t, + i)lx (t X, 1 1

где i - число тактов элементарной задержки М.

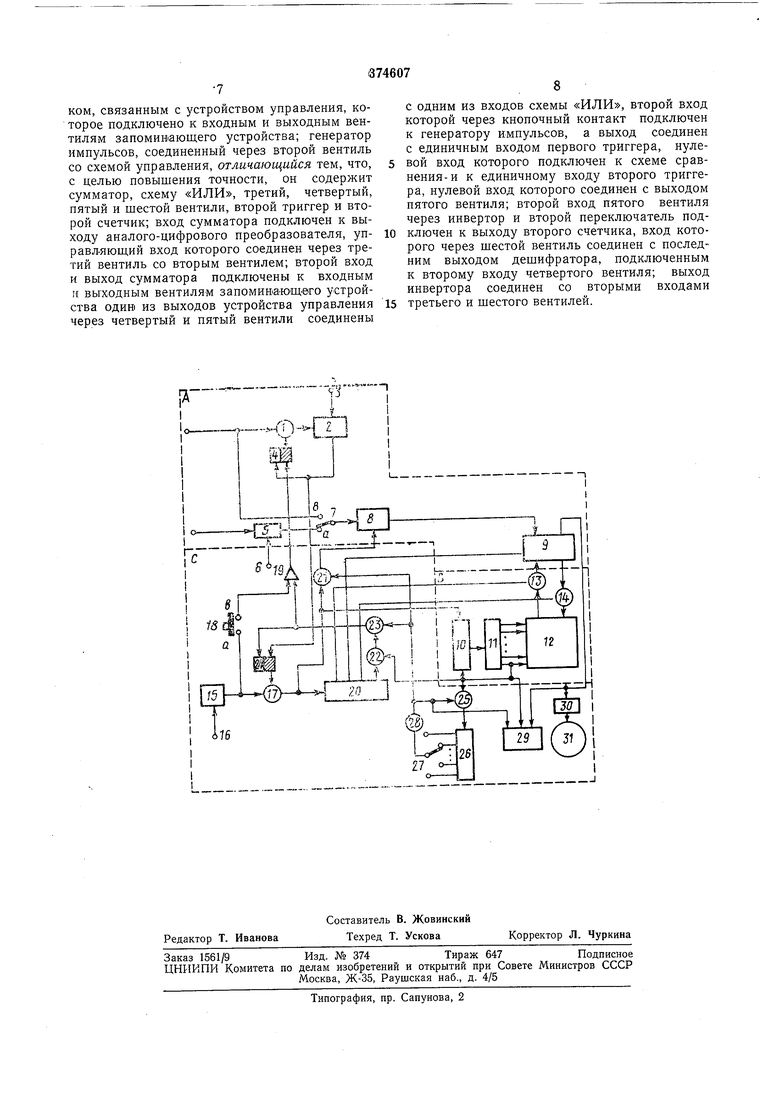

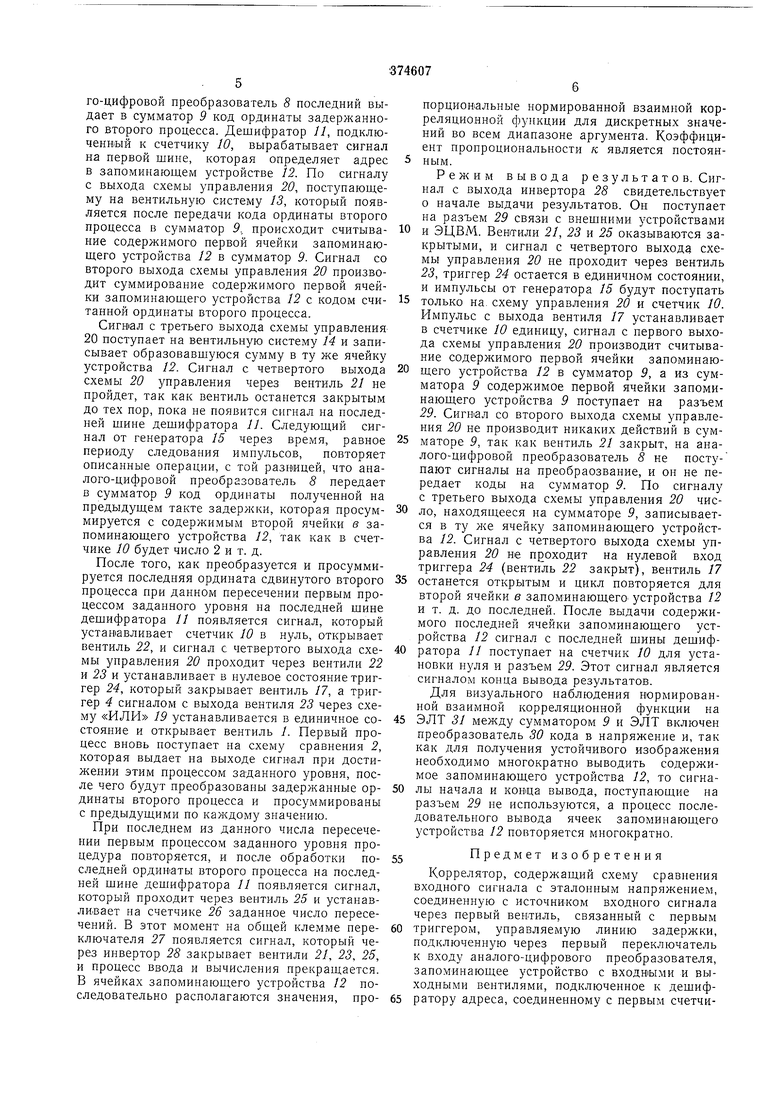

Иа чертеже показана функциональная схема предлагаемого коррелятора. Блок А ввода и вычисления предназначен для ввода ординат исследуемых случайных процессов, стационарно связанных между собой, и вычисления значений взаимной корреляционной и автокорреляционных функций, умноженных на соответствующие коэффициенты. Блок А содержит вентиль /, на вход которого подается первый процесс, а выход подключен к схеме

сравнения 2, предназначенной для выработки сигнала при достижении первым процессом уровня X, который задается по каналу 3 управления. Выход схемы сравнения подключен к нулевому входу триггера 4, единичный выход которого соединен с вентилем 1. На вход 3 . устройства 5 задержки, устанавливаемой перед началом работы по каналу 6 управления, поступает второй исследуемый процесс. Выход устройства задержки соединен с клеммой а переключателя 7, предназначенного для подклю-5 чения одното из исследуемых процессов к аналого-цифровому преобразователю 8. Клемма в переключателя 7 соединена с входом вентиля 1. Аналого-цифровой преобразователь подключен своим выходом к сумматору 9, выпол-Ю няющему операцию сложения. Блок В синхронного накопления предназначен для хранения накопленных 2 значеНИИ корреляционной функции. Он состоит из счетчика 10, подключенного к дешифратору15 11, выходы которого определяют адрес в запоминающем устройстве 12, служащем для хранения накапливаемых значений корреляционной функции. Запоминающее устройство 12 соединено через вентильные системы 1320 к 14 с сумматором 9. Вентильная система 13 предназначена для чтения чисел из запоминающего устройства 12 в, сумматор 9, а вентильная система 14 - для записи результатов сложения из сумматора 9 в запоминающее25 устройство 12. Блок С управления вводом, наконлением и выдачей результатов предназначен для управления вводом в процессе вычислений, накоплением значений корреляционной функции30 и автоматическим выводом результатов на внешние устройства или ЭЦВМ после обработки заданого количества ординат, а также для задания количества ординат исследуемого процесса. Он содержит генератор 15 тактовых35 импульсов, частота которого устанавливается перед началом работы по каналу управления 16. Генератор 15 тактовых импульсов соединен с входом вентиля 77 и с клеммой а кнопоч-40 ного контакта 18, клемм.а в которого соединена через схему «ИЛИ 19 с единичным входом триггера 4. Выход вентиля 17 соединен с входом схемы управления 20, нредназначенной для выработки необходимой последова-45 тельности сигналов на ее выходах, с входом счетчика 10, с входом вентиля 21, выход которого подключен к аналого-цифровому преобразователю 8. Первый из выходов- схемы управления 20 нокключен к вентильной системе50 13, второй - к сумматору 9, третий выход схемы управления 20 соединен с вентильной 14, а четвертый - с входом вентиля 22. Вы-ход вентиля 22 подключен к входу вентиля 23, а выход вентиля 23 - к схеме «ИЛИ 1955 и к нулевому входу триггера 24, едииичаьш выход .которого управляет вентилем 17. Выход схемы сравнения 2 соединен с единичным входом триггера 24. Последний выход дешифратора /) соединен с вентилем 25, со счетчи-$0 ком 10 для установки его в нуль, с вентилем 22 и с разъемом 29 связи с внешними устройствами и ЭЦВМ. Выход вентиля 25 соединен со счетчиком 26, который предназначен для подсчета количества ординат. Вых.оды65 . 4 счетчика 26 подключены к клеммам переключателя 27, предназначенного для останова схемы при накоплении заданного числа ординат, Общая клемма переключателя 27 подключена к инвертору 28, выход которого соединен-, с вентилями 21, 28, 25 и с разъемом 29. Выход сумматора 9 соединен с входом преобразователя 30 кода в напряжение и с разъемом 29. Преобразователь 30 кода в напряжение предназначен для преобразования кодов результатов вычисления и подключен к электроннолучевой трубке (ЭЛТ) 31, для визуальнего наблюдения результатов на ней. Исходная информация вводится в коррелятор непосредственно о виде аналоговых напряжений или напряжений, записанных предварительно на ленту-носитель, Работа коррелятора в основных режимах работы в случае вычисления нормированной взаимной корреляционной функции осуществляется следующим образом, Режим ввода и вычисления. Перед началом работы в зависимости от максимального значения первого исследуемого процесса по каналу управления 3 задается уровень в схеме сравнения 2, по каналу управления 6 - задержка второго процесса относительно первого, равная интервалу аргумента корреляционной функции, а но каналу управления 16 - частота генератора 15 тактовых импульсов. Для вычисления взаимной корреляционной функции переключатель 7 устанавливается в положение а. На переключателе 26 устанавливается число, зависящее от желаемой точности или от длины реализаций процессов, при этом вентили 21, 23 и 25 открыты. Рассмотрим процесс ввода и вычисления на некотором пересечении нервым процессом заданного уровня. Коррелятор запускается путем замыкания кнопочного конта:Кта 18, импульс от генератора 15 устанавливает в единочное состояние триггер 4, который открывает управляемьш им вентиль /. Первый процесс начинает поступать на схему сравнения 2, при этом второй процесс, задержанный устройстарм задержки 5 относительно первого, поступает на аналого-цифровой преобразователь 8. При достижении первым процессом заданного уровня схема сравнения 2 вырабатывает сигнал, который устанавливает триггер 4 в нулевое состояние и управляемый триггером 4 вентиль / закрывается, прекращая поступление нервого процесса на схему сравнения 2. Сигнал с выхода последней устанавливает в единичное состояние триггер 24, который открывает вентиль /7, и первый импульс от генератора 15 через откр.ытый вентиль 17 поступает на аналого-цифровой преобразователь S через открытый вентиль 21, на счетчик 10, устанавливая в нем единицу, и на схему управления 20, которая с приходом нмпульса на ее вход последовательно вь;рабатывает сигналы на всех выходах. С приходом сигнала с выхода вентиля 21 на аналого-цифровой преобразователь 8 последний выдает в сумматор 9 код ординаты задержанного второго процесса. Дешифратор Ц, подключенный к счетчику 10, вырабатывает сигнал на первой шине, которая определяет адрес в запоминающем устройстве 12. По сигналу с выхода схемы управления 20, постунающему на вентильную систему 13, который появляется после передачи кода ординаты второго процесса в сумматор 9, происходит считывание содержимого первой ячейки запоминающего устройства 12 в сумматор 9. Сигнал со второго выхода схемы управления 20 производит суммирование содержимого первой ячейки запоминающего устройства 12 с кодом считанной ординаты второго процесса.

Сигвал с третьего выхода схемы управления 20 поступает на вентильную систему 14 и записывает образовавшуюся сумму в ту же ячейку устройства 12. Сигнал с четвертого выхода схемы 20 управления через вентиль 21 не пройдет, так как вентиль останется закрытым до тех пор, пока не появится сигнал на последней щине дещифратора //. Следующий сигнал от генератора 15 через время, равное периоду следования импульсов, повторяет описанные операции, с той разницей, что аналого-цифровой преобразователь 8 передает в сумматор 9 код ординаты полученной на предыдущем такте задержки, которая просуммируется с содержимым второй ячейки в запоминающего устройства 12, так как в счетчике 10 будет число 2 и т. д.

После того, как преобразуется и просуммируется последняя ордината сдвинутого второго процесса при данном пересечении первым процессом заданного уровня на последней щине дещифратора // появляется сигнал, который устанавливает счетчик 10 в нуль, открывает вентиль 22, и сигнал с четвертого выхода схемы управления 20 проходит через вентили 22 и 23 и устанавливает в нулевое состояние триггер 24, который закрывает вентиль 17, а триггер 4 сигналом с выхода вентиля 23 через схему «ИЛИ 19 устанавливается в единичное состояние и открывает вентиль /. Первый процесс вновь поступает на схему сравнения 2, которая выдает на выходе сигнал при достижении этим процессом заданного уровня, после чего будут преобразованы задержанные ординаты второго процесса и просуммированы с предыдущими по каждому значению.

При последнем из данного числа пересечении первым процессом заданного уровня процедура повторяется, и после обработки последней ордин1аты второго процесса на последней щине дешифратора 11 появляется сигнал, который проходит через вентиль 25 и устанавливает на счетчике 26 заданное число пересечений. В этот момент на общей клемме переключателя 27 появляется сигнал, который через инвертор 28 закрывает вентили 21, 23, 25, и процесс ввода и вычисления прекращается. В ячейках запоминающего устройства 12 последовательно располагаются значения, пропорциональные нормированной взаимной корреляционной функции для дискретных значений во всем диапазоне аргумента. Коэффициент пропроциональности к является постоянным.

Режим вывода р е з у л ьт а т о в. Сигнал с выхода инвертора 28 свидетельствует о начале выдачи результатов. Он поступает на разъем 29 связи с внешними устройствами

и ЭЦВМ. Вентили 21, 23 и 25 оказываются закрытыми, и сигнал с четвертого выхода схемы управления 20 не проходит через вентиль 23, триггер 24 остается в единичном состоянии, и импульсы от генератора 15 будут поступать

только на, схему управления 20 и счетчик 10. Импульс с выхода вентиля 17 устанавливает в счетчике 10 единицу, сигнал с первого выхода схемы управления 20 производит считывание содерлсимого первой ячейки запоминающего устройства 12 в сумматор 9, а из сумматора 9 содержимое первой ячейки запоминающего устройства 9 поступает на разъем 29. Сигнал со второго выхода схемы управления 20 не производит никаких действий в сумматоре 9, так как вентиль 21 закрыт, на аналого-цифровой преобразователь 8 не поступают сигналы на преобраозвание, и он не передает коды на сумматор 9. По сигналу с третьего выхода схемы управления 20 число, находящееся на сумматоре 9, записывается в ту же ячейку запоминающего устройства 12. Сигнал с четвертого выхода схемы управления 20 не проходит на нулевой вход триггера 24 (вентиль 22 закрыт), вентиль 17

останется открытым и цикл повторяется для второй ячейки в запоминающего устройства 12 и т. д. до последней. После выдачи содержимого последней ячейки запоминающего устройства 12 сигнал с последней щины дещифратора 11 поступает на счетчик 10 для установки нуля и разъем 29. Этот сигнал является сигналом конца вывода результатов.

Для визуального наблюдения нормированной взаимной корреляционной функции на

ЭЛТ 31 между сумматором 9 и ЭЛТ включен преобразователь 30 кола в напряжение и, так как для получения устойчивого изображения необходимо многократно выводить содержимое запоминающего устройства 12, то сигналы начала и конца вывода, поступающие на разъем 29 не используются, а процесс последовательного вывода ячеек запоминающего устройства 12 повторяется многократно.

Предмет изобретения

Коррелятор, содержащий схему сравиения входного сигнала с эталонным напряжением, соединенную с источником входного сигнала через первый вентиль, связанный с первым

триггером, управляемую линию задержки, подключенную через первый переключатель к входу аналого-цифрового преобразователя, запоминающее устройство с входными и выходными вентилями, подключенное к дещифратору адреса, соединенному с первым счетчиком, связанным с устройством управления, которое подключено к входным и выходным вентилям запоминающего устройства; генератор импульсов, соединенный через второй вентиль со схемой управления, отличающийся тем, что, с целью повышения точности, он содержит сумматор, схему «ИЛИ, третий, четвертый, пятый и шестой вентили, второй триггер и второй счетчик; вход сумматора подключен к выходу аналого-цифрового преобразователя, управл-яюш,ий вход которого соединен через третий вентиль со вторым вентилем; второй вход и выход сумматора подключены к входным м выходным вентилям запомивающего устройства ОДИН1 из выходов устройства управления через четвертый и пятый вентили соединены

с одним из входов схемы «ИЛИ, второй вход которой через кнопочный контакт подключен к генератору импульсов, а выход соединен с единичным входом первого триггера, нулевой вход которого подключен к схеме сравнения-и к единичному входу второго триггера, нулевой вход которого соединен с выходом пятого вентиля; второй вход пятого вентиля через инвертор и второй переключатель подключей к выходу второго счетчика, вход которого через шестой вентиль соединен с последним выходом дешифратора, подключенным к второму входу четвертого вентиля; выход инвертора соединен со вторыми входами

третьего и шестого вентилей.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯТОР | 1972 |

|

SU432510A1 |

| УСТРОЙСТВО для ВЫЧИСЛЕНИЯ линий'РЕГРЕССИИ | 1971 |

|

SU290282A1 |

| Цифровой коррелятор | 1982 |

|

SU1045233A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ЗНАКОВЫЙКОРРЕЛЯТОР | 1971 |

|

SU302731A1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬ ЗАКОНОВ РАСПРЕДЕЛЕНИЯ | 1973 |

|

SU369575A1 |

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР С УСРЕДНЕНИЕМ | 1967 |

|

SU190097A1 |

| Устройство для определения корреляционной функции | 1987 |

|

SU1501086A1 |

| Устройство для определения взаимной корреляционной функции | 1987 |

|

SU1427383A1 |

| Коррелятор | 1976 |

|

SU696474A1 |

Т5

I

;-,...„|D-.J 2I

.-.

V

7

.

Hj5 -г

А j L L i-f-1- -I

Авторы

Даты

1973-01-01—Публикация