Предлагаемое устройство относится к опециалнзированным вычислительным устройствам, иредиаэначеиным для оценки вероятностно-статистических характеристик нроцессов, характеризующих динамические свойства систе.м уиравления и контроля.

Исследования динамических свойств технологических ироцессов систем уиравления п контроля с целью технической диагностики, идентификации или адаптивного управления этимон ироцесса.ми и системами неразрывпо связаны с оценкой статистических свойств процессов, характеризующих объекты исследования.

При определении характеристик процессов в условиях нормальной .эксплуатации, когда время .иаблюдеиия процессов огра.ничивается до .минимально .возможного, о-пределяемого затратами па сбор и обработку статистических даиных, широкое распространение получили непараметрические методы оцеиивапия статистических характеристик.

Пзвестные устройства для сцепки вероятiiOCTHO-статистических характеристик случайных нроцессо;в позволяют получить оцепку либо регрессии случайных процессов, либо услов и ой дисперсии.

стве предусмотрены дополнительпые олоки и такое их соединение, которое обеспечивает заноминацие вычисленных зиачеиий регрессии случайных процессов, центрирование случайных процессов относительно лииии условных мате.матических ожиданнй и носледующее возведение полученных результатов в квадрат.

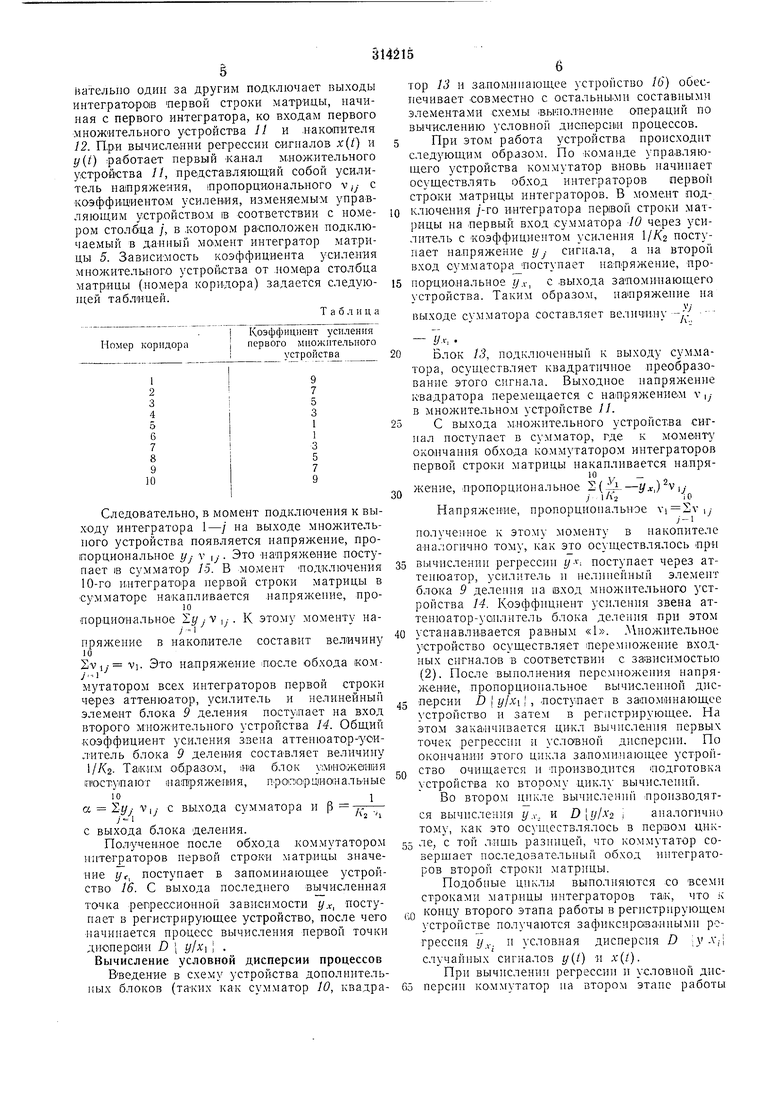

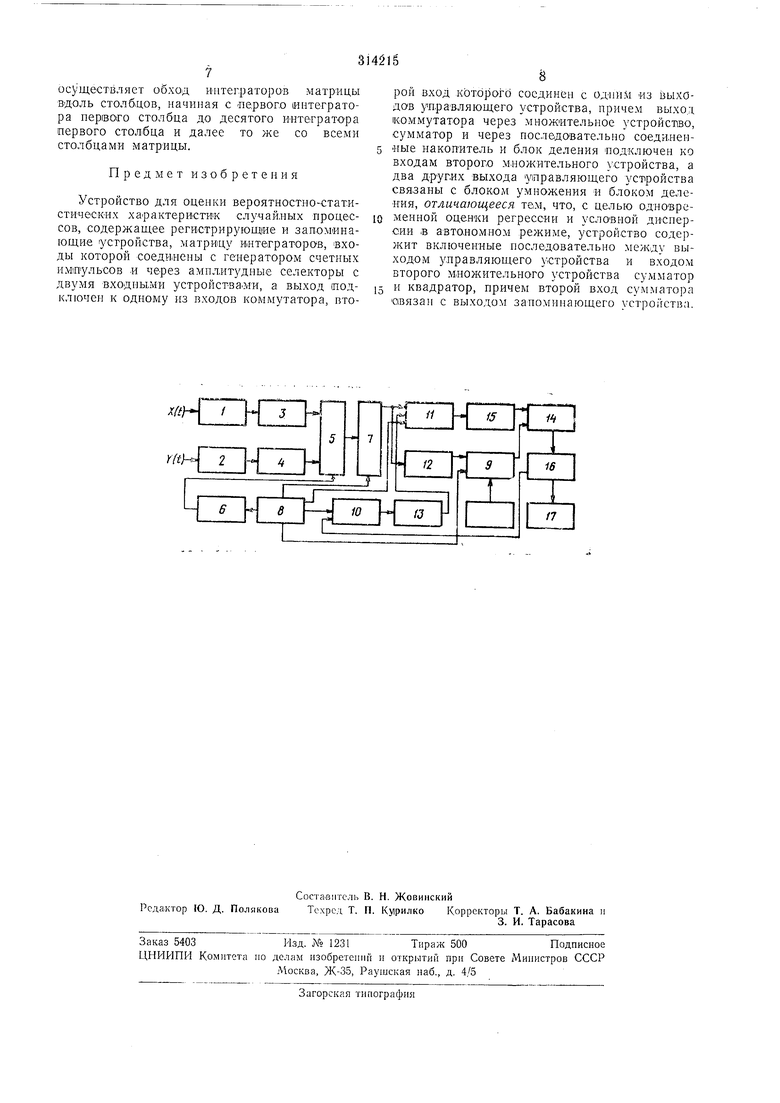

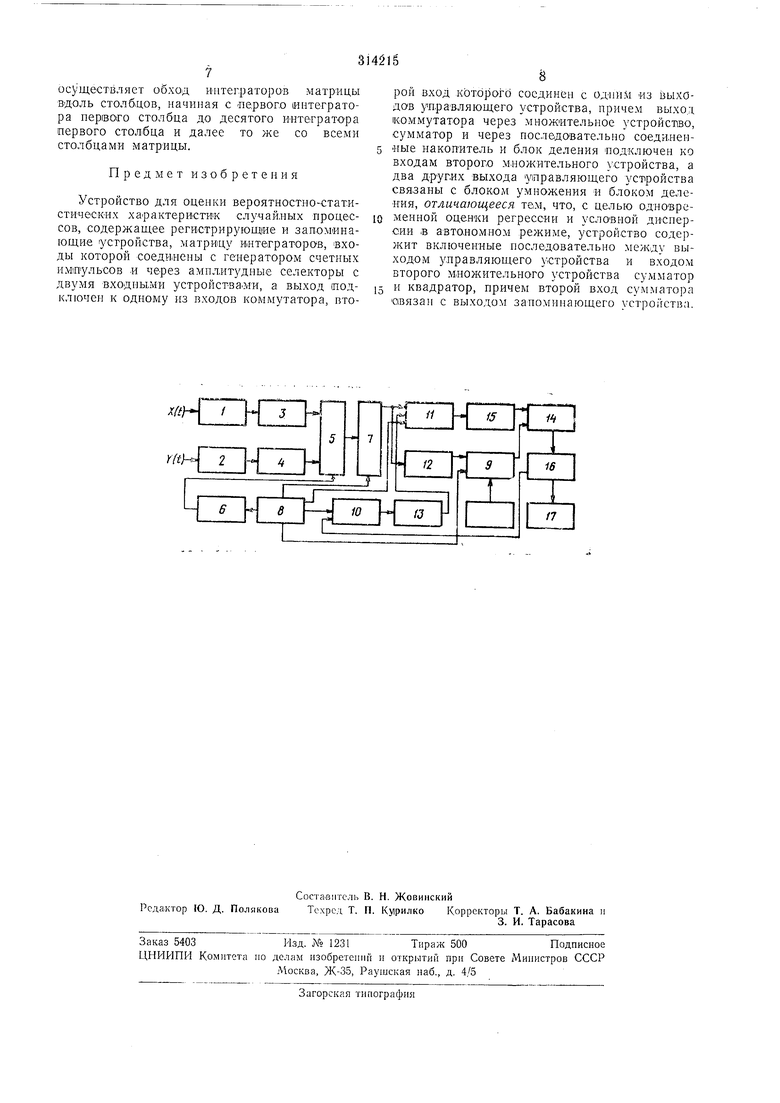

Па чертеже лредставлена структ рная схе.ма одного из возможных вариантов устройства для оцерпчи вероятпостно-статнстическ 1х характеристик дина.мнческих процессов.

Исследуемые сигиалы подаются иа «входиые устройства / и 2, каждое из которых состоит, например, из интегратора средиего значения и сумматора, ностроеиных на усилителях постоянного тока с глубокой отрицательной обратной связью. Выходы усилителей соединены с ам1нли1удными селектора.м-и 3 и 4, которые представляют еобой 10-каиальиые устройства с общим входом. Каждый канал состоит из верхнего и нижнего амилнтудиого селекторов, двух формирующнх и вычитающего устройств. АмиЛНтудпые селекторы соедниеиы со в.ходами матр1щы 5 интеграторов, которая состоит из 10 строк и 10 столбцов (по числу каналов амплитудных селекторов). Каждый интегратор матрицы имеет типовую диодную ячейку «П со строчным и столбце1ВЫ.М входами и наконнтель и.мпульсов со входом для счетных импульсов, поступающих с генератора 6 счетных имиульсов. Строчные ВХОДЫ интеграторов, расположенных в одной и той ж« строке матрицы, подключены к входной ШЕне строки соответствующего канала амллитудного селектора 3 таким образом, что входная шияа первой строки матрицы соединена с выходом первого канала амплитудного селектора, входная шина второй строки - с выходом второго ка-нала амплитудного селектора и так далее до 10-й строки. Столбцевые входы интеграторов, расположенных в одноименном столбце матрицы интеграторов, .подключены к входной шине столбца. Столбцевые входные шипы подключаются к соответствуюш,им 10 выходам амплитудного селектора 4. Выход каждого из интеграторов матрицы подключен к соответствуюш ему входу коммутатора 7. Таким образом, коммутатор имеет 100 сигнальных -входов. Управляюш,ее устройство 8 уста;навл:ивает соответствуюш,ие режимы работы всего устрой|ства. Выходы его соединены с генератором счетных имлульсов, коммутатором 7, блоком 9 деления, сумматором 10 и множительным устройством 11. Второй вход множительного устройства соединен с выходом коммутатора и со входов накопителя 12. Лиюжительное устройство состоит из двух каналов. Пер;вый канал представляет собой усилитель постоянного тока, охваченный глубокой отрицательной обратной связью, с изме шемыМ коэффициентом усиления. Структура второго канала множительного устройства построена по типовой схеме аналоговых блоков умножения, широко используемых в выч ислительной технике. Вход второго канала множительного устройства соединен с выходом квадратора 13. В качестве квадратора в устройстве могут быть иопользоваиы, например, широко применяемые -в вычислительной технике элементы с квадратичной статической характеристикой. Вход квадратора подключен к выходу сумматора 10, собранного на базе типового усилителя постоянного тока с глубокой отрицательной обратной связью. Два входа сумматора подключены соответственно к выходам упр.авляюшего и запоминающего устройств. Накопитель представляет собой интегратор, собранный на базе типового усилителя постоянного тока с глубокой отрицательной обратной связью. Выход накопителя подключен к блоку 9 деления. Блок .деления состоит из аттенюатора, усилителя постоянного тока, охваченного глубокой отрицательной обратной связью с регулируемым коэфф1щиентом усиления и нелинейного элемента, имеющего статическую .характеристику в виде обратной функции. Выход блока деления подключен ко второму множительному устройству 14, второй вход которого соединен с выходом сум1матора 15. Последний представляет собой интегратор, со бранный на базе усилителя постоянного тока с глубокой отрицательной обратной связью. Второе множительное устройство 14 имеет структуру, аналогичную структуре второго канала множительного устройства 11. Выход блока деления подключен к запоминающему устройству 16, представляющему собой, нанример, усилитель ностоянного тока с емкостно-реостатной обратной связью. В качестве регистрирующего устройства 17, подключенного к выходу запоминающего устройст-ва, МОжет быть иснользован, напр.имер, электронный нечатающий вольтметр типа ЭЦПВ-3, а в качестве блока питания - широко 1применяемый в вычислительной технике стабилизиров.анный выпрямитель типа ЭСВ-3. Работа устройств включает два этапа; первичную обработку и накопление исходной информации; (Вычисление условных средних значений случайных сигналов и условных дисперсий этих сигналов. На иервом этапе работа устройства состоит в том, что интеграторы среднего значения входных устройств осредняют .на некотором интервале наблюдения входные сигналы, определяя тем самым их -математические ожидания. Но окончании измерения средних значений сигналов исследуемые сигналы центрируются IB усилителях-сумматорах входных устройств, и одновременно изменяется их динамический диапазон до величины +10 в. При этом фиксируются коэффициенты усиления усилителя-сугмматора сигнала устройства 1 и коэффициент усилителя-сумматора сигнала устройства 2. С усилителей-сумматоров сигналы поступают на входы амплитудных селекторов 3 и 4, нреобразующих их в им пульсы напряжения, длительности которых пропорциональные времени пребывания сигналов в пределах коридоров амплитудных селекторов. Путем надлежащей коммутации выходов амплитудных селекторов с матрицей интеграторов в последней обеспечивается интегрирование счетных импульсов, т. с. фиксация в интервале наблюдения частоты совместного появления событий. На этом нервый этап работы устройства заканчивается, наступает второй этап - вычисление условны.х средних значений и условных дисперсий случайных сигналов. Работу устройства рассмотрим на примере вычисления регрессии ух сигнала y(i) относительно x(i) и условной дисперсии Искомые зависи1могти получаются путем вычислений по формулам: ( W-)-f Д (i--у., )v Vел -i ,J -;-iгде KZ - коэффициент усиления сигнала y(t) во входном устройстве 2; у J-- среднее значение напряжения у-го коридора амплитудного селектора 4. Вычисление регрессии у вателыю один за другим подключает выходы интеграторов первой строки матрицы, начиная с первого интегратора, ко входам первого множительного устройства 11 и .наканителя 12. П.р.и вычислении регрессии сигналов х(/) и /(/) -работает первый канал множительного устройства 1, представляющий собой усилитель напряжения, пропорционального v/y с коэффициентом усиления, изменяемым управляющим устройством IB соответствии с номером столбца /, в .котором расположен подключаемый в данный интегратор матрицы 5. Зависимость коэффициента усилеиия множительного устройства от .HOMeipa столбца матрицы (.номера коридора) задается следуюН1:ей таблицей. Таблица Коэффициент усиления Номер коридора первого миожптельного устройства Следовательно, в момент подключения к выходу интегратора 1-/ на выходе множительного устройства появляется напряжение, прошорциональное г/у v ly. Это цаиряжение поступает IB сумматор /5. В момент подключения 10-го интегратора первой строки матрицы в сумматоре накапливается напря/кепие, пропорциональное Zw . v , . К ЭТОМУ моменту на; -1 пряжение в накопителе составит величину Svi.- V. Это на. |П.осле обхода коммутатором всех интеграторов первой строки через аттенюатор, усилитель и нелинейный элемент блока 9 деления поступает на вход второго множительного устройства 14. Общий .коэффициент усиления звена аттенюатор-усилитель блока 9 деления составляет величину 1//(2. Таитм о бразом, блок удпножвния пЮС туп а ют ill аир я я, n pcrjop щион а л ьп ы е СоJ a 2-y/V|- с выхода сумматора и В - Ч 1 с выхода блока деления. Полученное после обхода коммутатором интеграторов первой строки матрицы значение г/г, поступает в запоминаюндее устройство 16. С выхода последнего вычисленная точка регрессионной зависимости ух, поступает в регистрирующее устройство, после чего начинается процесс вычисления первой точки д пене рои и D y/Xi . Вычисление условной дисперсии процессов тор 13 и за.номинающее устройство 16) обеспечивает совместно с остальными составными элементами схемы вынолнен ие операций по вычислению условно днсиерсши процессов. При этом работа устройства происходит следующим обр:азом. По :команде управляющего устройства коммутатор вновь начинает осуществлять обход интеграторов оервон строки матрицы интеграторов. В момент подключения /-ГО интегратора первой строки матрицы на .первый вход сумматора 10 через усилитель с коэффициентом усилення l/Kz поступает на.нряжение г/у сигнала, а на второй вход суммато.ра поступает напряжение, пропорцио.нальное .г/л-, с .выхода запоминающего устройства. Таким образом, напряжение на выходе сумматора составляет величину -- - //Л-, . Блок 13, подключенный к выходу сумматора, осуществляет квадратичное цреобразованне этого сигнала. Выходное напряжение квадратора неремещается с напряжением v ,j в множительном устройстве 11. С выхода множительного устройства сигнал поступает в сумматор, где к моментуокончания обхо.да коммутатором интеграторов первой строки матрицы накапливается на.пря V жеиие, пропорциональное 2{-ii--УХ М i Лг о Напряжение, пропорциопальное vi Sv ly ;-i полученное к этому моменту в накопителе аналогично тому, как это осуществлялось прИ вычисленнн регрессии y-V; поступает через аттенюатор, усилитель и нелинейный элемент блока 9 деления на вход множительного устройства 14. Коэффициент усиления звена аттенюатор-уоилитель блока деления при этом устанавливается равным «1. Множительное устройство осуществляет перемножение входных сигналов в соответствии с зависимостью (2). После выполнения перемножения напряжение, пропорциональное вычисленной дисперсии D I у1х , поступает в запоминающее устройство и затем в регистрирующее. На этом закапчивается цикл вычисления первых точек регрессии и условной дисперсии. По окончании этого цикла запоминающее устройство очищается и производится подготовка устройства ко второму циклу вычислений. Во втором цикле вычислений пронзводятся вычисления г/л-, и D y/Xz аналогич)1о тому, как это осуществлялось в nepiBOM цикле, с той лишь разницей, что коммутатор совершает последовательный обход интеграторов второй строки матрицы. Подобные циклы выполняются со всеми строками матр.ицы инте.граторов , что к концу второго этапа работы в регнстрпрующем устройстве получаются зафиксираваиными регрессия г/д.. и условная дисперсия D у .v,-i случайных сигналов г/(/) и x(i).

осуществляет обход интеграторов матрицы вдоль столбцов, начиная с Первого интегратора первого столбца до десятого ИНтегратора первого столбца и далее то же со всеми столбцами матрицы.

Предмет изобретения

Устройство для оценки вероятностпо-статистическ-их характеристик случайлых процессов, содержащее регистрирующие и запоминающие устройства, матрицу интеграторо-в, входы которой соединены с генератором счетных им1пульсов и через амплитудные селекторы с двумя входны,ми устройства ми, а выход подключен к одному из входов коммутатора, второй вход которого соединен с одним «з 1зыходов управляющего устройства, причем выход всоммутатора через множительное устройст1во, сумматор и через носледавательно соеди.нен«ые накопитель и блок деления подключен ко входам второго множительного устройства, а два других выхода управляющего успройства связаны с блоком умножения и блоком деления, отличающееся тем, что, с целью одноъременной оценки регрессии и условной диснерсии в автоломном режиме, устройство содержит включенные последовательно между выходом злравляющсго устройства и входом второго миожительного устройства сумматор

и квадратор, причем второй вход сумматора связан с выходом запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1972 |

|

SU357565A1 |

| Устройство для статистической обработки информации | 1974 |

|

SU525101A1 |

| УСТРОЙСТВО для ОЦЕНКИ ВЕРОЯТНОСТНО- СТАТИСТИЧЕСКИХ ХАРАКТЕРИСТИК ДИНАМИЧЕСКИХПРОЦЕССОВ | 1970 |

|

SU269612A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU387391A1 |

| Устройство для обработки изображений | 1986 |

|

SU1388915A1 |

| УСТРОЙСТВО для ОЦЕНКИ ДОСТОВЕРНОСТИ БИНАРНЫХ СИГНАЛОВ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1972 |

|

SU351332A1 |

| Нелинейное корректирующее устройство | 1980 |

|

SU951231A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Двумерный цифровой фильтр | 1986 |

|

SU1320876A1 |

| Устройство для измерения корреляционногоОТНОшЕНия дВуХ СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU851420A2 |

Xffi

Даты

1971-01-01—Публикация