Предлагаемое изобретение относится к вычислительной технике и может быть использовано в вычислительных и управляющих системах повышенного быстродействия, ядерной электронике и в технике измерений наносекундных процессов.

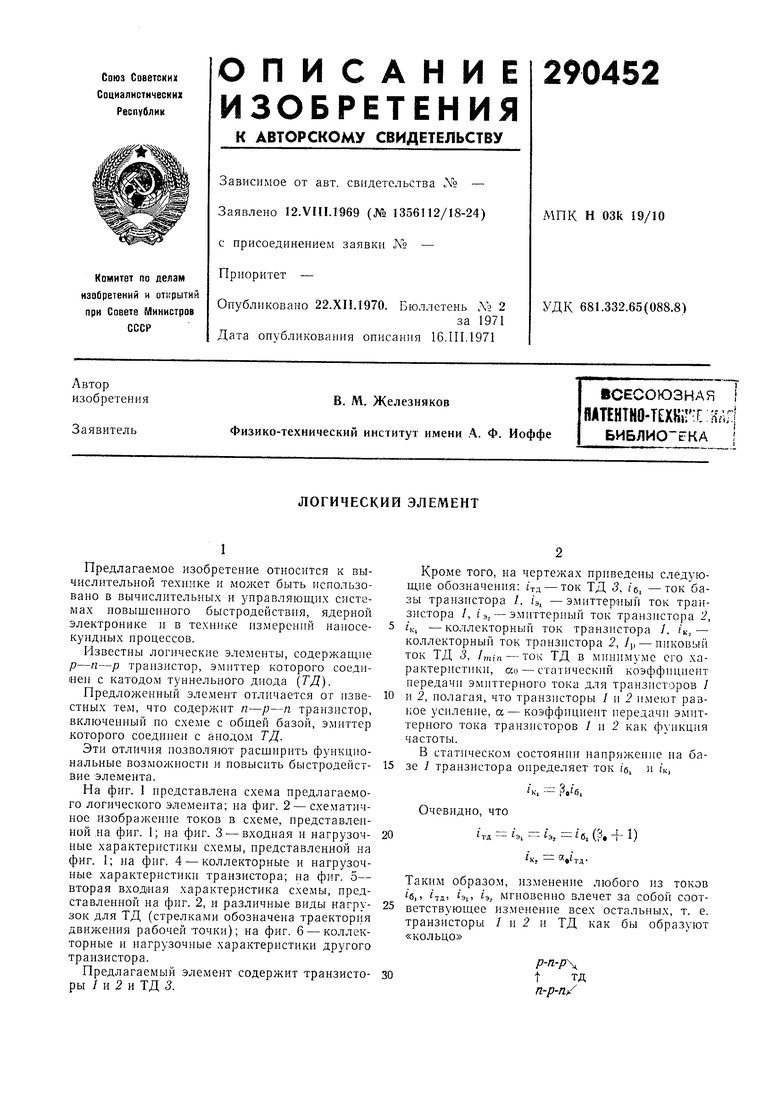

Известны логические элементы, содержащие р-п-р транзистор, эмиттер которого соединен с катодом туннельного диода (ТД).

Предложенный элемент отличается от нзвестных тем, что содержит п-р-я транзистор, включенный по схеме с общей базой, эмиттер которого соединен с анодом ТД.

Эти отличия иозволяют расширить функциональные возможности и повысить быстродействие элемента.

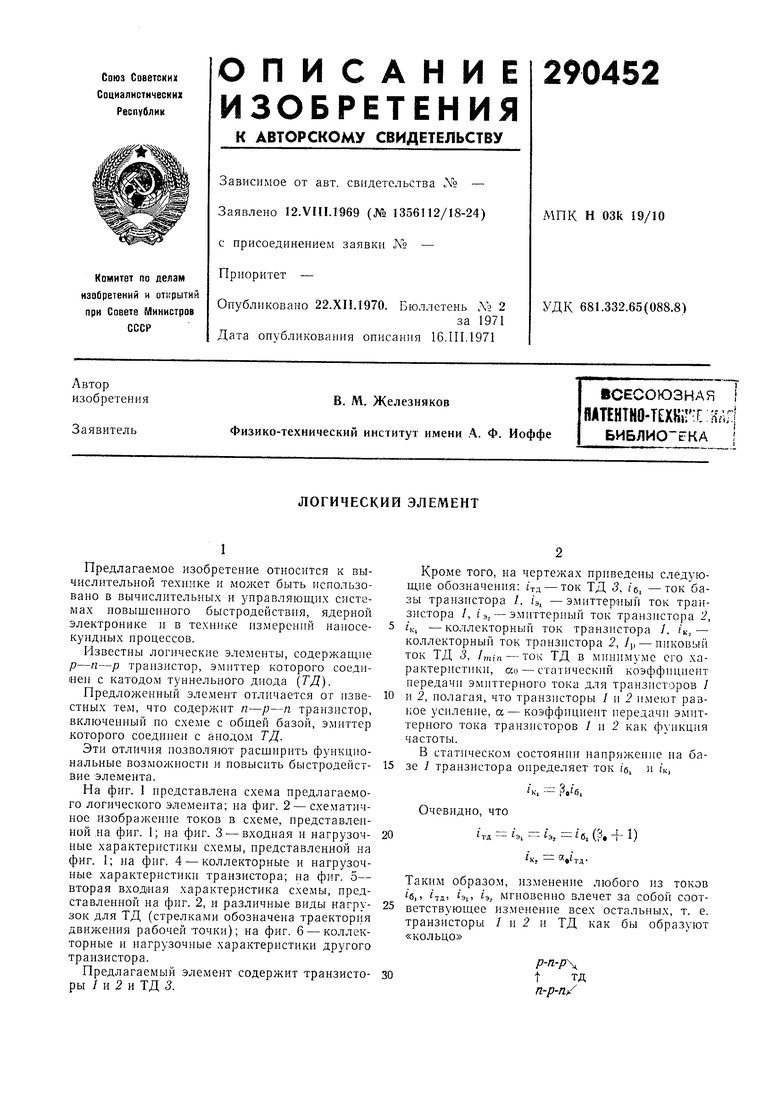

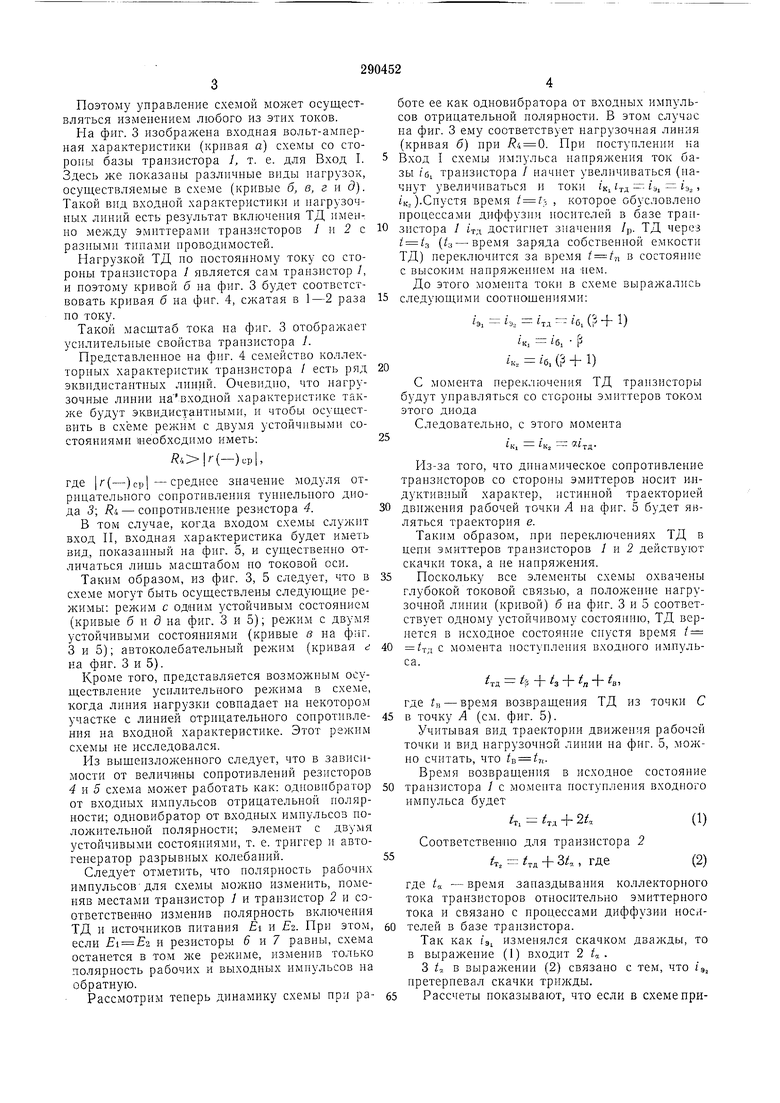

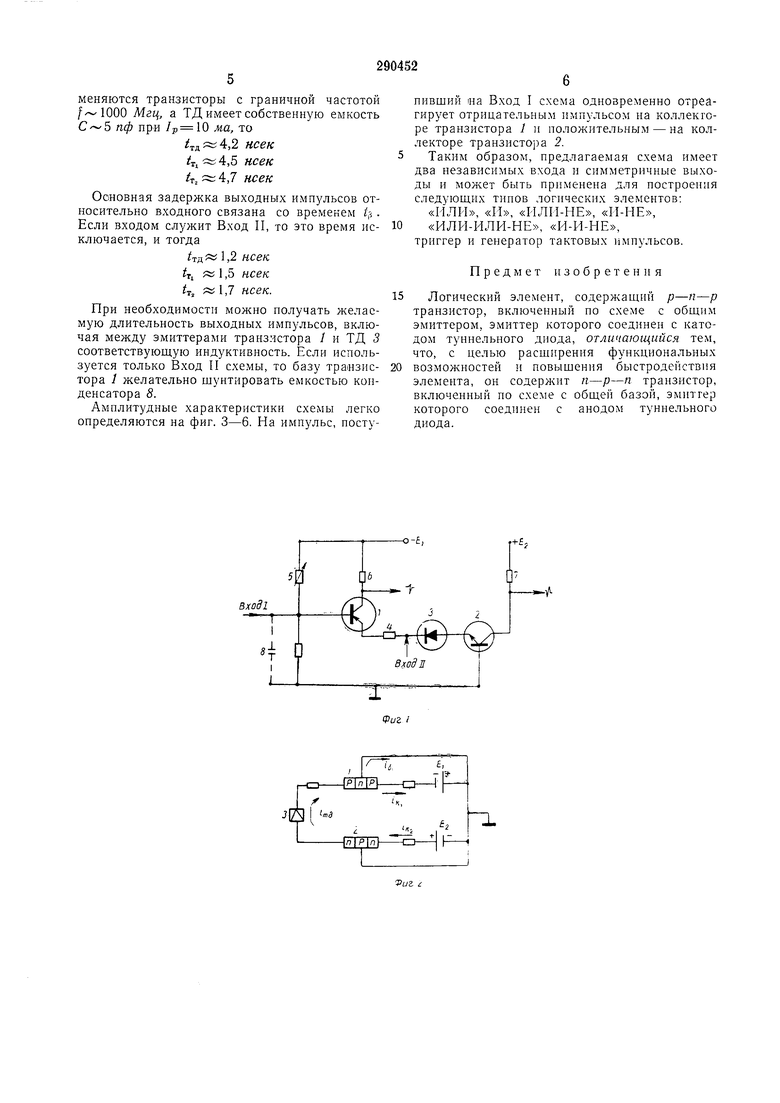

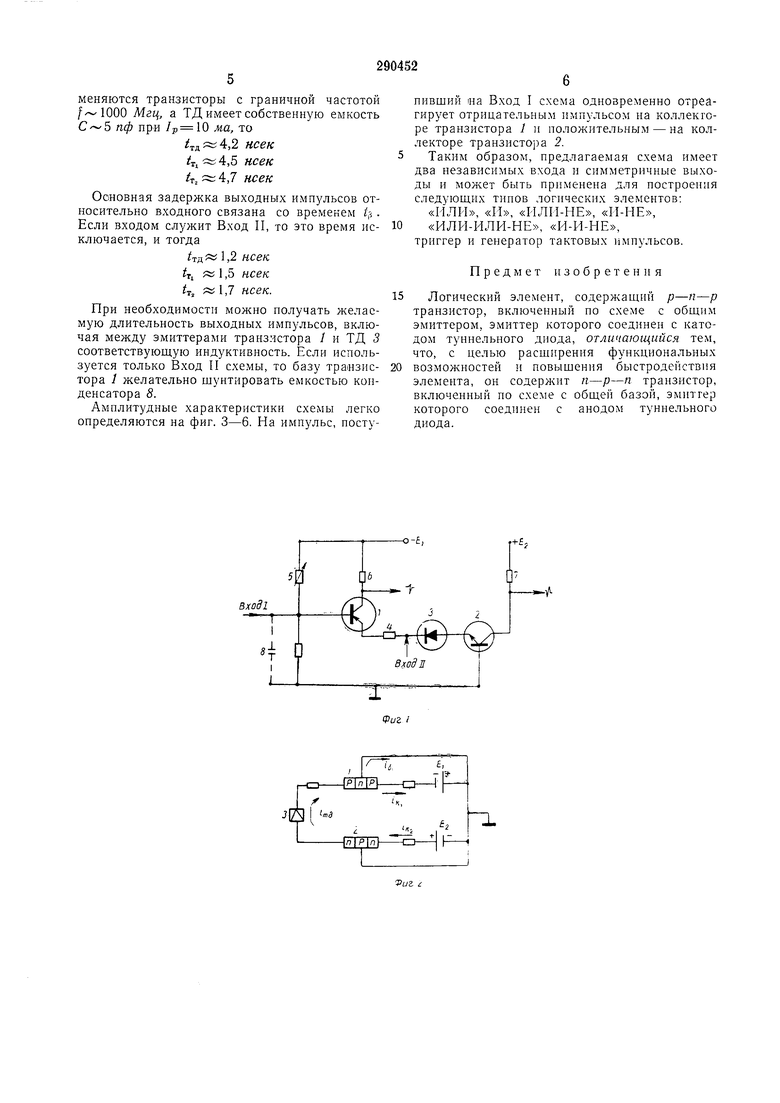

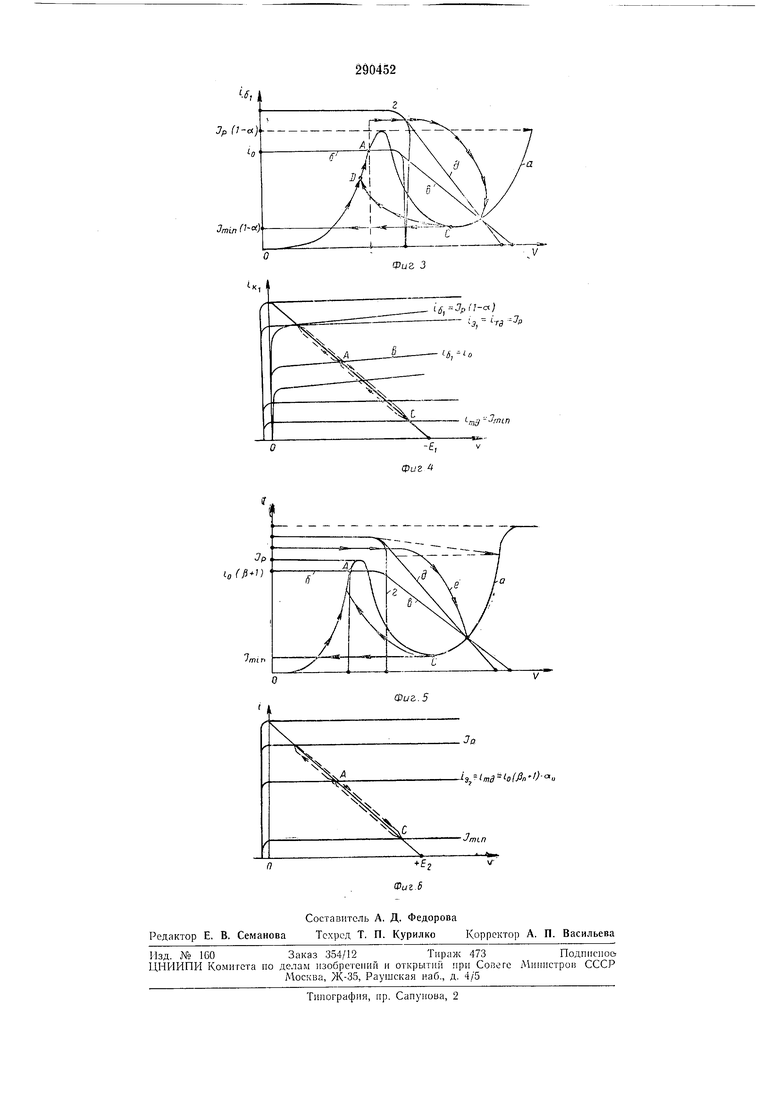

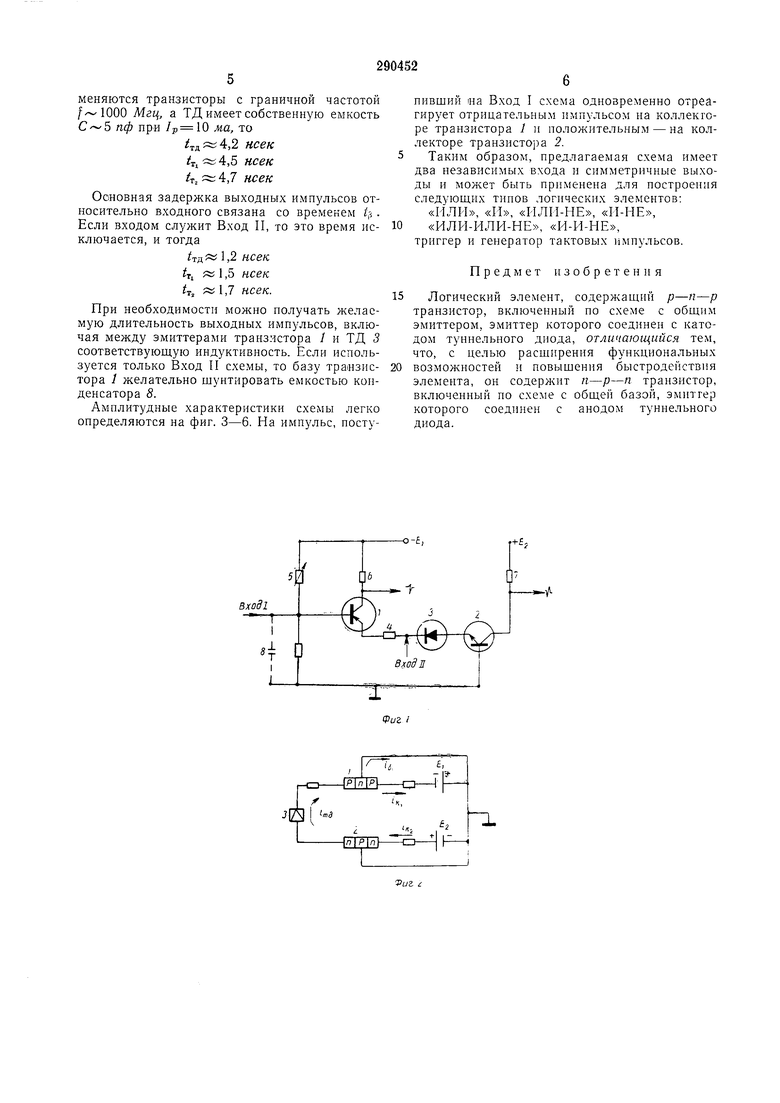

На фиг. 1 иредставлена схема предлагаемого логического элемента; на фиг. 2 - схематичное изображение токов в схеме, представленной .на фиг. 1; на фиг. 3 - входная и нагрузочные характеристики схемы, представленной на фиг. 1; на фиг. 4 - коллекторные и нагрузочные характеристики транзистора; на фиг. 5- вторая входная характеристика схемы, представленной на фиг. 2, и различные виды нагрузок для ТД (стрелками обозначена траектория движения рабочей точки); на фиг. 6 - коллекторные и нагрузочные характеристики другого транзистора.

Кроме того, на чертежах приведены следующие обозначения: гтд - ток ТД 3, /6i -ток базы транзистора /, (э, -эмиттериый ток транзистора /, гэ, - эм1ггтер 1ый ток транзистора 2,

/к, -коллекторный ток транзистора /, /к,- коллекторный ток транзистора 2, /р - пиковый ток ТД 3, 1,пгп - ток ТД в мшшмуме его характеристики, аи - статический коэффициент передачи эмиттерного тока для транзисторов /

и 2, иолагая, что транзисторы / и 2 имеют равное усиление, а - коэффициеит передачи эмиттерного тока транзисторов 1 и 2 как фуикция частоты.

В статическом состоянии напр51жение на базе / транзистора определяет ток Гб и (к,

к, З.гб,

Очевидно, что

, -гбЛЗ,+ 1)

к, : «втдТаким образом, 11зменение любого из токов Ч, гтд Ь,, гэ, мгновенно влечет за собой соответствующее изменение всех остальных, т. е. транзисторы / и 2 и ТД как бы образуют «кольцо

Поэтому управление схемой может оеуществляться изменением любого из этих токов.

На фиг. 3 изображена входная вольт-амперная характеристики (кривая а) схемы со стороны базы транзистора /, т. е. для Вход I. Здесь же показаны различные виды нагрузок, осуществляемые в схеме (кривые б, в, г и д). Такой вид входной характеристики и нагрузочных линий есть результат включения ТД именно между эмиттерами транзисторов / и 2 с разными тинами нроводимостей.

Нагрузкой ТД но постоянному току со стороны транзистора / является сам транзистор 1, и ноэтому кривой б на фиг. 3 будет соответствовать кривая б на фиг. 4, сжатая в 1-2 раза но току.

Такой масштаб тока на фиг. 3 отображает усилительные свойства траизистора 1.

Нредставленное на фнг. 4 семейство коллекторных характеристик транзистора / есть ряд эквидистантных линий. Очевидио, что нагрузочные линии навходиой характеристике также будут эквидистантными, и чтобы осуществить в схеме режим с двумя устойчивыми состояниями необходимо иметь;

( -),р ,

где |г(-)ср|-среднее значение модуля отрицательного сонротивления туннельного диода 3; Ri - сонротивление резистора 4.

В том случае, когда входом схемы служит вход II, входная характеристика будет иметь вид, показанный на фиг. 5, и существенно отличаться лишь масштабом по токовой осн.

Таким образом, из фиг. 3, 5 следует, что в схеме могут быть осуществлены следующие режимы: режим с одним устойчивым состоянием (кривые б и б на фиг. 3 и 5); режим с двумя устойчивыми состояниями (кривые в на фмг.

3и 5); автоколебательный режим (кривая на фиг. 3 и 5).

Кроме того, представляется возможным осуществление усилительного режима в схеме, когда линия нагрузки совнадает на некотором участке с линией отрицательного сопротивления на входной характеристике. Этот режим схемы не исследовался.

Р1з вышеизложенного следует, что в зависимости от величины сопротивлений резисторов

4и 5 схема может работать как: одновибратор от входных имиульсов отрицательной полярности; одновибратор от входных имнульсов ноложнтельиой полярности; элемент с двумя устойчивыми состояниями, т. е. триггер и автогенератор разрывных колебаний.

Следует отметнть, что полярность рабочих импульсов для схемы можно изменить, поменяв местами транзистор / и транзистор 2 и соответственно изменив полярность включения ТД и источников питания Ei и Ez. Нри этом, если Ei Ez и резисторы 5 и 7 равиы, схема останется в том же режиме, изменив только полярность рабочих и выходных импульсов на обратную.

боте ее как одновибратора от входных импульсов отрицательной полярности. В этом случае на фиг. 3 ему соответствует нагрузочная линия (кривая б) ири R,Q. При поступлении на Вход I схемы импульса наиряжения ток базы (6i транзистора / начнет увеличиваться (иачнут увеличиваться и токи IK, -- гэ, - 1э.,, гк,).Спустя время / -, , которое обусловлено процессами диффузии иосителей в базе траизистора / 1тд достигиет значеиня /р. ТД через

4 (3 - время заряда собственной емкости

ТД) переключится за время / /„ в состояние

с высоким напряжением па нем.

До этого момента токи в схеме выражались

следующнмн соотношениями:

/э, - гэ, гтл - iu, ( + 1) IK, /б, fi

- б. (г + 1)

С момента переключения ТД транзисторы будут унравляться со стороны эмнттеров током этого днода

Следовательно, с этого момента

-.

«к, - г к, - .

Из-за того, что дниамическое сонротивление транзисторов со стороны эмиттеров носит индуктивный характер, истиниой траекторией

движения рабочей точки А иа фиг. 5 будет являться траектория е.

Таким образом, при переключениях ТД в цепи эмиттеров транзисторов 1 и 2 действуют скачки тока, а ие наиряжения.

Поскольку все элементы схемы охвачены глубокой токовой связью, а положение нагрузочной линии (кривой) б на фиг. 3 и 5 соответствует одному устойчивому состояиию, ТД вернется в исходное состояние спустя время /

тд с момента постунления входного импульса.

тд 4 + 4 + 4 + 4,

где ,, - время возвращения ТД из точки С в точку А (см. фиг. 5).

Учитывая вид траектории движения рабочей точки и вид нагрузочной линии на фиг. 5, можно считать, что /в п.

Время возвращения в исходное состояние траизистора / с момеита поступления входного импульса будет

4. ,д + 24(1)

Соответственно для транзистора 2 и., 4д + 34 , где(2)

где 4 - время запаздывания коллекторного тока транзисторов относительно эмиттерного тока и связано с нроцессами диффузии носйтелей в базе транзистора.

Так как (э изменялся скачком дважды, то в выражение (1) входит 2 4.

меняются транзисторы с граничной частотой Мгц, а ТД имеет собственную емкость пф при ма, то

,2 нсек п 4,5 нсек /т, 4,7 нсек

Основная задержка выходных импульсов относительно входного связана со временем t-i . Если входом служит Вход II, то это время исключается, и тогда

тд 1,2 нсек t-t л; 1,5 нсек tf л; 1,7 нсек.

При необходимости можно получать желаемую длительность выходных импульсов, включая между эмиттерамн транзистора 1 и ТД 5 соответствующую индуктивность. Если используется только Вход II схемы, то базу транзистора 1 желательно шунтировать емкостью конденсатора 8.

Амплитудные характеристики схемы легко определяются на фиг. 3-6. На импульс, поступивший «а Вход I схема одновременно отреагирует отрицательным импульсом на коллекторе транзистора 1 и положительным - на коллекторе транзистора 2.

Таким образом, предлагаемая схема имеет два независимых входа и с 1мметричные выходы и молсет быть применена для построения следуюш,их типов логических элементов:

«ИЛИ, «И, «ИЛИ-ИЕ, «И-ИЕ, «ИЛИ-ИЛИ-НЕ, «И-И-ИЕ,

триггер и генератор тактовых импульсов.

Предмет изобретения

Логический элемент, содержащий р-п-р транзистор, включенный по схеме с общим эмиттером, эмиттер которого соединен с катодом туннельного диода, отличающийся тем, что, с целью расширения функциональных

возможностей и повышения быстродействия элемента, он содержит п-р-п транзистор, включенный по схеме с общей базой, эмитгер которого соединен с анодом туннельного диода.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДЛИТЕЛЬНОСТИ ИМПУЛЬСОВ ТОКА В НАПРЯЖЕНИЕ | 1971 |

|

SU301843A1 |

| РЕГИСТР СДВИГА | 1968 |

|

SU209069A1 |

| РАЗРЯДНЫЙ ФОРМИРОВАТЕЛЬ | 1972 |

|

SU327586A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ЗАПРЕТ» | 1972 |

|

SU423251A1 |

| СРАВНИВАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU291184A1 |

| Комплементарный логический элемент и-или/и-или-не | 1978 |

|

SU718929A1 |

| Триггер | 1978 |

|

SU739718A1 |

| АВТОМАТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ПОЭЛЕМЕНТНОГО КОНТРОЛЯ АККУМУЛЯТОРНОЙ БАТАРЕИ | 1971 |

|

SU319977A1 |

| Устройство для включения тиристора | 1971 |

|

SU472444A1 |

Вход

о-,

г+.

Даты

1971-01-01—Публикация