Изобретение относится к области вычислительной техники и может быть использовано при создании высокопроизводительных цифровых вычислительных машин в качестве разрядных формирователей записи и считывания оперативных запоминающих устройств (ОЗУ), выполненных на базе перспективных интегральных запоминающих элементов.

Известен разрядный формирователь, содержащий входное устройство с раздельными входами записи и считывания и выходное устройство, гальванически связанное с разрядной линией.

Однако наличие межкаскадного трансформатора связи в нем приводит к искажению фро.нтов импульса записи, ограничению быстродействия, увеличению суммарной задержки, ограничению стенени возможной интеграции запоминающих устройств на МОИ транзисторах. Кроме того, разрядный формирователь с межкаскадной трансформаторной связью не рассчитан на непосредственное соединение с комплексом логических схем управления по трактам записи и сч1 тывания.

В целях устранения вышеуказанных недостатков в предлагаемом формирователе входное устройство содержит выполненную на двух транзисторах, включенных по схеме с общим эмиттером и общей коллекторной нагрузкой, схему «ИЛИ, .входы которой соответственно соединены с раздельным: входами записи и считывания, а также с резнсторамн смещения, вторые выводы которых соединены с источником смещения, и двухкаскадный усилитель, выполненный на транзисторах, включенных но схеме с общим э.миттером и непосредственной связью между каскадами. Вход вышеуказанного двухкаскадного усилителя соединен со входом записи, нагрузочные резисторы схемы «ИЛИ и первого каскада усилителя подключены к плюсу источника питания, нагрузочный резнстор второго каскад, усилителя соединен с .плюсом другого источника питания, а выходное устроГктво выполнено на двух последовательно соединённых транзисторах с нагрузочны.ми резистора.ми в коллекторных цепях. Ирнчем база одного, из транзисторов соединена с выходом схемы «ИЛИ, а база другого - с выходом двухкаскадного усилнтеля.

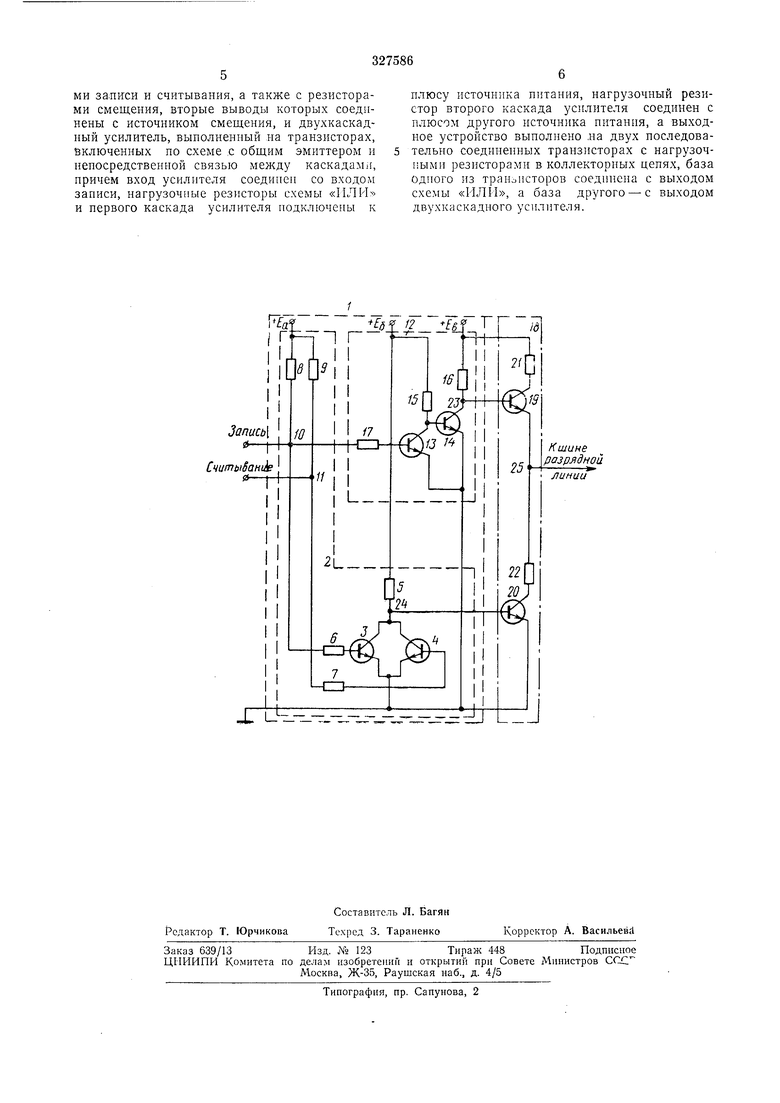

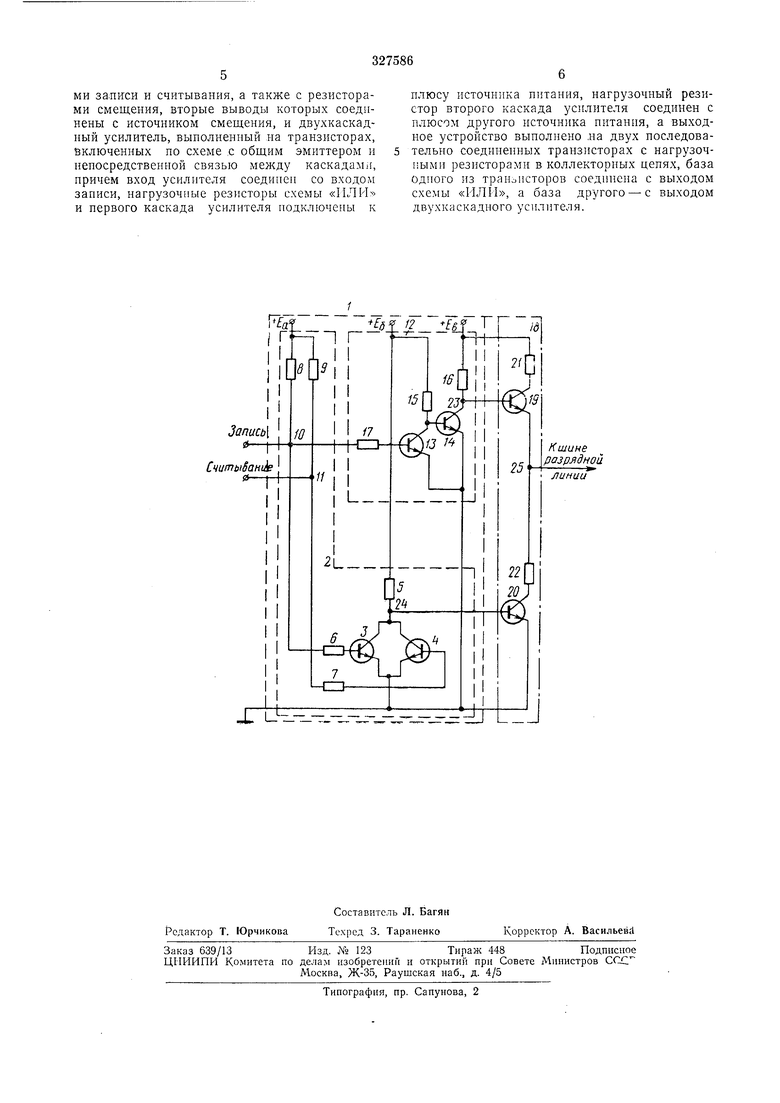

Иа чертеже нредставлеиа принципиальная электрическая схема предлагаемого форм 111ователя.

Формирователь содержит входное устройство /, содержащее логическую схему «ИЛИ 2, объединяющую входы «Запись п «Считывание н выполненную на двух транзисторах 3 л 4 п-р-/г-типа с общей коллекторной нагрузкой (резистор) 5 двумя базовыми резисторами 6 и 7 и двумя резисторами 8 9 смещения, общие точки 10 и 11 связи которых. соединены соответственно со входами «Запись и «Считывание ; и двухкаскадный усилитель 12 сигналов записи, выполненный по схеме с общим эмиттером на двух транзисторах 13 и 14м-р-/г-тииа с непосредственной связью между ними, с коллекторными резисторами 15 и 16 соответственно и базовым резистором 17 транзистора 13. Второй вывод резистора 17 соединен с общей точкой 10 связи. Вторые выводы резисторов 8 и 9 смещения подсоединены к илюсу источника смещения ЕЯ, являюн1,егося источником питания комплекса логических схем управления разрядным формирователем. Резисторы 5 и 15 коллекторных ценей транзнсторов 3, 4 и 13 соответственно иодсоедннены к нлюсу источника питания разрядного формирователя Ег, с более низким потенциалом, что уменьп1ает энергонотребление схемы. Резистор 16 коллекторной цени траизистора 14 подсоединен к нлюсу источника пита.ния ЕК с более высоким потенциало.м.

Выходное устройство 18 выполнено па двух последовательно соединенных транзисторах /9 и 20 п-р-л-тнна с коллекторными резисторами 21 и 22. Базовые выводы транзисторов 19 н 20 соединены соответственно с общей точкой 23 связи резистора 16 и коллектора транзистора 14 двухкаскадного усилителя 12 сигналов заниси и с общей точкой 24 связи резистора 5 и коллекторов транзисторов 3 и 4 логической схемы «ИЛИ 2. Общая точка 25 связи эмиттера траизистора 19 и резистора 22 коллекторной цеии транзистора 20 подсоедииена к шине разрядной линии.

В статическом состоянии, т. е. при отсутствии сигналов заииси и считываиия, когда потенциалы точек 10 и 11, определяемые исходным состоянием выходных каскадов комнлекса логических схем управления по трактам записи и считываиия, низкие, траизисторы 3, 4, 13 и 19 иаходятся в режиме отсечки, а траизисторы 14 и 20-в режиме насыщения. На niHiiy разрядной линии (точка 25) постуиает потенциал, нрактически равный -,„ разрядная линия соединяется с землей, что нриводит к заряду емкости, существующей между стоком и нодложкой МОП траизнстора триггера запоминающего устройства, нодключенного к данлой разрядной линнн.

При поступлении имнульса занлсн на вход «Занись входиого устройстг а / транзисторы 3, 13 н 19 нереходят в режим пасыии пия, а транзисторы 14 и 20 - в режим отсечки. Ма разрядную линию (точка 25 иостуиает сигнал ЕК, емкость сток-иодлол ка разряжается по цени: нодложка МОП транзистора заномииающего устройства, источник Ер,, резистор 21, коллектор-эмиттер транзистора 19 (точка 25), сток МОП транзнстора. По окончании входной команды заниси в схеме восстанавливается исходное состояние транзисторов: транзисторы 3, 4, 13 н 19 возврап1аются в режим отсечки, а транзисторы 14, 20 -

в режим насыщения, так что на разрядной лкиии появляется цотенциал -ЕВПри считывании кода «1 на вход «Считывание входного устройства / поступает

имнульс считывания (потенциал точки 11 ирактически становится равным а), транзистор 4 нереходит в режим асыщения, транзнстор 20 выходного устройства - в режи.м отсечки. Состояние оетальных транзисторов

разрядного формирователя остается исходным, т. е. траизисторы 3, 13 и 19 иаходятся в режиме отсечки, транзистор 14 ъ режи.ме насыщения. Емкость сток - нодложка разряжается теперь через разрядную линию: адресные МОП транзисторы разрядной линии, открытый МОП транзистор триггера заноминаюн1его устройства, нринадлежащего к выбранному слову памяти. Если нлечо триггера заиоминающего устройства занерто, никакого тока практически не возннкает - считывается код «О. Если это нлечо открыто, то через разрядную лннию начинает протекать ток - считывается код «1. Такнм образом, предлагаемый разрядный

формнрователь позволяет осуществнть непосредственное управлеппе от комплекса логических схем унравлення по трактам записи и считывапия, обеспечивает запись информационного кода без разделительного траисформатора между входным устройством и выходным, гальванически связанным с разрядной линней. Отсутствие трансформатора существепио улучшает форму имнульса записи, )меньшает суммарную задержку до величины

11римерно 50 нсек, включая разрядную лииию, ири амплитуде разрядного тока порядка 160 ма, обеснечивающей быстрое переключение соответствующего триггера запоминающего устройства, выиолнеииого иа МОП траизисторах.

Построение разрядиого формирователя на транзисторах в режиме нереключения с непосредственной связью между каскадами обеспечивает высокую стабильность характеристик, экономичность унравлення, достаточно высокую стенень интеграции, что позволяет существенно уменьшнть габариты и вес устройства.

Предмет изобретения

Разрядиый формирователь, содержащий входное устройство с раздельными входами записи и считывания и выходное устройство,

гальваиически связаииое с разрядной линией, отличающийся тем, что, с целью улучшения фронтов имиульса записи, ловышения быстродействия схемы, обеспечения неиосредствеииой стыковки с комилексом логических схем

уиравления и повышения степени интеграции, входное устройство содержит выполненную на двух транзисторах, включенных по схеме с общим эмиттером и общей коллекторной нагрузкой, схему «ИЛИ, входы которой соотми залнси и считывания, а также с резисторами смещения, вторые выводы которых соединены с источником смещения, и двухкаскадный усилитель, выполненный на транзисторах, йключенных по схеме ,с общим эмиттером и непосредственной связью между каскадами, причем вход усилителя соединен со входом записи, нагрузочные резисторы схемы «ПЛИ и первого каскада усилителя подключены к

илюсу источника питания, нагрузочный резистор второго каскада усилителя соединен с плюсом другого источника питання, а выходное устройство выполнено ,на двух последовательно соединенных транзисторах с нагрузочр.ыми резисторами в коллекторных цепях, база одного из транзисторов соединена с выходом схемы «ИЛИ, а база другого - с выходом двухкаскадного усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАЗРЯДНЫЙ ФОРМИРОВАТЕЛЬ | 1973 |

|

SU370649A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-СЧИТЫВАНИЯ | 1972 |

|

SU345517A1 |

| ФОРМИРОВАТЕЛЬ ТОКА ВЫБОРКИ | 1973 |

|

SU377869A1 |

| Полупроводниковое реле постоянного тока | 1976 |

|

SU706932A2 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| УСТРОЙСТВО для СРАВНЕНИЯ | 1970 |

|

SU269223A1 |

| Формирователь импульсов | 1974 |

|

SU657601A1 |

| Устройство для формирования разрядных токов записи | 1975 |

|

SU546016A1 |

| ИМПУЛЬСНЫЙ ФОРМИРОВАТЕЛЬ ТОКА | 1970 |

|

SU269199A1 |

....J...IjJ

XL

Ев Г Ц

I Н 1 I

Кшине разрядной

Даты

1972-01-01—Публикация