Известные запоминающие устройства на трансфлюксорах, управляемые неограниченными токами, содержат числовые шины записи «О, числовые шины записи «1, выходы которых для каждой матрицы объединены в общую точку, разрядные шины запрета «1, разрядные шины запрета «О и кодовый преобразователь.

Отличием предлагаемого устройства является то, что общая точка всех числовых шин записи «1 матрицы через кодовый распределитель подключена к разрядной шине запрета «О или разрядной шине запрета «1, причем выходы обеих шин запрета каждого разряда объединены в общую точку, подключенную через кодовый распределитель к шине запреla «О или тине запрета «1 следующего разряда.

Это повышает наделсность устройства, упрощает его н снижает необходимую амплитуду импульса записи.

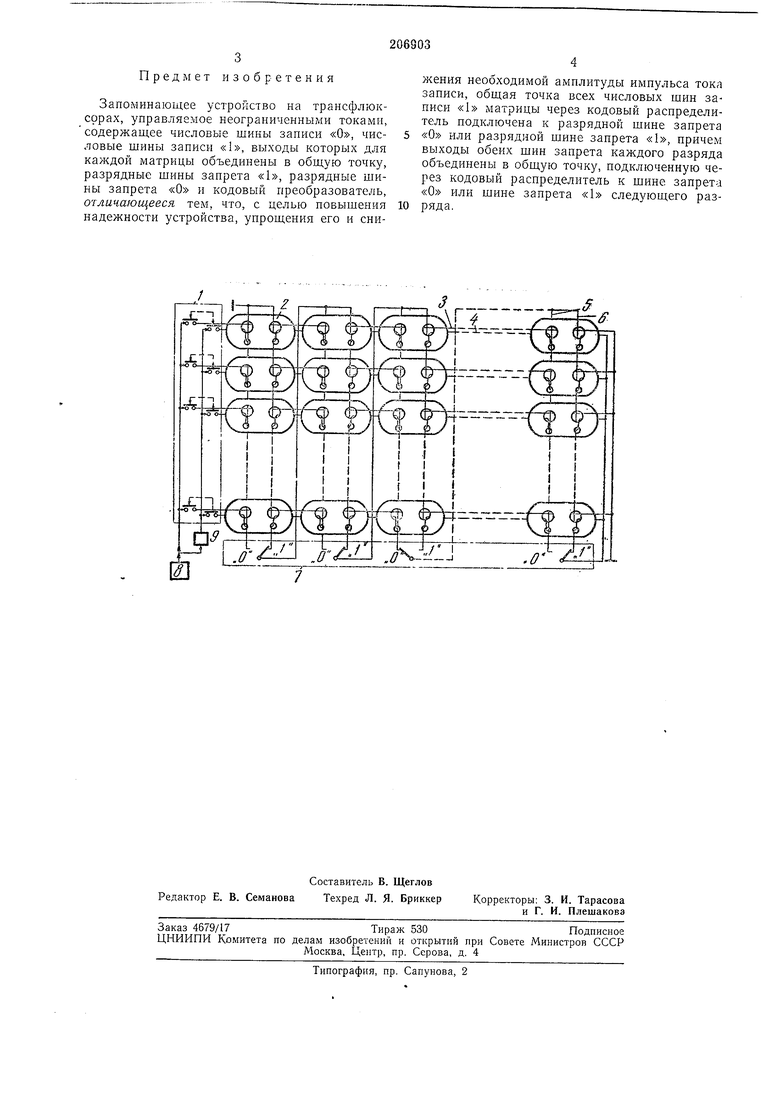

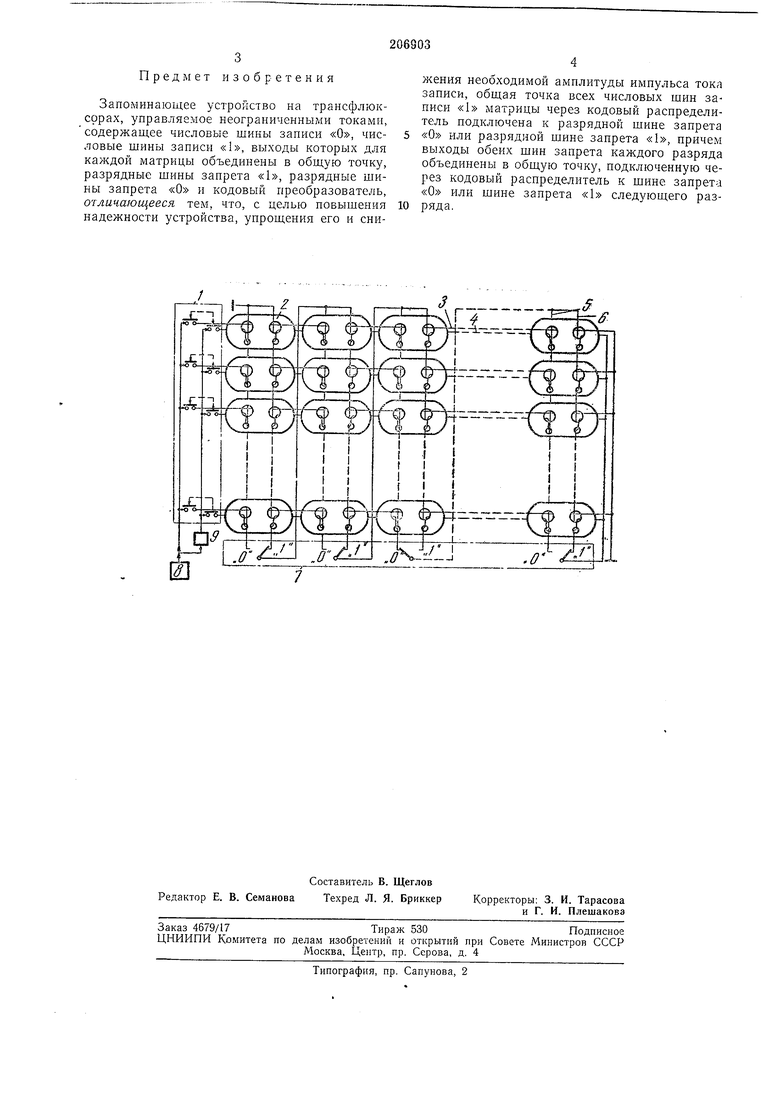

На чертеже изображена принципиальная схема предложенного устройства.

Устройство содержит распредели ель / чисел, собственно запоминающее устройство 2 на трансфлюксорах, числовые шины 3 записи «О, числовые шины 4 записи «1, разрядные шины 5 запрета «1, разрядные шины 6 запрета «О, кодовый распределитель 7, формирователь записи 8 и схему задержки 9.

Информация в рассматриваемом устройстве представляется активным сигналом «Q.

1. Логическая 10. 2. Логический «О - 01.

С помощью распределителя 1 чисел выход формирователя записи 8 подключается непосредственно к шине 3 записи «О и через схему задержки 9 к шине 4 записи «1 выбранной числовой линейки. Запись информаци осуществляется в два такта. В первом такте импульс тока проходит по соответствующей числовой щине 3 записи «О, осуществляя стирание информации в данной числовой линейке; во втором такте им1пульс тока записи проходит по соответствующей числовой шине 4 записи «1 и последовательно через разрядные шины 5 запрета «1 или разрядные шины 6 запрета «О матрицы, подключенные кодовым распределителем согласно заданному коду.

Достоинством описываемого устройства является то, что в нем обеспечивается строгое соответствие амплитуды тока в шинах записи

«1 и запрета и совпадение этих сигналов во времени.

Кроме того, в такой схеме необходима а.мнлитуда импульса тока записи значительно ниже, чем у схем с параллельным запреПредмет изобретения

Запоминающее устройство на трансфлюксорах, управляемое неограниченными токами, содержащее числовые шины записи «О, числовые щины записи «I, выходы которых для каждой матрицы объединены в общую точку, разрядные щины запрета «1, разрядные щины запрета «О и кодовый преобразователь, отличающееся тем, что, с целью повыщения надежности устройства, упрощения его и снижения необходимой амплитуды импульса тока записи, общая точка всех числовых щин записи «1 матрицы через кодовый распределитель подключена к разрядной щине запрета «О или разрядной щине запрета «I, причем выходы обеих щин запрета каждого разряда объединены в общую точку, подключенную через кодовый распределитель к щине запрета «О или щине запрета «1 следующего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU300890A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236863A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU254205A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236862A1 |

| Запоминающее устройство | 1973 |

|

SU446108A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335719A1 |

| КРИОГЕННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU265188A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU216795A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

Даты

1968-01-01—Публикация