Изобретение относится к вычислительной технике и может быть использовано на предприятиях, занимающихся разработкой, испытаниями и отбраковкой интегральных схем.

Известен анализатор коротких замыканий и обрывов, предназначенный для проверки кремниевых интегральных схем типа ТС-1 на отсутствие кратковременных коротких замыканий и обрывов при испытании на виброустойчивость.

Испытание интегральных схем на отсутствие кратковременных коротких замыканий и кратковременных обрывов производится в р жимах, указанных в технических условиях на испытуемые интегральные схемы.

Недостатком такого устройства обнаружения коротких замыканий и обрывов является то, что фиксирование коротких замыканий и обрывов происходит нестабильными по амплитуде перепадами напряжений, возникающими на контактах испытуемой интегральной схемы. Возможен случай, когда при иоявлении короткого замыкания или обрыва амплитуда возникаюн;его перепада будет очень мала, вс.тедствие чего может быть нечетное срабатывание электронного реле и короткое замыкание или обрыв могут быть не зафиксированы. Если испытуемая интегральная схема заведомо имеет короткое замыкание или

обрыв, то и в этом случае короткое замыкание или обрыв не будет зафиксирован.

Следующим недостатком являются невозможность проверки на данном стенде интегральных схем милливаттной и микроваттной мощности, а также обрывов и коротких замыканий микросекундной длительности вследствие инерционности реле. Целью предлагаемого изобретения является создание анализатора коротки.х замыканий и обрывов для испытаний расщиренного состава интегральных схем, фиксации обрывов и замыканий, существующих в течение коротких промежутков времени (порядка десятка

микросекунд), повыщения надежности прибора и удобства эксплуатации.

Указанная цель достигается тем, что входные контакты испытуемой интегральной схемы соединены через схемы «НЕ с выходами

импульсов положительной полярности формирователя последовательностей импульсов и через схемы «ИЕ с первыми входами схем «И первого элемента «И-ИЛИ-ИЕ, вторые входы которых соединены с выходами

импульсов отрицательной полярности формирователя последовательностей импульсов. Выход первого элемента «И-ИЛИ-ИЕ через инвертор соединен со входом третьей схемы «И второго элемента «И-ИЛИ-ИЕ.

рез схему «ИЛИ соединены с первым входом первой схемы «И и через ппвертор - с первым входом второй схемы «И второго элемента «И-ИЛИ-ИЕ, причем вторые входы первой и второй схем «И этого же элемента «И-ИЛИ-НЕ соединены соответственно с выходами импульсов опроса формирователя последовательностей импульсов, выход второго элемента «И-ИЛИ-НЕ соединен со входом установки нуля триггера индикации. При этом на входы испытуемой схемы подаются импульсы отрицательной полярности, разнесенные во времени, и анализируется прохождепие этих импульсов в испытуемой интегральной схеме. В случае короткого замыкания или обрыва в контактных соединениях испытуемой интегральной схемы на выходе анализатора появляется импульс напряжения, который поступает на триггер индикации. Триггер сработает и загорится лампочка индикации.

Испытания, могут подвергаться интегральные схемы, сопрягаемые по уровням логических «О и «1 с интегральными схемами тина «Логика и реализуюни1е логические функции «И, «И-НЕ, «И-ИЛИ-НЕ.

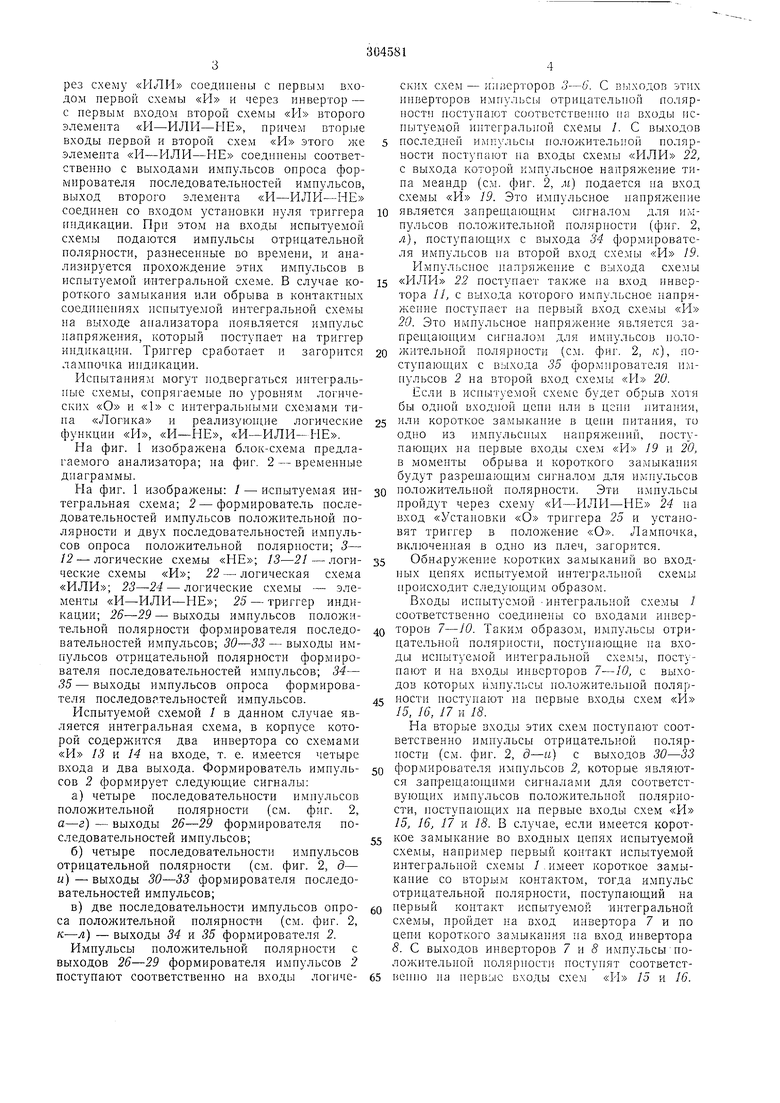

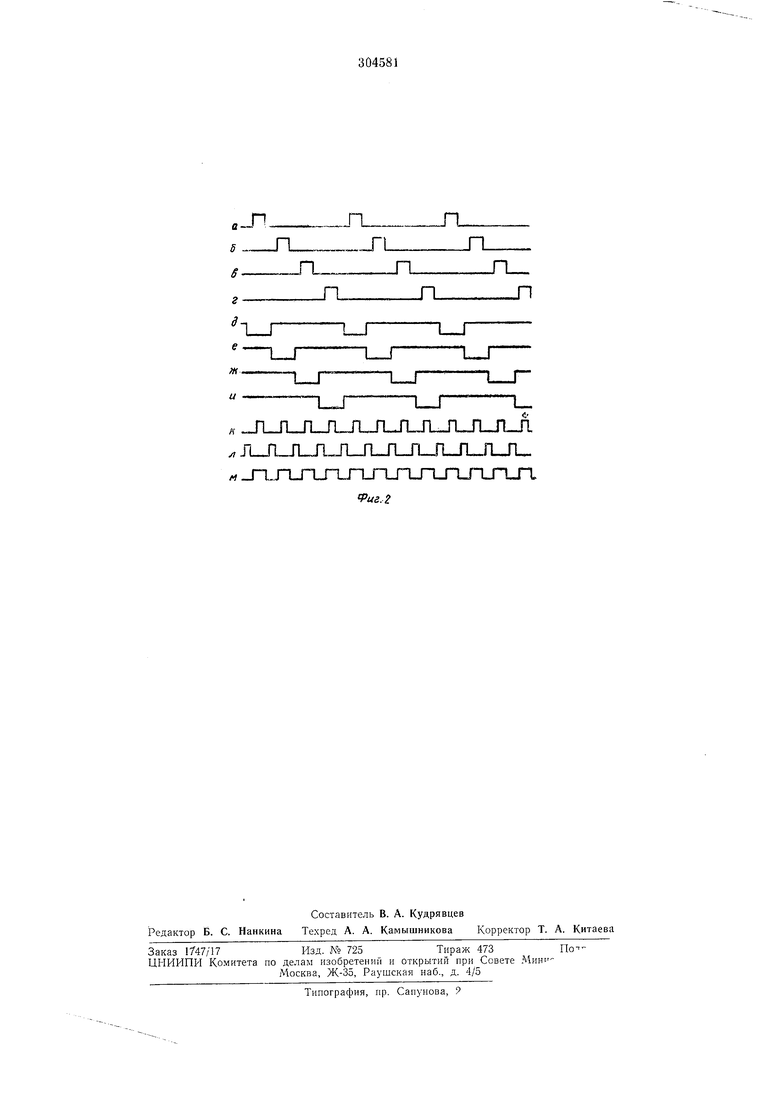

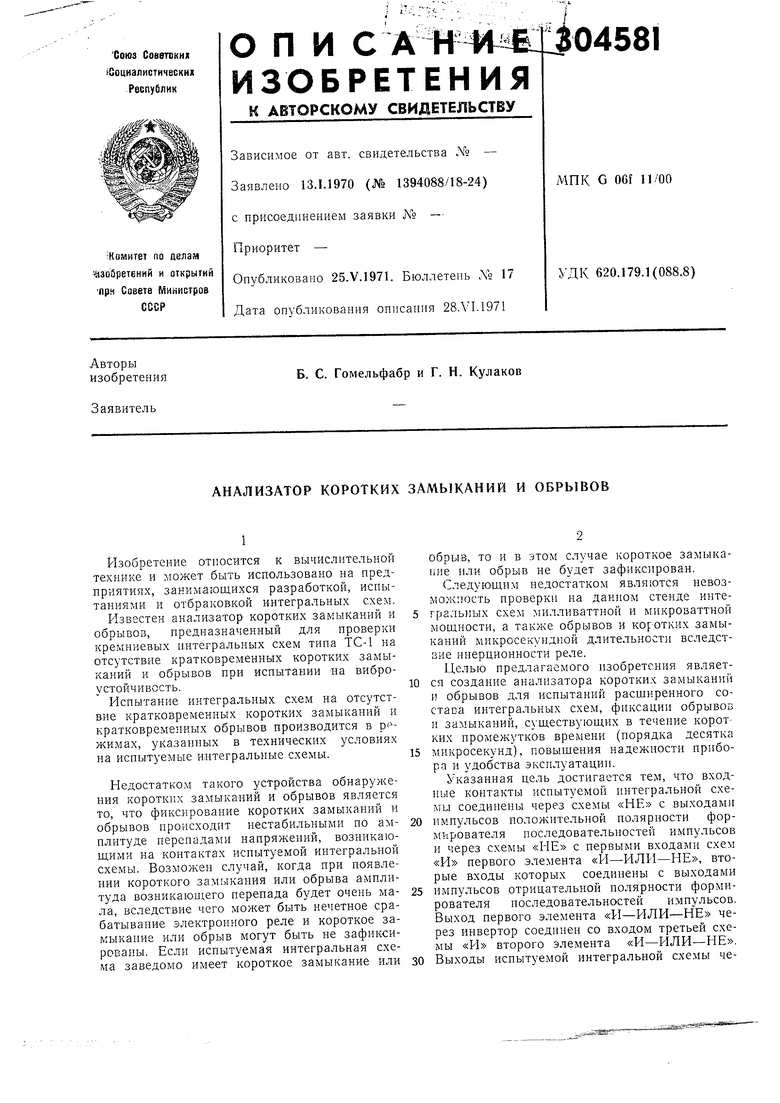

На фиг. I изображена блок-схема предлагаемого анализатора; на фиг. 2 - временные диаграммы.

На фиг. 1 изображены: / - испытуемая интегральная схема; 2 - формирователь последовательностей импульсов пололштельной полярности и двух последовательностей имнульсов опроса положительной полярности; 3- 12 - логические схемы 13-21-логические схемы 22 - логическая схема 23-24 - логические схемы - элементы «И-ИЛИ-НЕ ; 25 - триггер индикации; 26-29 - выходы импульсов положительной полярности формирователя последовательностей импульсов; 30-33 - выходы импульсов отрицательной полярности формирователя последовательностей импульсов; 34- 35 - выходы импульсов опроса формирователя последовательностей импульсов.

Испытуемой схемой / в данном случае является интегральная схема, в корпусе которой содержится два инвертора со схемами «И 13 и 14 на входе, т. е. имеется четыре входа и два выхода. Формирователь импульсов 2 формирует следующие сигналы:

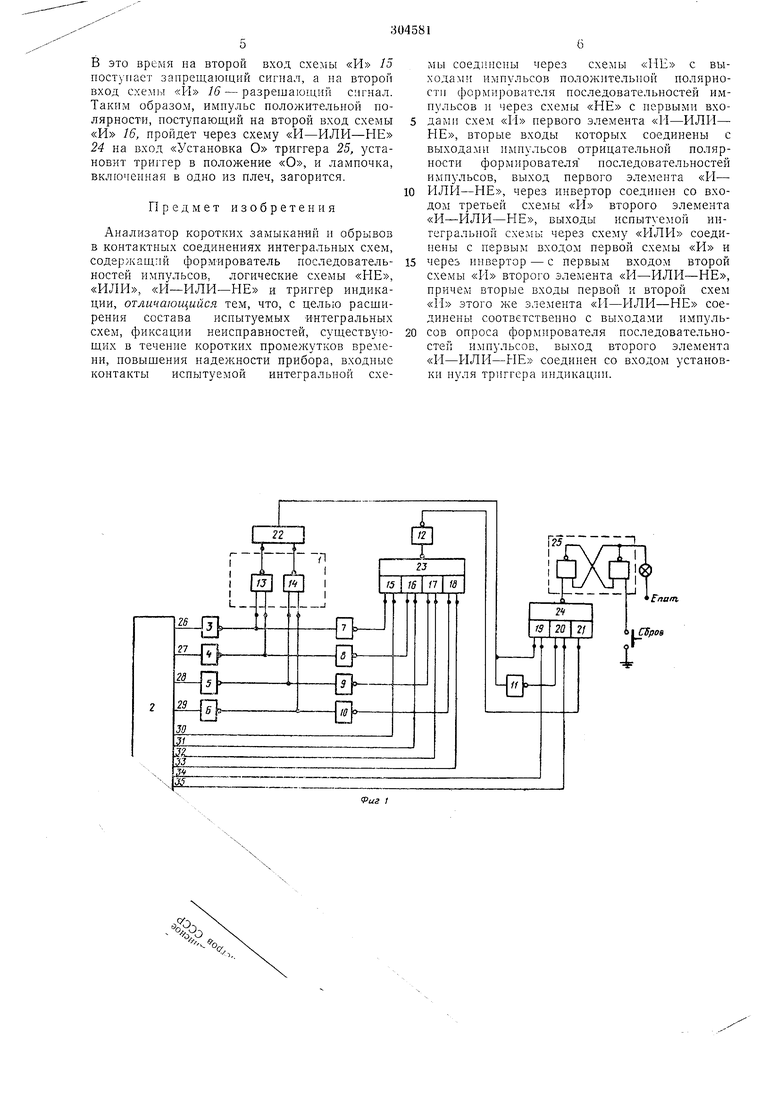

а)четыре последовательности импульсов положительной полярности (см. фиг. 2, а-г) - выходы 26-29 формирователя последовательпостей импульсов;

б)четыре последовательности импульсов отрицательной полярности (см. фиг. 2, д- и) - выходы 30-33 формирователя последовательностей импульсов;

в)две последовательности импульсов опроса положительной полярпости (см. фиг. 2, к--л) - выходы 34 и 35 формирователя 2.

ских схем - инверторов 3-6. С влходов этих инверторов импульсы отрицательной полярности поступают соответственпо на входы испытуемой интегральной схемы 1. С выходов 5 последней импульсы но.чожительпой полярности поступают на входы схемы «ИЛИ 22, с выхода которой 1-1: шульсное напряжение тина меандр (c:vi. фиг. 2, м) нодается па вход схемы «И 19. Это импульсное напряжение

Q является запреп1аюш,им сигналом для нл:пульсов положительной полярности (фиг. 2, л), поступающих с выхода 34 формирователя импульсов на второй вход схемы «И 19. Импульсное напряжение с выхода схемы

15 «ИЛИ 22 поступает также па вход инвертора //, с выхода которого импульсное iianpHженне поступает на первый вход схемы «И 20. Это импульсное напряжение является запрещающим сигналом для импульсов положительной полярности (см. фиг. 2, к), поступающих с выхода 35 формирователя импульсов 2 на второй вход схе.мы «И 20.

Если в испытуемой схеме будет обрыв хотя бы одной входной ценн или в цепи ниталия,

5 или короткое замыкание в цени питания, то одно из импульсных напряжений, поступаюпхих на первые входы схем «И 19 и 20, в моменты обрыва и короткого замыкапия будут разрещающим сигналом для имну.тьсов

0 полол :ительпой полярпости. Эти импульсы пройдут через схему «И-ИЛИ-НЕ 24 на вход «Установки «О триггера 25 и установят триггер в положение «О. Лампочка, включенная в одно из плеч, загорится.

5 Обнаружение коротких замыканий во входных цепях испытуемой интегральной схемы происходит следующим образом.

Входы испытуемой Интегральной схемы / соответственно соединены со входами инверторов 7-10. Таки.м образом, импульсы отрицательной полярности, поступающие на входы испытуемой интегральной схемы, поступают и на входы инверторов 7-10, с выходов которых импульсы положительной полярности поступают на первг ш входы схем «И 15, 16, 17 н18.

На вторые входы этих схем поступают соответственно импульсы отрицательной нолярпости (см. фиг. 2, д-и) с выходов 30-33

0 формирователя импульсов 2, которые являются запрещающими сигналами для соответствующих импульсов положительной полярности, поступающих на первые входы схем «И 15, 16, 17 и 18. В случае, если имеется короткое замыкание во входных цепях испытуемой схемы, например первый контакт испытуемой интегральной схемы /.имеет короткое замыкание со вторым контактом, тогда импульс отрицательной полярности, поступающий на

o первый контакт испытуемой интегральной схемы, пройдет на вход инвертора 7 и по цени короткого замыкания на вход инвертора 8. С выходов инверторов 7 и 8 импульсы ноложителыюй полярности поступят соответственно па первые входы схем «И 15 и 16.

В это время на второй вход схемы «И /5 поступает запрещающий сигнал, а на второй вход схем1я «И 16 - разрешающий сигнал. Таким образом, импульс положительной полярности, поступающий на второй вход схемы «И 16, пройдет через схему «И-ИЛИ-НЕ 24 на вход «Установка О триггера 25, установит триггер в положение «О, и лампочка, включенная в одно из плеч, загорится.

Предмет изобретения

Анализатор коротких замыканий и обрывов в контактных соединениях интегральных схем, содержащий формирователь последовательностей импульсов, логические схемы «НЕ, «ИЛИ, «И-ИЛИ-НЕ и триггер индикации, отличающийся, тем, что, с целью расщирения состава испытуемых интегральных схем, фиксации неисправностей, существующих в течение коротких промежутков времени, повьш1ения надежности прибора, входные контакты испытуемой интегральной схемы соединены через схемы «НЕ с выходами импульсов положительной полярности формирователя последовательностей имиульсов и через схемы «НЕ с первыми входами схем «И первого элемента «И-ИЛИ- НЕ, вторые входы которых соединены с выходами импульсов отрицательной полярности формирователя последовательностей имиульсов, выход первого элемента «И-

ИЛИ-НЕ, через инвертор соединен со входом третьей схемы «И второго элемента «И-ИЛИ-НЕ, выходы испытуемой интегральной схемы через схему «ИЛИ соединены с первым входом первой схемы «И и

через инвертор - с первым входом второй схемы «И второго элемента «И-ИЛИ-НЕ, причем вторые входы первой и второй схем «И этого элемента «И-ИЛИ-НЕ соединены соответственно с выходами импульсов опроса формирователя последовательностей импульсов, выход второго элемента «И-ИЛИ-НЕ соединен со входом установки иуля Tpiirrepa индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля контантирования выводов интегральной схемы | 1980 |

|

SU890280A1 |

| Устройство контроля надежности омических контактов полупроводниковых диодов | 1978 |

|

SU673940A1 |

| Устройство для фиксации обрывов и коротких замыканий электродов транзисторов | 1978 |

|

SU744386A1 |

| Устройство для испытаний обмоток на обрыв и наличие короткозамкнутых витков | 1987 |

|

SU1576876A1 |

| УСТРОЙСТВО ДЛЯ НАКАЛА КАЛИЛЬНОЙ СВЕЧИ | 2017 |

|

RU2660979C1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для индикации | 1983 |

|

SU1124376A1 |

| Устройство для определения междуфазных замыканий и замыканий на землю в сетях с изолированной нейтралью напряжением 6-10 кВ | 2022 |

|

RU2788035C1 |

| Устройство для контроля состояния объектов | 1986 |

|

SU1368902A1 |

| Устройство для контроля электрического монтажа | 1990 |

|

SU1794258A3 |

vpzun :

я ™rLJT-JlJl AJLJT Jl JT rLJT R , Jl l-JLJl-JLJLJlJlJlJlJT / jn.nJTJnjnjnj jnjTJ-Lnj4

Риг. 2

Даты

1971-01-01—Публикация