Изобретение относится к аналого-цифровым преобразователям и может быть использовано в различных устройствах автоматики и вычислительной техники.

Известны преобразователи аналоговых величин в цифровой код, состоящие из генератора тактовых импульсов, регистра тактов, логических схем «И, регистра результата, управляющего линейным декодирующим преобразователем, связанным со сравнивающим устройством, к одному из входов которого подключают источник эталонного напряжения, соответствующего в каждый данный момент времени весу разряда преобразуемой величины.

Известные преобразователи аналоговых величин в цифровой код имеют тот недостаток, что под воздействием помех возможен сбой любого из триггеров регистра результата или регистра тактов, что неизбежно приводит к искажению результата преобразования.

Целью изобретения является повыщение достоверности измерений в условиях воздействия помех.

Это достигается тем, что в аналогоцифровом преобразователе единичные входы триггеров регистра результата соединены с нулевыми входами триггеров регистра тактов, а нулевые - с единичными соотретственно, выходы триггеров регистров результата и тактов, кроме последнего, подключены ко входам ячеек деи1ифратора соответствия, а выходы последних триггеров - ко входу дешифратора несоответствия, выход которого через схему «И подключен к первому входу генератора тактовых импульсов, выходы дешифратора соответствия через схемы «ИЛИ подключены ко входам вентилей-формирователей; первый выход генератора тактовых импульсов через вентиль подключен к одному входу сравнивающего устройства и через схемы «И к единичным входам триггеров регистра результата и к нулевым входам триггеров регистра тактов; второй выход генератора через вентиль и схемы «И подключен к нулевым входам триггеров регистра результата и к единичным входам триггеров регистра тактов, другие входы этих схем «И подключены к выходу сравнивающего устройства; третий Выход генератора тактовых импульсов соединен со входом дещифратора несоответствия и со входами схем «И, другие входы которых подключены к выходам дещифраторов соответствия, выход каждой из

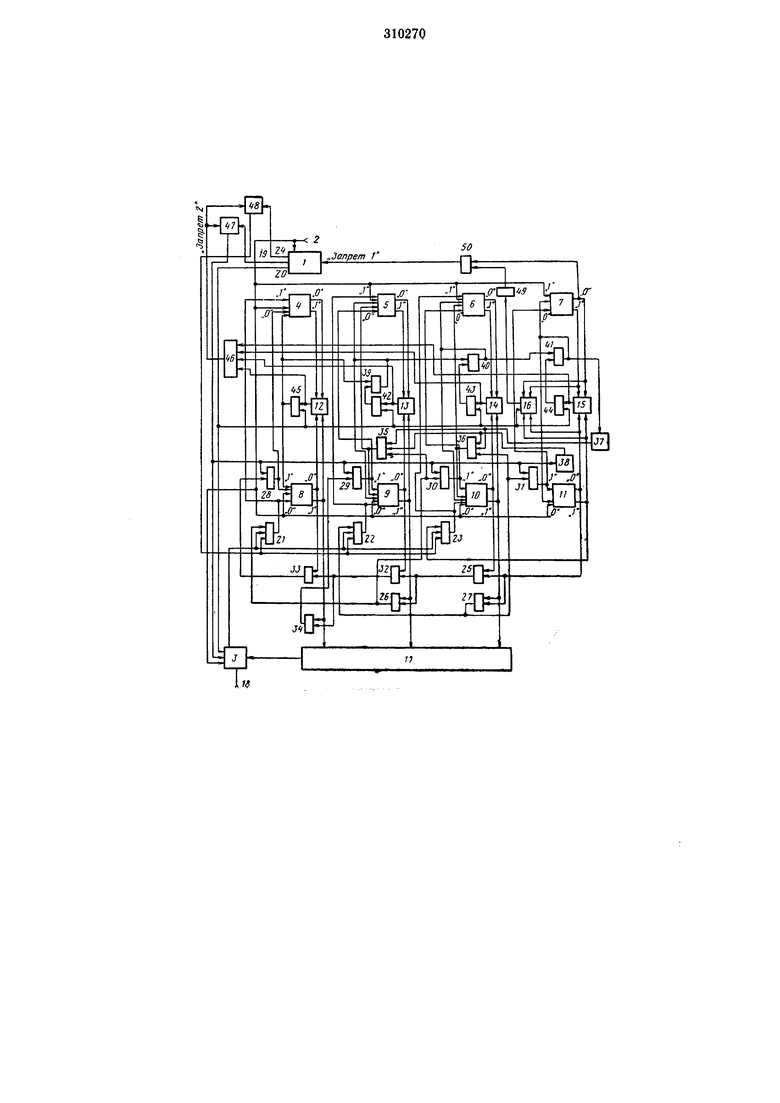

этих схем «И, кроме первой, подключен к одному из входов соответствующей схемы «ИЛИ, выходы которых соединены с нулевыми входами соответствующих триггеров регистра тактов и результата, схемы «ИЛИ выход последней из них через линию задержки и схему «И подключен к нулевым входам триггеров регистра и результата. На чертеже представлена структурная схема аналого-цифрового преобразователя. Она содержит генератор 1 тактовых импульсов, клемму 2 «Пуск, сравнивающее устройство 3, триггеры 4-7 регистра тактов, триггеры 8-// регистра результата, дешифраторы 12-15 соответствия, дешифратор 16 несоответствия, декодирующий преобразователь 17, клемму 18 входного напряжения, шины 19 и 20 генератора, схемы «И 21--23, выходную шину 24 генератора, схемы «И 25-36, линии задержки 37 и 38, схемы «ИЛИ 39, 40, 41, схемы «И 42-45 дешифратора, общую схему «ИЛИ 46, вентилиформирователи 47 и 48, выходные схемы «И 49 и 50. Работа преобразователя состоит из двух основных режимов: режим отсутствия сбоев в процессе преобразования элементов памяти (триггеров) под воздействием помех и режим наличия сбоев триггеров под воздействием помех.. ,i i В первом режиме ,Ър 1Сигнале «Пуск схему устанавливают в исходное состояние, при котором триггер 8 старшего разряда регистра результата, устанавливают в состояние «1, а триггеры 9, 10, 11 последующих разрядов этого регистра, а также триггер сравнивающего устройства 3 и триггер 4 старшего разряда регистра тактов - в состояние «О. Триггеры 5, 6, 7 последующих разрядов регистра тактов устанавливают в состояние «1. Причем триггеры обоих регистров имеют нулевые («О) и единичные («1) входь и единичные («1) и нулевые («О) выходы. С выходов «О триггеров 10 и // подают разрешающий потенциал на один из входов схемы «И 32, на второй вход которой подают потенциал с выхода «О триггера 9. С выхода схемы «И 32 подают потенциал на один из входов логической схемы «И 34, на второй вход которой подают потенциал с выхода «1 триггера 8, благодаря, чему с выхода схемы «И 34 разрешающий потенциал аортупает на один из входов, схемы «И 29. В то же время в генераторе имлульсов 1, на которьщ также подают сигнал «Пуск., ф,ормир.уют сдвинутые во времени импульсы первого такта на линиях первой, второй и третьей фазы - шины 19, 24 и 20 соответственно. Импульсом первой фазы по шине 19 через вентиль-формирователь 47 (поскольку отсутствует потенциал «Запрет 2) опрашивают схемы «И 28-3,1, образующие совместно со схемами «И 21-23 логическую схему фррмирования прямого и обратного кодов. Так как подготовлена к работе только схема 29, то Триггер 9 устанавливают в состояние «1 импульсом с выхода схемы 29, а на выходе декодирующего преобразователя 17 формируют компенсационное напряжение U, соответству{ощее весу следующего (2-го) разряда, которое суммируется с весом 1-го разряда, присутствующим на выходе преобразователя 17 в исходном состоянии схемы. При этом со входа (а следовательно, и выхода) схемы «И 32 снимают, а на вход схемы «И 26 подают разрешающий потенциал. В результате этого на выходе схемы «И 26 формируется разрещающий потенциал, который поступает на соответствующие входы схем «И 21 и 30, подготавливая тем самым последние к работе. По шине 19 производят также опрос состояния, в котором находилось сравнивающее устройство 3 в момент, пррдществующий появлению импульса на щине 19. При этом на выходе сравнивающего устройства 3, к клемме 18 которого подключают входное преобразуемое напряжение t/вх. формируют разрешающий потенциал, если выполняется условие , и потенциал запрета - в противном случае. Импульсом второй фазы через вентиль-формирователь 48 (поскольку отсутствует потенциал «Запрет .2) по шине 24 производят опрос схем «И 21-23. Если на входе схемы 21 присутствует разрешающий потенциал с выхода сравнивающего устройства 3, то на выходе схемы 21 в этом случае формируется импульс, который устанавливает триггер 8 в «О, а триггер 4 - в «1 состояние. Импульсом третьей фазы по шине 20 производят опрос схем 42-45 и сбрасывают в исходное состояние «О триггер сравнивающего устройства 3. Импульс на выходе дешифратора несоответствия 16 подают на вход схемы «И 50, на втором входе которой присутствует запрещающий потенциал в том случае, если триггер 7 находится В состоянии «1. На втором такте работа схемы происходит аналогично изложенному выще, с тем отличием, что в результате установки в состояние «1 триггера 10 импульсом первой фазы по щине 19 снимают разрешающий потендиал с выхода схемы «И 26, а следовательно, и с соответствующих входов схем «И 21, 30 и форм.ируют разрещающий потенциал на выходе схемы «И 27; а следовательно, и на соответствующих входах схем «И 22, ЗА Импульс второй фазы пропускают на выход схемы «И, 22, если f/Bx- a. и устанавливают триггер 9 в «О, а триггер 5 -в «1 состояние. Импульс не проходит, на выход схемы 22 в противном случае ()Импульсом третьей фазы по щине 20 производят опрос состояния схем «И , аналогично изложенному В)Ь1ше и сб.ра,сывают в исходное состояние триггер сравнивающего устройства 3. На третьем такте работа cxeMiji происходит следующим образом. Импульс Нарвой фазы по щине 19 подают на соответствующий вход схемы «И 31 и устанавливают триггер // В «1, а триггер 7 - гера 11 подают разрешающий потенциал на сйответствующий вход схемы «И 23, а с выхода «О триггера 7 подают разрешающий потенциал на соответствующий вход схемы «И 50. Импульс второй фазы проходит на выход схемы «И 23, если , устанавливая триггер 10 в состояние «О, а триггер 7 - в состояние «1, и не проходит схему «И 23 в противном случае {t/вх э)Импульсом третьей фазы по шине 20 произВоДят опрос схем 42-45 и сбрасывают в исходное состояние триггер сравнивающего устройства 3. При этом (в случае отсутствия помех) импульс третьей фазы проходит дешифратор несоответствия 16, схему «И 49 и поCTynaet на соответствующий вход схемы 50, с выхода которой формируется импульс запрета, прекращающий работу трехфазного генератора импульсов 1. Во втором режиме (наличие сбоев триггеров в процёссе преобразования под действием помех) paiccMOTpHM следующие случаи: а)сбой триггеров происходит после поступления импульса «Пуск или после импульса третьей фазы генератора /; б)сбой триггеров происходит после поступления импульса первой фазы генератора. В первом случае при сбое триггеров после первого такта на втором такте схема работает следующим образом. Поскольку в схеме имеются триггеры (например, 6, 10), которые находятся в одинаковом состоянии, то на выходах соответствующих дешифраторов соответствия (в данном случае 14) появляется потенциал «Запрет 2, который через схему «ИЛИ 46 поступает на вентили-формирователи 47 и 48, запрещая тем самым поступление импульсов первой и второй фазы генератора /. По этой причине импульсы первой и второй фазы не произведут в -схеме никаких изменений. Импульсом третьей фазы по шине 20 опрашивают схемы «И 42-45. На выходе схемы 43 ПОЯВИТСЯ импульс, так как на ее вход подан разрешающий потенциал с выхода дешифратора 14. Импульс третьей фазы через схемы 40 и 41 установит триггеры 6 и 7 в единичное состояние, триггеры 10, 11 - в нулевое. С выхода схемы 41 посылают импульс также на линию задержки 37, которая задерживает импульс на время переходных процессов в триггерах обоих регистров. С выхода линии 37 импульс подают на схемы «И 35, 36. Так как на вход линии задержки 38, в которой импульс задерживается на время прохождения импульсов второй и третьей фазы (шины 24, 20) генератора, не был подан импульс -первой фазы (шина 19} генератора, то импульс с выхода линии 37 не проходит на выход схем 35, 36. Если среди триггеров регистра результата имеется хотя бы один триггер, находящийся в состоянии «1, то посредством схем «И 25, 26, 27, 32, 34 выделяют первый справа тригго примера таким явv яeтcя триггер 5, так как на первом такте импульсом первой фазы по шине 19 генератора / посредством схемы «И 29 он был установлен в «1. Поэтому на вход схемы «И 30 подается разрешающий потенциал с выхода схемы «И 26. На следующем такте схема работает аналогично. Пусть после первого такта происходит сбой триггера 9, а триггер S установлен в «О, тогда на выходе дешифратора соответствия 13 появляется потенциал «Запрет 2, который через схему «ИЛИ 46 поступает на вентилиформирователи 47 и 48. Импульсы первой и второй фазы генератора 1 не произведут в схеме по этой причине никаких изменений. Импульсом третьей фазы по шине 20 опрашивают схемы «И 42-45, на выходе схемы 42 появляется импульс, которым посредством схем «ИЛИ 39, 40, 41 устанавливают триггеры 9, 10 ъ 11 в нулевое состояние, а триггеры 5, 6 и 7-в единичное. Так как на первом такте триггер 8 был установлен в состояние «О, то в регистре результата нет ни одного триггера, находящегося в состоянии «1. По этой причине на выходе схемы «И 33 появляется разрещающий потенциал для схемы «И 28, так как на входы схемы «И 33 подают нулевой потенциал с выхода триггера 8 и разрешающий потенциал со схемы «И 32. На следующем такте в случае отсутствия сбоев импульс первой фазы опросит схемы «И 28-31. Так как только на схему «И 28 подан разрещающий потенциал, то импульсом первой фазы триггер 8 устанавливается в единичное состояние. Импульс второй фазы (в случае отсутствия помех) в схеме не произведет никаких изменений, так как на входы схем «И 21-23 подаются разрешающие потенциалы от схем «И 26, 27 и триггера 11. В дальнейшем схема работает аналогично рассмотренному выше. Во втором случае, например, триггер 11 устанавливается в единичное состояние после поступления импульса первой фазы на втором такте. Тогда на выходе дешифратора соответствия 15 появляется потенциал «Запрет 2, который через схему «ИЛИ 46 подается на вентили-формирователи 47 и 48. Поскольку на вентиль 48 подан потенциал «Запрет 2, то импульс второй фазы в схему не поступает. Импульсом третьей фазы опрашивают схемы «И 42-45. Так как на вход схемы 44 подан разрешающий потенциал с выхода дешифратора соответствия 15, то импульсом соответствия 15, то третьей фазы через схемы 41, 44 устанавливают триггер // в нулевое состояние, а триггер 7 - в единичное и подают его также на вход линии задержки 37. С выхода последней импульс посылают на входы схем «И 35, 36. С выхода линии задержки 38 на входы схем «И 35 и 36 подают в этот момент задержанПоскольку первым справа триггером, находящимся в состоянии «1, будет триггер 10 (так как импульсом первой фазы на втором такте посредством схемы «PI 30 триггер был установлен в состояние «1, то на выходе схемы «И 27 появляется разрешающий потенциал для схемы 36. Таким образом, импульсом с выхода схемы 36 триггер 10 устанавливается в «О, а триггер 6 - в «1 состояние. В дальнейшем схема работает аналогично рассмотренному выше.

Предмет изобретения

Аналого-цифровой преобразователь, содержащий генератор тактовых импульсов, регистр тактов, регистр результата, выходы триггеров которого подключены к соответствующим входам декодирующего преобразователя, а выход последнего соединен со входом сравнивающего устройства, ко входам которого подключены два выхода генератора импульсов и источник преобразуемого нанряжения, линии задержки, логические схемы, дешифраторы, отличающийся тем, что, с целью повышения достоверности измерений в условиях помех, единичные входы триггеров регистра результата соединены с нулевыми входами триггеров регистра тактов, а нулевые - с единичными соответственно, выходы триггеров регистров результата и тактов, кроме последнего, подключены ко входам ячеек дешифратора соответствия, а выходы последних триггеров - ко входу дешифратора несоответствия, выход которого через схему «И подключен к первому входу генератора тактовых импульсов, выходы дешифратора соответствия через схему «ИЛИ подключены ко входам вентилей-формирователей; первый выход генератора тактовых импульсов через вентиль подключен к одному входу сравнивающёго устройства и через схемы «И к единичным входам триггеров регистра результата и к нулевым входам триггеров регистра тактов, второй выход генератора через вентиль и через схемы «И подключен к нулевым

входам триггеров регистра результата и к единичным входам триггеров регистра тактов, другие входы этих схем «И подключены к выходу сравнивающего устройства, третий выход генератора тактовых импульсов соединен

со входом дешифратора несоответствия и со входами схем «И, другие входы которых подключены к выходам дешифраторов соответствия, выход каждой их этих схем «И, кроме первой, подключен к одному из входов соответствующей схемы «ИЛИ, выходы которых соединены с нулевыми входами соответствующих триггеров регистра тактов и результата, схемы «ИЛИ соединены между собой последовательно, и выход последней из них через

линию задержки и схему «И подключен к нулевым -входам триггеров регистра и результата,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬU..БИ&--^-- | 1973 |

|

SU385392A1 |

| ДЕКАДНЫЙ СЧЕТЧИК | 1971 |

|

SU320060A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД | 1970 |

|

SU271917A1 |

| Устройство для ввода информации | 1974 |

|

SU532095A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU563713A1 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ ОСЦИЛЛОГРАММ | 1968 |

|

SU218546A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ ВЕЛИЧИ В ЦИФРОВОЙ КОД | 1971 |

|

SU318963A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ НЕПРЕРЫВНЫХ ВИЗУАЛЬНЫХ КРИВЫХ | 1969 |

|

SU237458A1 |

Даты

1971-01-01—Публикация