1

Изобретение относится к цифровой вычислительной технике, в частност1И к устройствам для связи между цифровыми и аналоговыми вычислительными системамН.

Известны аналого-цифровые преобразователи, содержащие блоки компараторов, делитель напряжения, кодирующую матрицу, регистр кода со схемами «И линейно-декодирующий преобразователь, реверсивно-сдвигающий регистр и генератор тактов.

Цель изобретения - улучщение защиты от импульсных помех.

В предлагаемый преобразователь введены дополнительные компа1раторы, дополнительные схемы «И, «ИЛИ, дополнительный ля:нейно-декодирующий цреобразователь, причем выходы дополнительных схем «И, управляющие сдвигом реверсивно-сдвигающего регистр а, подключены к нулевым входам триггеров регистра кода; одни входы одной группы дополнительных схем «И подключены к выходу первой схемы «ИЛИ, входы которой соединены с нулевым входом первого и единичным выходом второго дополнительного компаратора; одни входы другой группы дополнительных схем «И подключены к выходу схемы «И, входы которой соединены с единичным выходом первого и нулевым выходом второго дополнительного компаратора; вторые входы первой и второй групп дополнительных схем

«И подключены к выходам соответствующих триггеров реверсивно-сдвигающего регистра; входы дополнительных схем «ИЛИ, управляющих дополнительным линейно-декодирующим преобразователем, соединены с выходами триггеров регистра кода и реверсивно-сдвигающего регистра; вход первого дополнительного компаратора соединен с выходом линейно-декодирующего преобразователя; вход второго дополнительного компаратора подключен к выходу дополнительного линейно-декодирующего преобразователя.

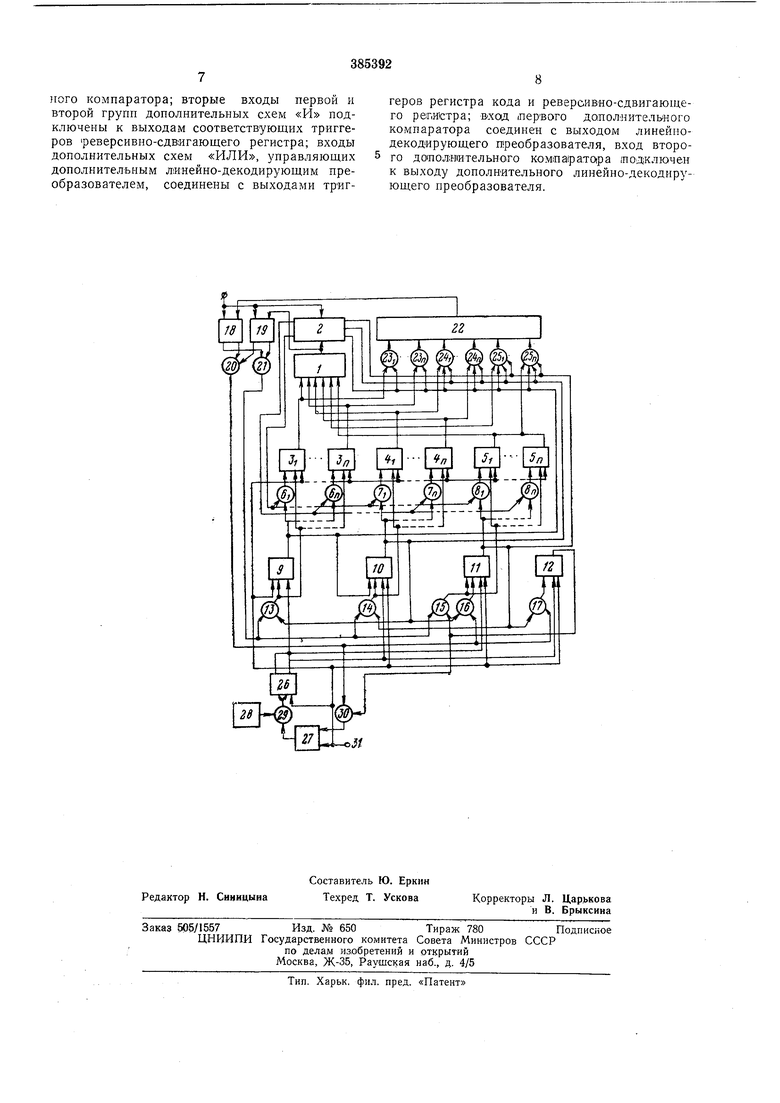

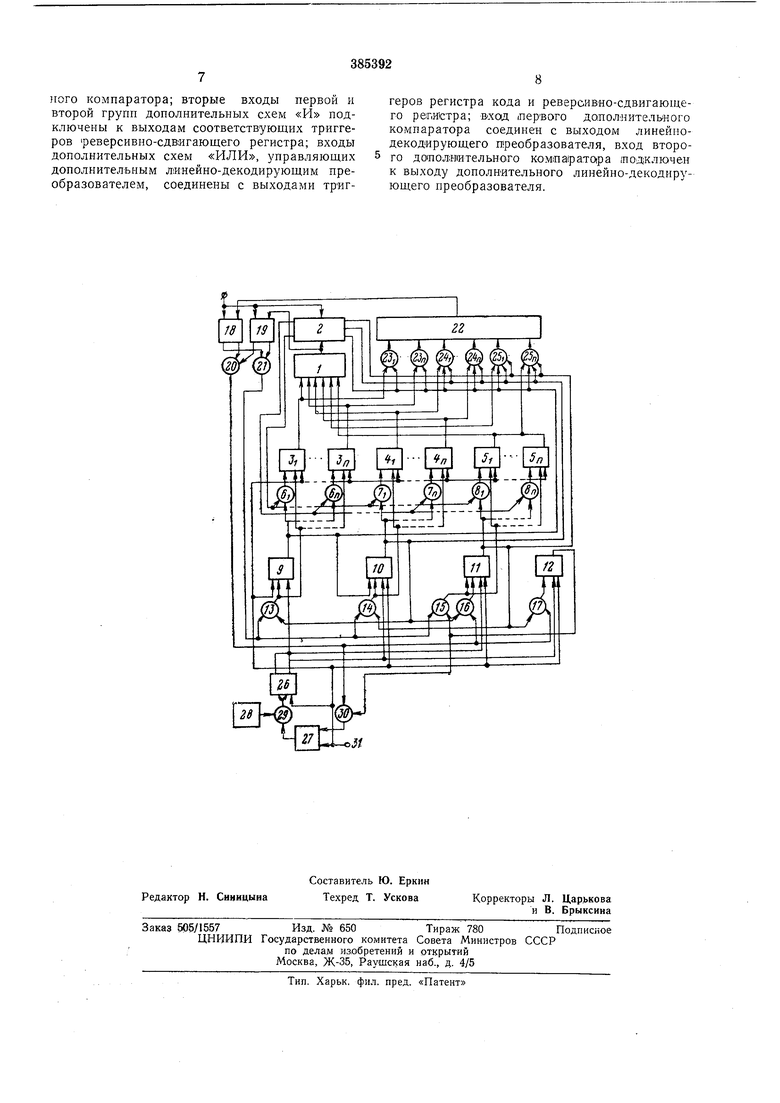

На чертеже приведена блок-схема предлагаемого п реобразователя.

Преобразователь состоит из основного линейно-декодирующего преобразователя (ЛДП) /, блока 2, содержащего набор компараторов, делитель напряжения и кодирующую матрицу, репистра кода, содержащего триггеры , 4.,4„, 5 --5ii, логическ|их схем «И , 7, -7,„ (Srt, управляющих записью сигналов из кодирующей матрицы в регистры кода; реверсивно-сдвигающего регистра (РСР), содерж ащего триггеры 9-12, логических схем «И 13-17, управляющих сдвигом РСР вправо и влево, и двух дополнительных компараторов 18, 19 с логическими схемами «И 20 и «ИЛИ 2J. В состав устройства входят также дополнительный ЛДП 22, управляемый логическими схемами «ИЛИ

23i-23n, , 25,25„, триггер 26, управляющий триггер 27, генератор тактовых импульсов 28 и две логические схемы «И 29 и 30.

Выход ЛДП 1 соединен с делителем н,апряжения блока 2 и с дополнительным компаратором 19. Выход ЛДП 22 соединен со входом компаратора 18. На втарые входы компараторов 18 п 19 подается входное напряжение Ux.

Выходы кодирующей матрицы блока 2 соединены со входами логических схем «И ,,/1 - 7,„ §1-б/г, управляющих записью числа в регистр кода.

К единичным входам первых трех триггеров 9-11 РСР подсоединены соответственно выходы логических схем «И 13-15, управляющих сдвигом РСР влево, а начиная с триггера 11 к единичным входам его и последующих триггеров подсоединены выходы логаческих схем «И 16, 17, управляющих сдвигом РСР вправо.

Первые входы логических схем «И 13- ,15 подсоединены к выходу схемы «ИЛИ 21, входы которой подключены к единичному выходу компаратора 18 и нулевому выходу компаратора 19.

Аналогично первые входы логических схем «И 16, 17 подключены к выходу схемы «И 20, входы которой соединены с нулевым выходом компаратора 18 и единичным выходом компаратора 19.

Вторые входы логичесюих схем «И 13-15 подключены к единичным выходам триггеров 10-12 соответственно, вторые входы логических схем «И 16 т 17 - к единичным выходам триггеров 10 И 11 соответственно. Выходы логических схем «ИЛИ ,,, , 25i-25„, соединены со входами дополйительного ЛДП 22. Входы схем «ИЛИ 25j-23„, соответствующие первому разряду ЛДП 22, соединены с выходами соответствующих триггеров 5,-3„ регистра кода и с выходом триггера 9. Входы схем «ИЛИ 24i-24„ соединены с выходами соответствующих триггеров 4i-4„ регистра кода и с выходами триггеров 9 и 10 РСР, входы схем «ИЛИ 25i-25„ - с выходами соответствующих тр1Ипгеров51--5„ реги:стра «ада и с выходами TipHirrepOB Р-:/1/РСР.

Выхоиы трИ1Лгер01Б 9-// подключены ко входу блока 2.

Предлагаемый преобразователь работает в двух режимах -- при отсутствии и при наличии на входе импульсных помех.

1) Режим отсутствия импульсных помех, i . При подаче на чклемму / си:гнала «пуск преобразователь устаяавливается в исходное состояние, при котором триггеры 3i-3„, , 5j-5п регистра кода и триггеры 10, 11, J2, 26 реверсивно-сдвигающего регистра находятся в состоянии «О, а триггер 9 РСР и управляющий триггер 27 - в состоянии «Ь. При этом с выхода «1 триггера 9 на один из входов лопических схем «И i-(5„, управляющих записью сигналов с кодирующей матрицы в триггеры первого разряда регистра кода, подается разрешающий потенциал. ОдHOBpeMCiiHO этот же потенциал подается на делитель напряжения блока 2 и дополнительный ЛДТ 22, благодаря чему на выходах делителя наюряжения фор,М1Ируется эталонное напряжение для основной группы компараторов, а на выходе дополнительного ЛДП 22

формируется эталонное напряжение Uaz Umax (Umax - предел измерения).

Но так как с выходов «1 триггеров регистра кода 1-3,1, 1-4„, 5i-5„ поданы на ЛДП / запирающие потенциалы, на выходе

ЛДП формируется эталонное напряжение

/э О.

С выхода «1 триггера 27 разрещающее напряжение поступает также на вход схемы «И 29, на второй вход которой подаются сигналы тактового генератора 28.

С выхода «О триггера 26 разрешающий потенциал поступает на вход «О триггера 9 РСР.

5 Так как на входы компараторов блока 2 и .дополнительных компараторов 18 и 19 поданы соответствующие эталонные напряжения с ЛДП / и 22, то на выходе гкодирующей матрицы блока 2 появляется код того интервала .J диапазона измеряемых напряжений, в котором находится измеряемое напряжение.

Первый импульс тактового генератора 28 через схему «И 29 (при наличии разрешающего потенциала триггера 27) переводит тригзд гер 26 в единичное состояние. При этом сигнал с выхода «О триггера 26 переводит триггер 9 во второе устойчивое состояние. Сигнал с его выхода обеспечивает запись кода из кодирующей матрицы в первый разряд регистра 0 кода, а также переводит триггер 10 во второе устойчивое состояние, в результате чего на выходе ЛДП 1 формируется эталонное напряжение, соответствующее цифровому значению первого разряда, которое затем подает5 ся на второй вход компаратора 19 и на смещение делителя напряжения в блоке 2.

На входы делителя напряжения блока 2 подается разрешающий потенциал с выхода триггера 10- при этом на выходе делителя 0 напряжения формируется эталонное напряжепие для компараторов блока 2, соответствующее второму такту работы комбинированного преобразователя.

На входы логических схем «ИЛИ 55 23i -f 23fi подаются разрешающие потенциалы, соответствующие коду первого разряда, записанному в триггеры 3i-Зп регистра кода. На входы логических схем «ИЛИ 24i-24,,, 25,-25п подается разрешающий побо тенциал с выхода триггера W РСР, в резуль-. тате чего на выходе ЛДП 22 формируется

aiH-l rr эталонное напряжение Umax, где

oi .- значение первого, разряда, полученного.

65 .ни пёрвом шаге;

bi - вес первого разряда. Напряжение с выхода ЛДП 22 подается на эталонный вход дополнительного компаратора 18. Разрешающий потенциал с выхода триггера W подается также на входы лолических схем «И . После подачи эталонных напряжений на все входы компараторов блока 2 и дополнительных компараторов 18 и 19 на выходе кодирующей мат|рицы блока 2 формируются кодовые сигналы второго разряда кода, которые поступают на входы логических схем «И ,,, , 5,. На выходе дополнительной логической схемы «ИЛИ 21 оказывается зашрающии потенциал для схем «И 13-15 РСР (при отсутствии импульсных помех на входе). Компаратор 19, сравнивающий напряжение --i. QJ (, и находится в еди«ич«ом соСТОЯНИИ, так как на первом такте И больше эталонного напряжения а.; компаратор 18 - в нулевом состоянии, так как на нервом такте (а, + 1) бчС выхода дополнятельной схемы «И 20 разрешающий потенциал подается на схемы «И 16, 17 и 30, удравляющие сдвигами РСР вправо, с выхода триггера 10 - на входы схем «И 13, 16. Второй Импульс с тактового генератора 28 через схему «И 29 переводит триггер 26 в «О. Импульсы с выхода триггера 26 поступают на нулевые входы триггеров 10, 12 РСР, Триггер 10 переходит в «О, а триггер 12 остается в состоянии «О. При этом импульс с выхода триггера 10 записывает соответствующие сигналы 02 из кодовой матрицы блока 2 через схемы «И 7,-7„ в триггеры второго разряда регистра кода. Импульс с Выхода триггера 10 не проходят через схему «И 13 на единичный вход триггера 9, так как на второй вход схемы «И 13 подан запирающий потенциал с выхода схемы «ИЛИ 21. По этой же причине не происходит сдвига единицы влево в РСР. Импульс с выхода триггера 10 проходит через логическую схему «И 16 на единичный вход триггера 11, переводя последний в состояние «1. На этом заканчивается второй такт работы устройства. В дальнейшем преобразователь работает так же, как на первом и втором тактах. 2) Режим наличия импульсных помех. Рассмот рим случай, когда импульсная помеха появляется на втором такте работы преобразователя. Если импульсная помеха отрицательной полярности, напряжение U + ( - амплиту .-г 7 тпп .да помехи) может оытьменьше и,,, положительной если помеха полярности - (-1 + 1). больше U,,в этом случае либо с нулевого выхода дополнительного компаратора 19, либо с единичного выхода дополнительного компаратора /5 на входы дополнительной схемы «ИЛИ 21 подается разрешающее напряжение, а на входы схемы «И 20 - запирающие напряжения с выходов обоих компараторов. С выхода схемы «ИЛИ 21 подается разрешающее напряжение на схемы «И 13-15, а с выхода схемы «И 20 - запирающий потенвиал «а схемы «И 15, 16, 30. „ Второй импульс с выхода тактового генератора 28 через схему «И 29 и триггер 26 переводит триггер 10 в состояние «О. Импульс с выхода триггера 10 поступает на схемы «И 13, 16, а так как на один из входов схемы «И 13 подан разрешающий потенциал с выхода схемы «ИЛИ 21, а на один из входов схемы «И 16 - запрещающий потенциал с выхода схемы «И 20, на выходе схемы «И 13 появляется сигнал, который поступает на единичный вход триггера 9 РСР и на нулевые входы триггерОБ 3i-5„ первого разряда регистра кода. Схема возвращается в состояние первого такта. Далее работа схемы протекает аналогично. Оцифровка первого разряда считается законченной, если во втором такте появляется разрешающий потенциал на выходе схемы «И 20, а запрещающий - на выходе схемы «ИЛИ 21 н происходит сдвиг вправо. Оцифровка последнего разряда будет закончена тогда, когда на выходе схемы «И 30 появится снтнал, который переведет управляющий триггер 27 в нулевое состояние. Предмет изобретения Аналого-цифровой преоб-разователь, содержащий блоки компараторов, делитель напряжения, кодирующую матрицу, регистр кода -о схемами «И, линейно-декодирующий преобразователь, реверсивно-сдвигающий регистр и генератор тактов, отличающийся тем, что, с целью улучшения защиты уст ройства от импульсных помех, в него введены дополнительные компараторы, дополнительные схемы «И, «ИЛИ, иостоднительный линейно-аекодирующий преобразователь, причем выходы дополнительных схем «И, управляющие сдвигом реверсивно-сдвигающего регистра, подключеты к нулевым входам триггеров регистра кода, одни входы одной группы дополнительных схем «И подключены к выходу первой схемы «ИЛИ, входы которой соединены с нулевым выходом первого и единичным выходом второго дополнительного компаратора, одни входы другой группы дополнительных схем «И подключены к выходу схемы «И, входы которой .соединены с единичным выходом первого и нзлевым выходом второго дополнительнего компаратора; вторые входы первой и второй групп дополнительных схем «И подключены к выходам соответствуюпдих триггеров реверсивно-сдвягающего регистра; входы дополнительных схем «ИЛИ, управляющих дополнительным линейно-декодирующим преобразователем, соединены с выходами триггеров регистра кода и ревероивио-сдвигаюп его регистра; вход лервото дополнительного компаратора соединен с выходом линейнодекодирующего преобразователя, вход второго дополиительного KOMioaipaTOipa (подключен к выходу дополнительного линейно-декодирующего преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код | 1972 |

|

SU447829A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU310270A1 |

| Преобразователь напряжение-код | 1972 |

|

SU474103A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| ТЕЙТМ- 1П 11^f vu4«*'pr'-'&i! Ti Ari!. -^t-i-^b»SHbJiKOTEaA | 1969 |

|

SU254223A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU563713A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ ВЕЛИЧИ В ЦИФРОВОЙ КОД | 1971 |

|

SU318963A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СЧЕТЧИКОВ ИМПУЛЬСОВ | 1970 |

|

SU281903A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ КОДОВ ПРИРАЩЕНИЯ ФУНКЦИИ | 1968 |

|

SU208344A1 |

Авторы

Даты

1973-01-01—Публикация