-I

Предлагаемое изобретение относится к устройствам для преобразования аналоговых величин в цифровой код с повышенной достоверностью результатов измерения в условиях воздействия на входе преобразователя импульсных помех любой амплитуды.

Р1звестеп преобразователь аналоговых величип в цифровой код, состоящий из генератора тактовых импульсов, связанного с ним регистра тактовых импульсов, триггеры которого, в свою очередь, связаны с соответствующими триггерами регистра результата. Выходы триггеров последнего подключены ко входам линейного декодирующего преобразователя, выход которого соединен с одним из входов сравнивающего устройства, а с другим его входом связан источник преобразуемого напряжения. Выход сравнивающего устройства подключен через схемы «И ко входам триггеров регистра результата.

Недостатком известного преобразователя является то, что он допускает только одноразовое измерение цифрового значения каждого разряда, поэтому обладает низкой степенью достоверности в условиях воздействия импульсных помех на входе преобразователя.

ловиях воздействия разнополярных импульсных помех.

Поставленная цель достигается тем, что выходы преобразователя- подключены ко входам связанных между собой триггеров, выходы которых, как и выходы преобразователя, подсоединены через вентили и схему «ИЛИ к одному из входов управляющего триггера преобразователя. Выходы триггеров и выход

генератора тактовых импульсов связаны также со схемой «И, выход которой подключен ко входам упомянутых триггеров.

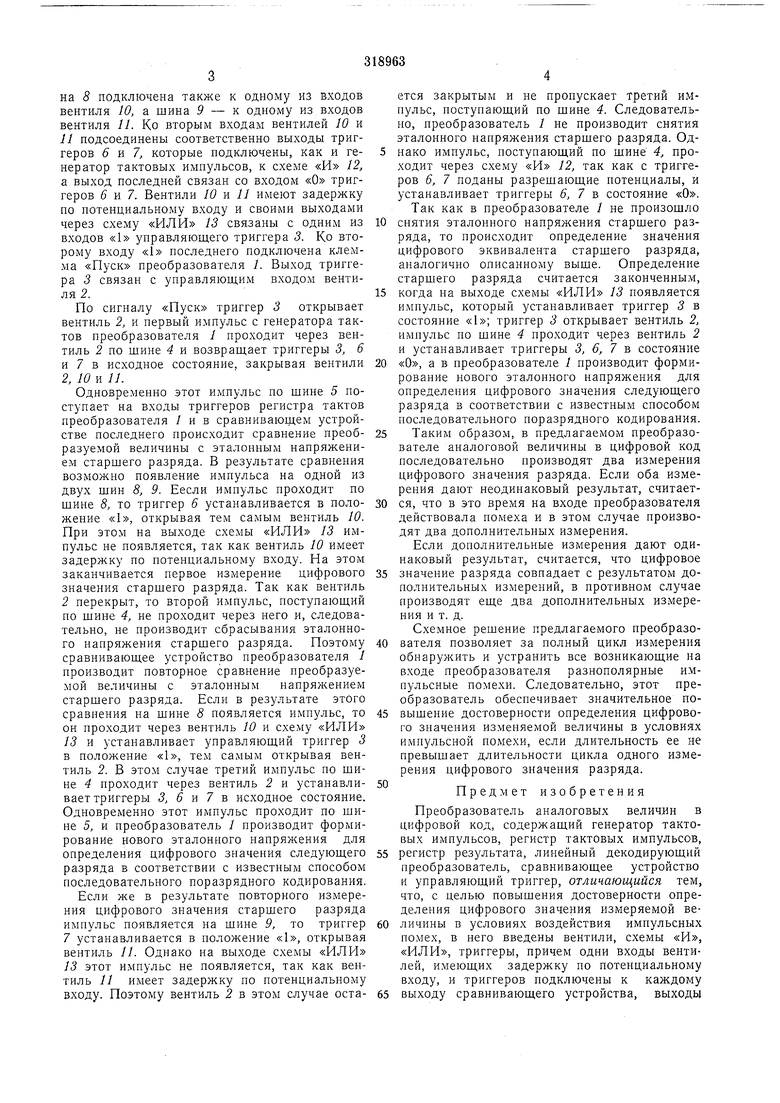

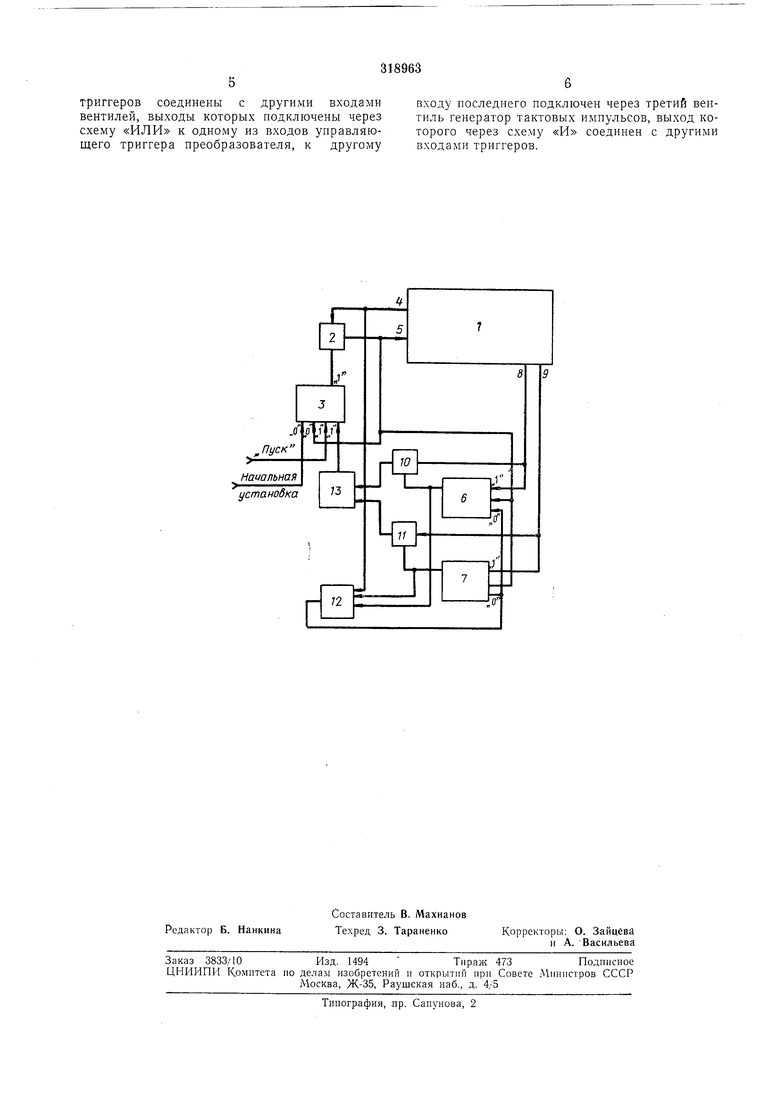

На чертеже изображена структурная блоксхема предлагаемого преобразователя аналоговой величины в цифровой код.

Собственно преобразователь J выполнен по принципу последовательного поразрядного кодирования и может иметь такое же схемное исполнение как и известный преобразователь.

Изображенные на чертеже вентиль 2 и триггер 3, расположенные на входе преобразователя /, вынесены из него для больщей наглядности. Причем через вентиль 2 выход генератора тактовых импульсов преобразователя подключен к его регистру тактовых импульсов шинами 4 и 5, а также ко входам «О управляющего триггера 3 и триггеров 6 и 7. Ко входам «1 триггеров 6 и 7 подсоединены выходы сравнивающего устройства преобрана 8 подключена также к одному из входов вентиля 10, а шнна 9 - к одному из входов вентиля 11. Ко вторым входам вентилей 10 и 11 подсоединены соответственно выходы триггеров 6 к 7, которые подключены, как и генератор тактовых импульсов, к схеме «И 12, а выход последней связан со входом «О триггеров б и 7. Вентили 10 id 11 имеют задержку по потенциальному входу и своими выходами через схему «ИЛИ 13 связаны с одним из входов «1 управляющего триггера 3. Ко второму входу «1 последнего подключена клемма «Пуск преобразователя /. Выход триггера 3 связан с управляющим входом вентиля 2.

По сигналу «Пуск триггер 3 открывает вентиль 2, и первый импульс с генератора тактов преобразователя 1 проходит через вентиль 2 но шине 4 и возвращает триггеры 3, 6 и 7 в исходное состояние, закрывая вентили 2, 10 и 11.

Одновременно этот импульс но щине 5 поступает на входы триггеров регистра тактов преобразователя /ив сравнивающем устройстве последнего происходит сравнение преобразуемой величины с эталонным напряжением старщего разряда. В результате сравнения возможно появление импульса на одной из двух щин 8, 9. Несли импульс проходит но щине 8, то триггер 6 устанавливается в положение «1, открывая тем самым вентиль 10. При этом на выходе схемы «ИЛИ 13 импульс не появляется, так как вентиль 10 имеет задержку по потенциальному входу. На этом закапчивается первое измерение цифрового значения старщего разряда. Так как вентиль 2 перекрыт, то второй импульс, поступающий по щнне 4, не проходит через него и, следовательно, не нроизводит сбрасывания эталонного напряжения старщего разряда. Поэтому сравнивающее устройство преобразователя 1 производит повторное сравнение преобразуемой величины с эталонным напряжением старщего разряда. Если в результате этого сравнения на щине 8 появляется импульс, то он проходит через вентиль 10 и схему «ИЛИ 13 и устанавливает управляющий триггер -3 в положение «1, тем самым открывая вентиль 2. В этом случае третий импульс по щине 4 проходит через вентиль 2 и устанавливает триггеры 5, 5 и 7 в исходное состояние. Одновременно этот импульс проходит но щине 5, и преобразователь / производит формирование нового эталонного напряжения для определения цифрового значения следующего разряда в соответствии с известным способом последовательного поразрядного кодирования.

Если же в результате повторного измерения цифрового значения старшего разряда импульс появляется на щине 9, то триггер 7 устанавливается в полол :ение «1, открывая вентиль 11. Однако на выходе схемы «ИЛИ 13 этот импульс не появляется, так как вентиль 11 имеет задержку по потенциальному входу. Поэтому вентиль 2 в этом случае остается закрытым н не пропускает третий импульс, поступающий по щине 4. Следовательно, преобразователь / не производит снятия эталонного напряжения старщего разряда. Однако импульс, поступающий но шине 4, проходит через схему «И 12, так как с триггеров 6, 7 поданы разрешающие потенциалы, и устанавливает триггеры 6, 7 в состояние «О. Так как в преобразователе / не произошло

снятия эталонного напряжения старщего разряда, то происходит определение значения цифрового эквивалента старщего разряда, аналогично описанному выше. Определение старщего разряда считается законченным,

когда на выходе схемы «ИЛИ 13 появляется импульс, который устанавливает триггер 3 в состояние триггер 3 открывает вентиль 2, имиульс по щине 4 проходит через вентиль 2 и устанавливает триггеры 3, 6, 7 ъ состояние

«О, а в преобразователе 1 производит формирование нового эталонного напряжения для определепия цифрового значения следующего разряда в соответствии с известным способом последовательного норазрядного кодирования.

Таким образом, в предлагаемом преобразователе аналоговой величины в цифровой код последовательно производят два измерения цифрового значения разряда. Если оба измерения дают неодинаковый результат, считается, что в это время на входе нреобразователя действовала помеха и в этом случае производят два дополнительных измерения.

Если дополнительные измерения дают одинаковый результат, считается, что цифровое

значение разряда совпадает с результатом дополнительных измерений, в противном случае производят еще два дополнительных измерения и т. д. Схемное решение предлагаемого преобразователя позволяет за полный цикл измерения обнаружить и устранить все возникающие на входе преобразователя разнополярные импульсные помехи. Следовательно, этот преобразователь обеспечивает значительное повыщение достоверности определения цифрового значения изменяемой величины в условиях импульсной помехи, если длительность ее не превышает длительности цикла одного измерения цифрового значения разряда.

гт

Предмет изооретения

Преобразователь аналоговых величин в цифровой код, содержащий генератор тактовых импульсов, регистр тактовых импульсов,

регистр результата, линейный декодирующий преобразователь, сравнивающее устройство и: управляющий триггер, отличающийся тем, что, с целью повышения достоверности определения цифрового значения измеряемой величины в условиях воздействия имнульсных помех, в него введены вентили, схемы «И, «ИЛИ, триггеры, причем одни входы вентилей, имеющих задержку по потенциальному входу, и триггеров нодключены к каждому

триггеров соединены с другими входами вентилей, выходы которых подключены через схему «ИЛИ к одному из входов управляющего триггера преобразователя, к другому

входу последнего подключен через третий вентиль генератор тактовых импульсов, выход которого через схему «И соединен с другими входами триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU310270A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬBr^irr^f^^.ocitJ и а ^ и»^ ^^- \^ f "^.' -^' S i.' . /I'i.';'^-:; •^;-"'-J ; iXJ'4-'^, | 1972 |

|

SU332567A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬU..БИ&--^-- | 1973 |

|

SU385392A1 |

| ГЕНЕРАТОР ДУГ ОКРУЖНОСТЕЙ | 1973 |

|

SU397902A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1972 |

|

SU416721A1 |

| ЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU268038A1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| УСТРОЙСТВО ДИСКРЕТНОЙ АВТОМАТИЧЕСКОЙ ПЕРЕСТРОЙКИ ЧАСТОТЫ | 1971 |

|

SU291302A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU395875A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО | 1971 |

|

SU293297A1 |

Даты

1971-01-01—Публикация