Предлагас.мое устройство относится к области моделирования случайных процессов на вычислительны.х машинах.

Известны генераторы случайных чисел, нозволяющие .получать некоррелированные последовательности чисел с любым требуемььм одномерным законом распределения вероятностей.

Одиако в известных устройствах невозможно лолученне последовательностей чисел с корреляционной функцией, отличной от дельтаобразной функции.

Предлагаемый генератор случайных чисел реализует способ получения случайных лоследовательностей с заданной автокорреляционной функцией без нзменения одномерного закона распределения вероятностей и отличается тем, что содержит устройство сравнения, связанное через второй регистр с заноминающим устройством и через логические схемы «И и «ИЛИ с двумя счетчиками, которые через схему «И подключены к предвыходному регистру, соединенному со вторым и выходным регистрами.

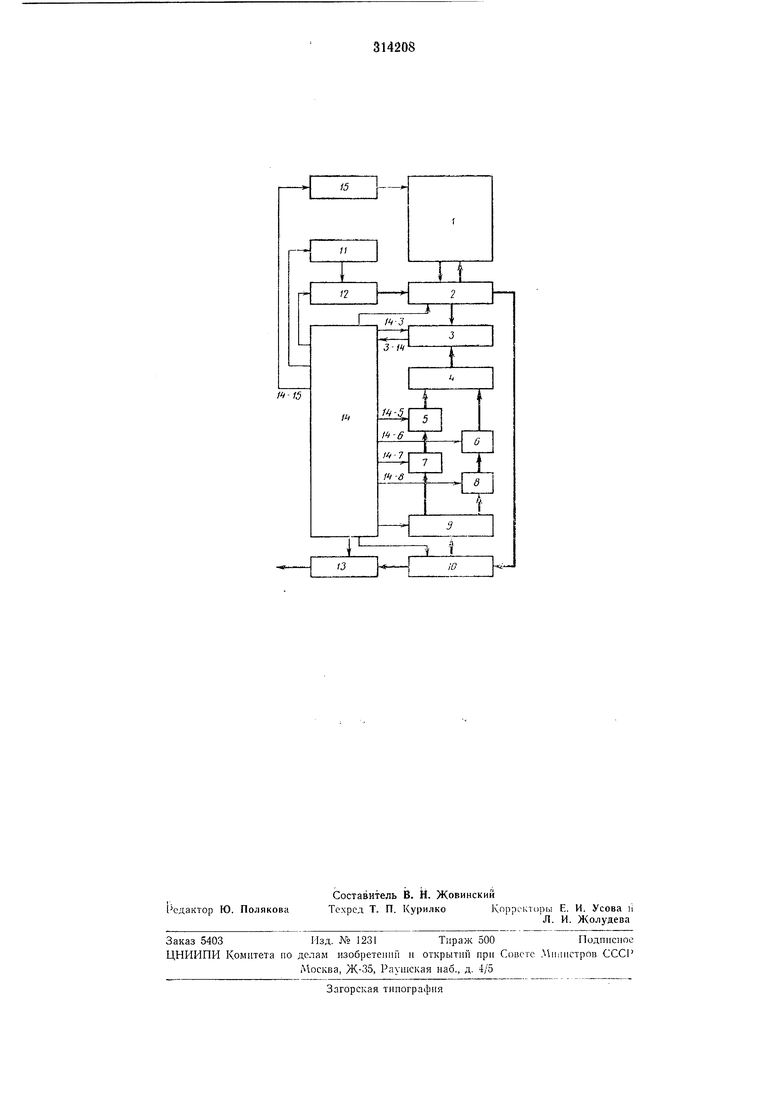

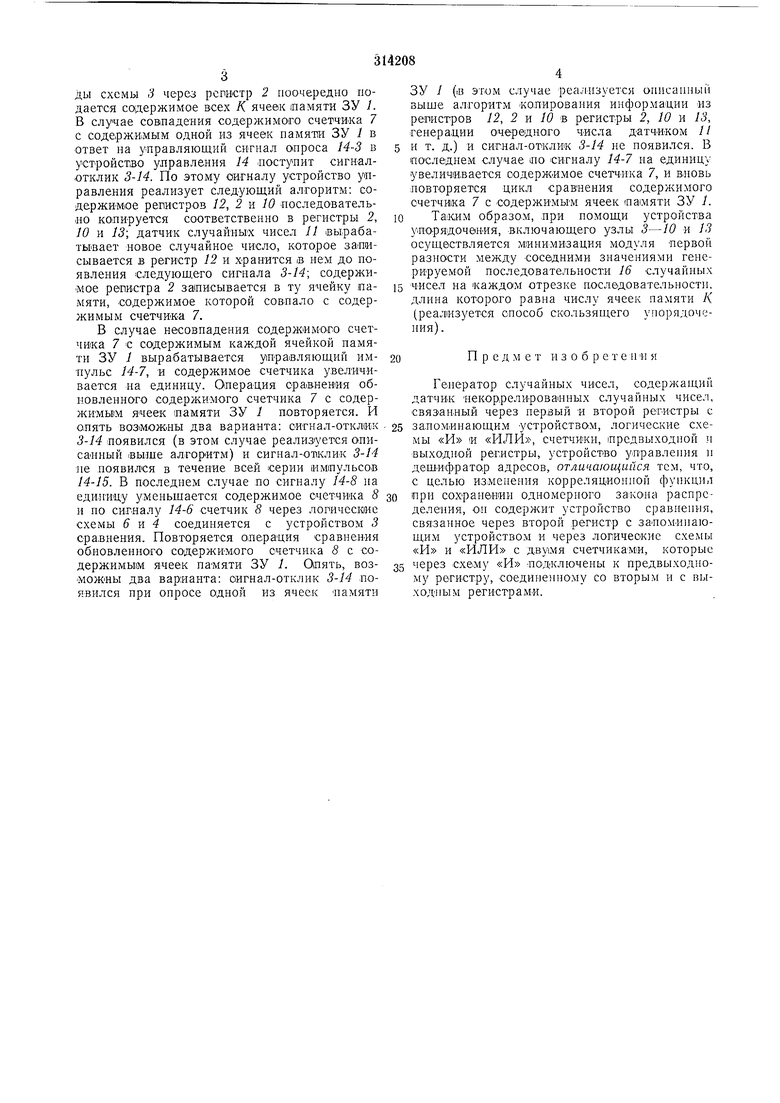

Блок-схема устройства показана на чертеже. Заноминающее устройство / через регистр 2 заноминающето устройства (ЗУ) связано с устройство 3 сравнения. Последнее через логические схемы «ИЛИ 4 и логические схемы «И 5 и 6 связано со счетчиками 7 и S импульсов. Счетчики 7 и 8 отличаются друг от друга тем, что нервый из них работает в режиме уве.мичеиия содержимого счетчика с приходом на счетный вход каждого управляющего сигнала, а второй - ;В режн.ме умен15шспия содержимого счетчика. Счетчики 7 и S через логическую схему «И 9 связаны с предвыходным регистром 10. Датчик 11 некоррелированных случайных чисел и выходной регистр 12 датчика случайных чисел последовательно соединены с регистрами 2, 10 и выходным регистром 13 всего устройства.

Устройство 14 управления через дешифратор 15 адреса вырабатывает унравляющне сигналы для заноминаюн1,его устройства 1. Оно также связано со всеми остальнымн функцнональнымн узлами устройства управляющими шиналш, которые на чертеже изображены тонкими линиями. Все информационные каналы на чертеже показа ны жирными линиями. Запоминающее устройство / содержит разрядных ячеек.

Схема работает следующим образом.

Ииформацня из регистра 10 копируется через логическую схему «И 9 в счетчики 7 и 8. По сигналу 14-5 через схемы 5 4 счетчик 7 соединяется с устройством 3 сравнения. Далее управляющее устройство 14 вырабатывает серню управляющих сигналов 14-15, с помощью которых иа ипформациоиные входы схемы 3 через регистр 2 поочередно подается содержимое всех /С ячеек памяти ЗУ /. В случае совпадения содержимого счетчика 7 с содержимым одной из ячеек памят1И ЗУ в ответ на управляющий сигнал опроса 14-3 в устройство улравления 14 поступит ситналотклик 3-14. По этому сигналу устройство управления реализует следующий алгоритм: содержимое репистров 12, 2 и 10 иоследователь«0 колируется соответственно в регистры 2, 10 и 13; датчик случайных чисел 11 вырабатьгвает новое случайное число, которое записывается в регистр 12 и хранится IB нем до появления следуюш.его сигнала 3-М; содержимое репистра 2 записывается в ту ячейку памяти, содержимое которой совпало с содержимым счетчика 7.

В случае несовпадения содержимого счетчика 7 с содержимым каждой ячейкой намяти ЗУ 1 вырабатывается управляющий импульс 14-7, и содержимое счетчика увеличивается на единицу. Операция сравнения обновленного содержимого счетчика 7 с содержимым ячеек памяти ЗУ 1 повторяется. И о.пять возможны два варианта: сигнал-отклик 3-14 появился (в этом случае реализуется описанный выше алгоритм) и сигнал-от1клик 3-14 не появился в течение всей серии импульсов 14-15. В последнем случае по сигналу 14-8 на единицу уменьшается содержимое счетчика 8 и но сигиалу 14-6 счетчик 8 через лопичесше схемы 6 к 4 соединяется с устройством 3 сравнения. Повторяется операция сравнения обловленного содержимого счетчика 8 с содержимым ячеек памяти ЗУ 1. Опять, возможны два варианта: сигнал-отклик 3-14 появился при опросе одной из ячеек памяти

ЗУ 1 (| этом случае реализуется онисапный выще алгоритм -копирования информации из регистров 12, 2 Е 10 ъ регистры 2, 10 и 13, генерации очередного числа датчиком //

и т. д.) и снгиал-отклик 3-14 не появился. В последнем случае по сигналу 14-7 на единицу увеличивается содерлшмое счетчика 7, и вновь повторяется цикл сравнения содержимого счетчика 7 с содержимым ячеек па1мяти ЗУ 1.

Таким образом, при помощи устройства упорядочения, включающего узлы 3-10 и 13 осуществляется минимизация модуля первой разно1сти между соседними значениями генерируемой последовательности 16 случайных

чисел на каждОМ отрезке носледовательности. длина которого равна числу ячеек памяти /( (реал изуется способ скользящего упорядочения).

Пред м е т и з о б р е т е п -н я

Генератор случайных чисел, содержащий датчик пекоррелироваашых случайных чисел, связанный через первый и второй регистры с запоминающим устройством, логические схемы «И и «ИЛИ, счетчики, предвыходной и выходной регистры, устройство управления и дешифратор адресов, отличающийся тем, что, с целью изменения корреляционной функцил При сохранении одномерного распределения, он содержит устройство сравнения, связанное через второй регистр с запоминающим устройством и через логические схемы «И и «ИЛИ с дву1мя счетчиками, которые через схему «И подключены к предвыходному регистру, соединенному со вторым и с выходным регистрами.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНАЯ I | 1973 |

|

SU370601A1 |

| Генератор случайных чисел | 1974 |

|

SU516042A2 |

| Генератор случайных чисел | 1985 |

|

SU1262492A1 |

| Генератор последовательностей случайных чисел | 1986 |

|

SU1374220A2 |

| Генератор многомерных случайных процессов | 1990 |

|

SU1755279A1 |

| Генератор последовательности случайных чисел | 1984 |

|

SU1251071A1 |

| Генератор последовательностей случайных чисел | 1990 |

|

SU1836680A3 |

| Генератор случайных чисел | 1985 |

|

SU1275436A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

Даты

1971-01-01—Публикация