Изобретение относится к моделированию случайных величин и процессов на вычислительных маап/ jax и может быть использовано в качестве приставки или внутреннего блока электронной вычислительной машины.

Цель изобретения - расширение функциональных возможностей за счет формирования экспоненциально-косинусной корреляционной зависимости между реализациями многомерного случайного процесса или поля.

Сущность работы предлагаемого устройства состоит в организации перестановки реализации многомерного случайного процесса или случайного поля с требуемым законом распределения вероятностей по правилу выбора из некоторой исходной ограниченной совокупности реализации с суммой компонентов, наиболее близкой по

модулю к сумме компонентов последней прогенерированной реализации. Суммирование компонентов реализаций обеспечивает возможность простого их сравнения для последующего выбора одной реализации из исходной их совокупности, Введение регистра памяти и схемы сравнения.обеспе- чивает задание управляющего параметра процесса генерирования - объема ограниченной совокупности исходных реализаций

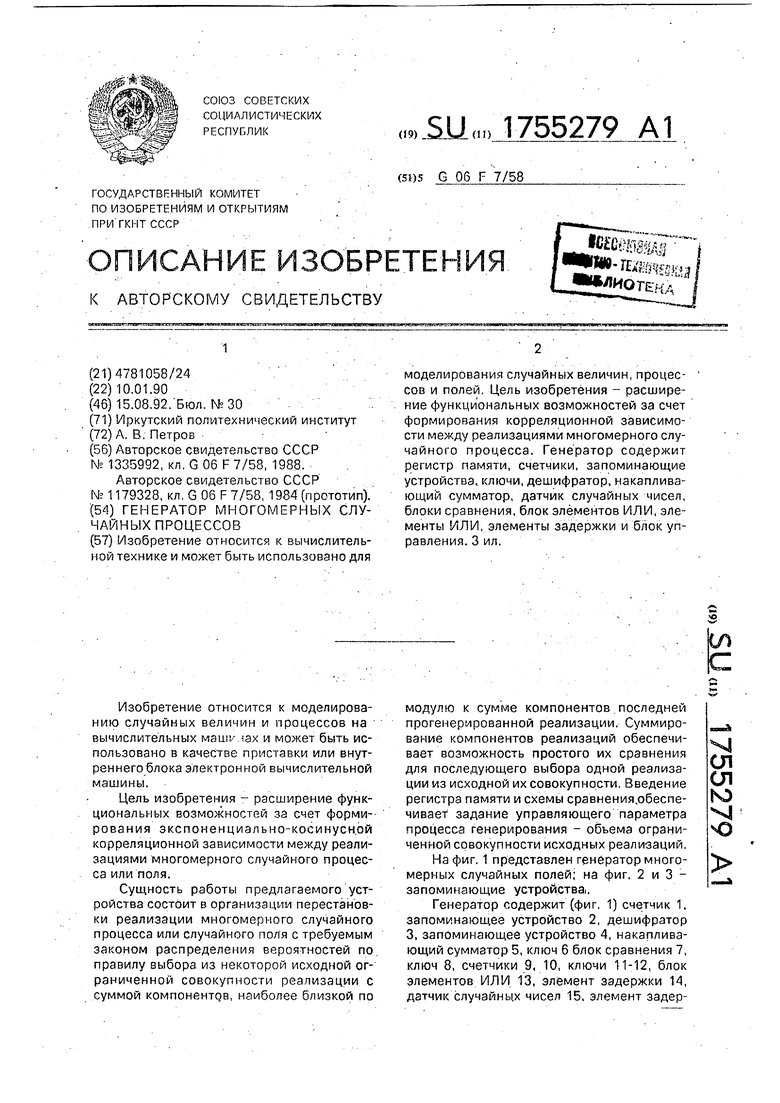

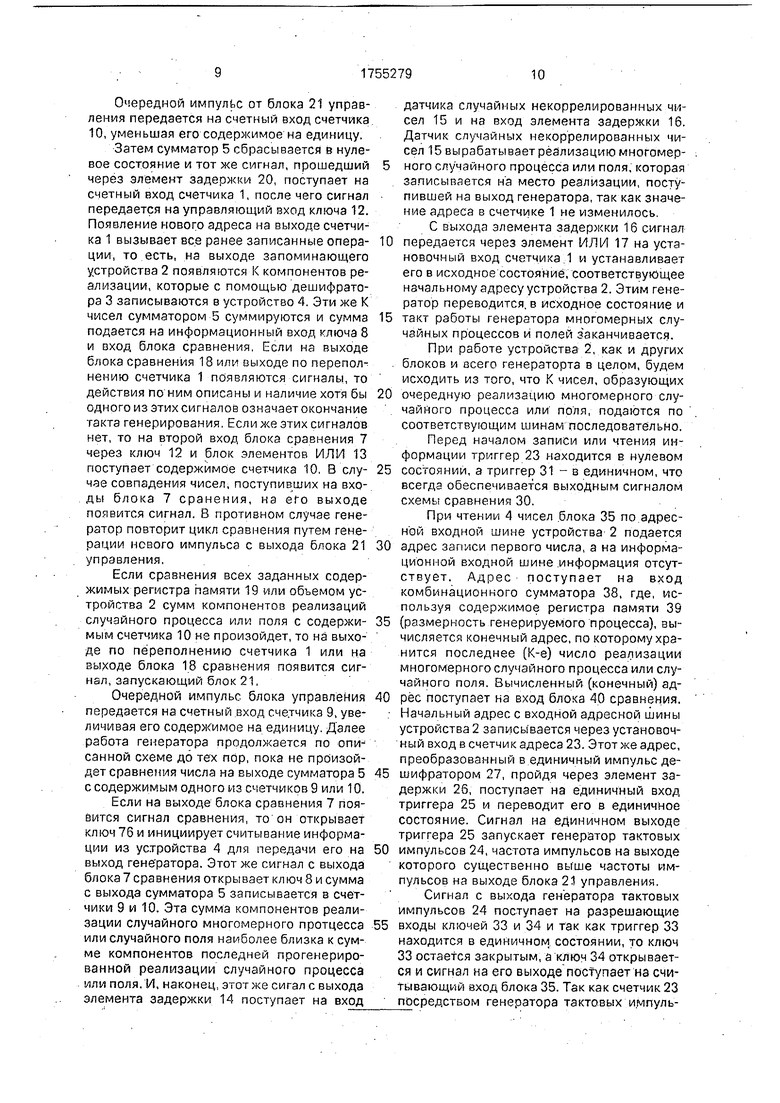

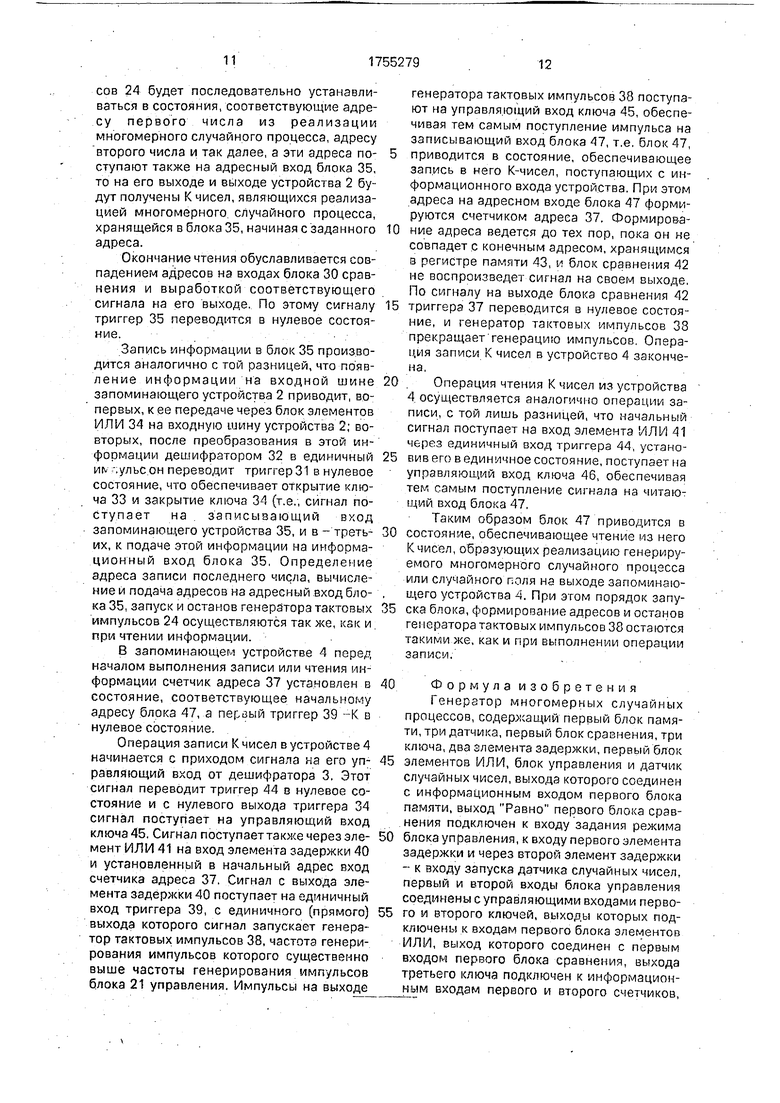

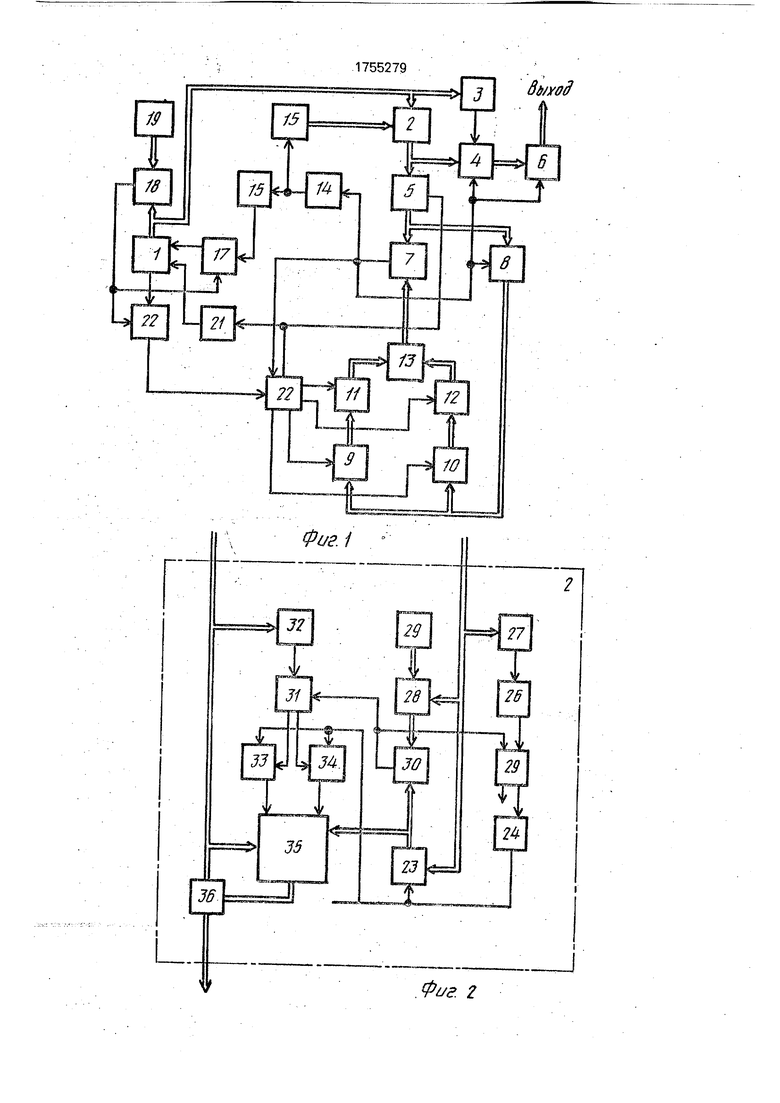

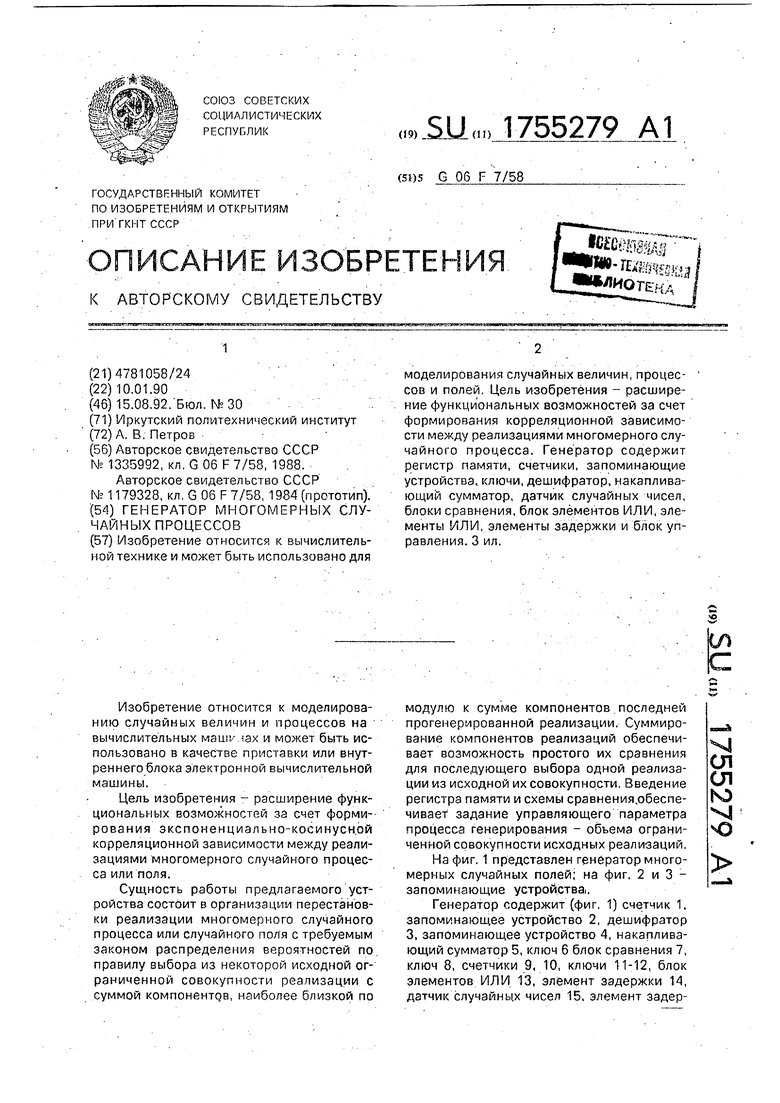

На фиг, 1 представлен генератор многомерных случайных полей; на фиг. 2 и 3 - запоминающие устройства,.

Генератор содержит (фиг. 1) счетчик 1, запоминающее устройство 2, дешифратор 3, запоминающее устройство 4, накапливающий сумматор 5, ключ 6 блок сравнения 7, ключ 8, счетчики 9, 10, ключи 11-12, блок элементов ИЛИ 13, элемент задержки 14, датчик случайных чисел 15, элемент задерслел

ю

х|

ю

жки 16, элемент ИЛИ 17, блок 18 сравнения, регистр 19 памяти, элемент задержки 20, блок 21 управления, элемент задержки 20, блок 21 управления, элемент ИЛИ 22.

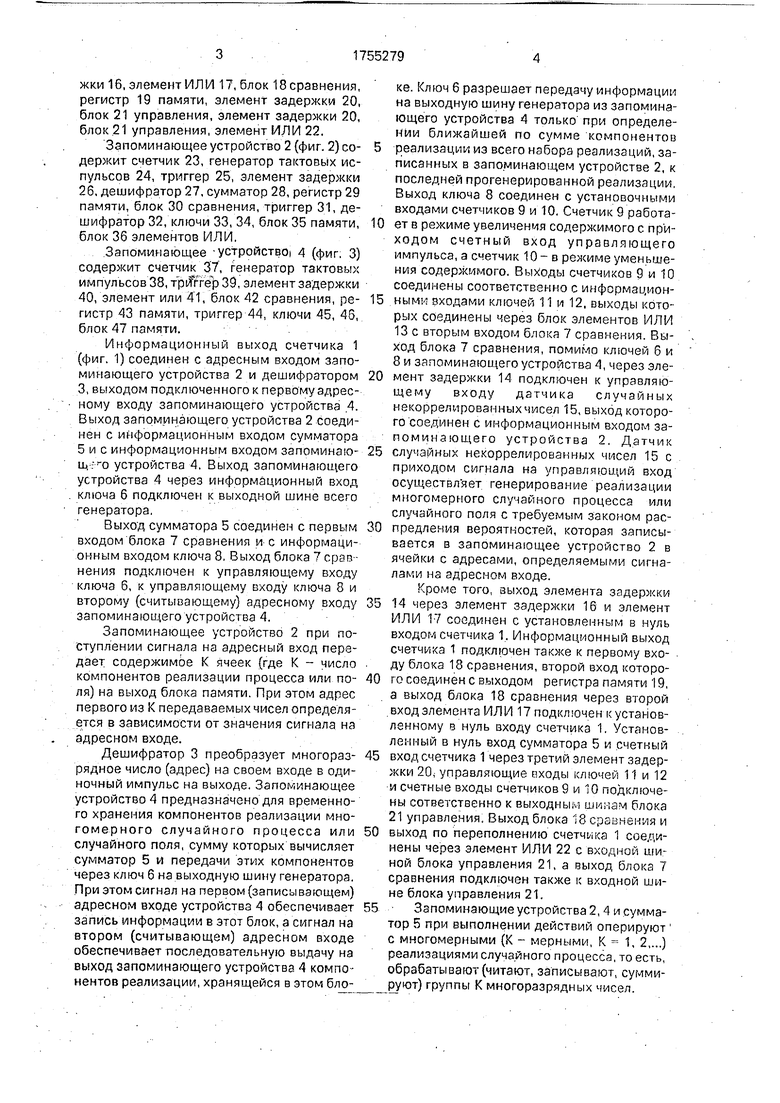

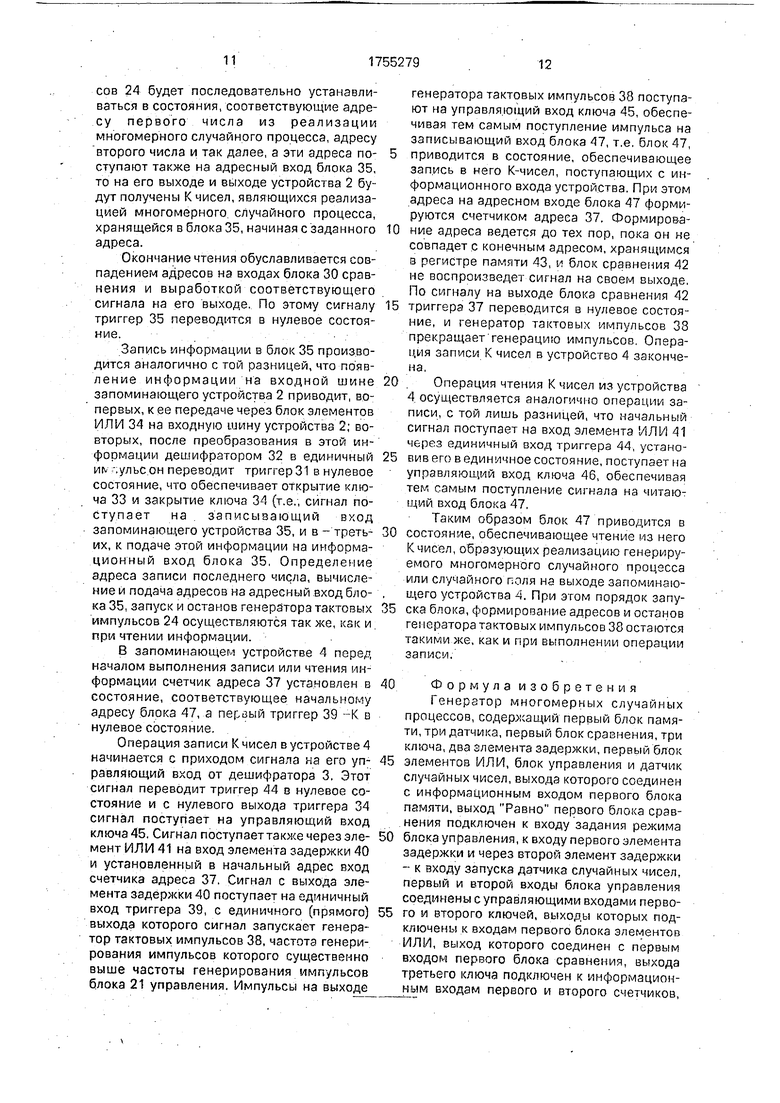

Запоминающее устройство 2 (фиг. 2) содержит счетчик 23, генератор тактовых ис- пульсов 24, триггер 25, элемент задержки 26, дешифратор 27, сумматор 28, регистр 29 памяти, блок 30 сравнения, триггер 31, дешифратор 32, ключи 33, 34, блок 35 памяти, блок 36 элементов ИЛИ.

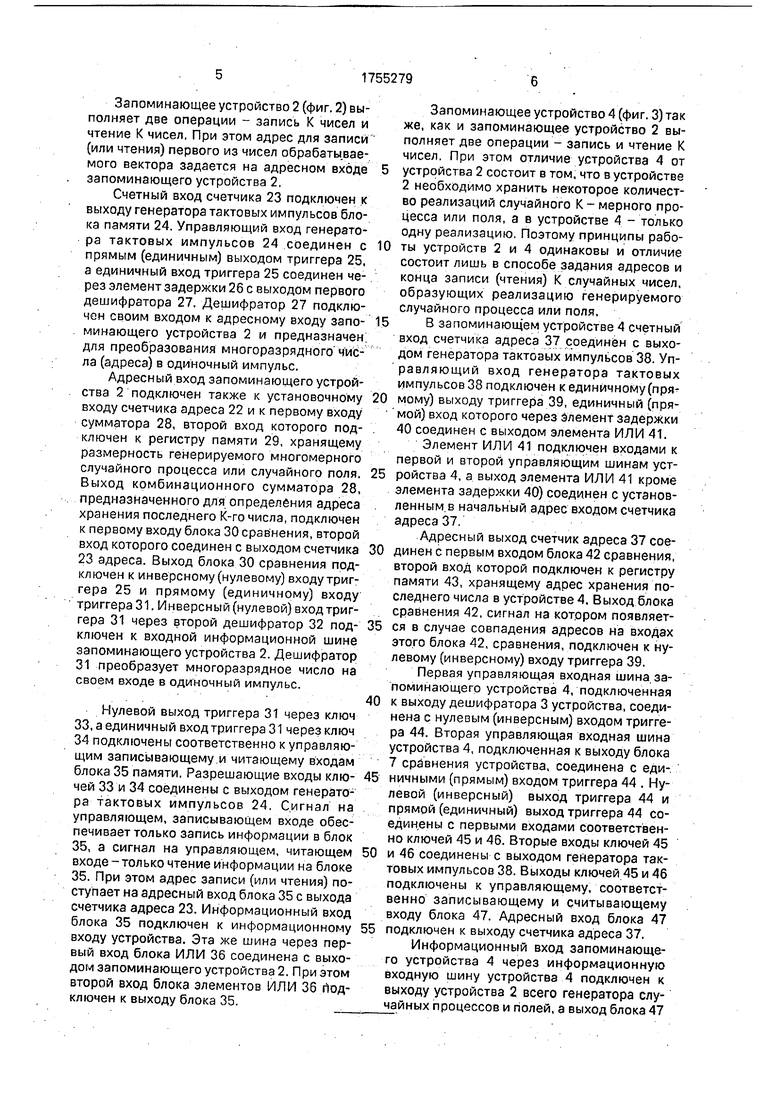

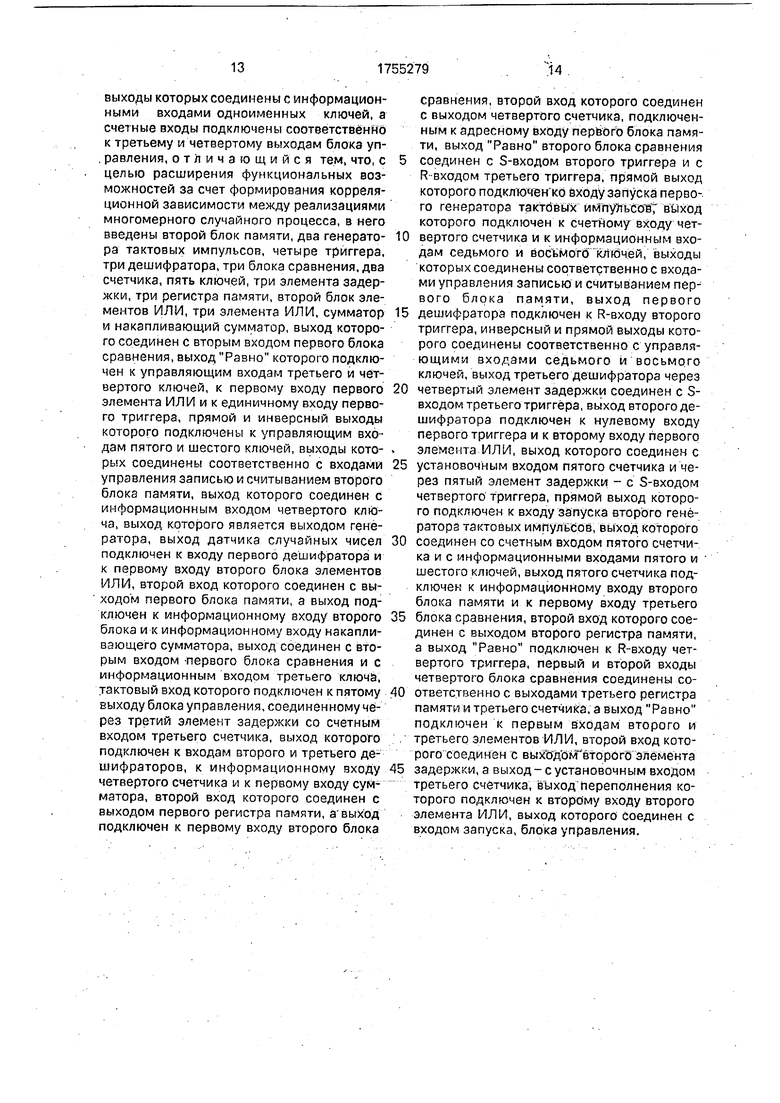

Запоминающее устройство| 4 (фиг. 3) содержит счетчик 37, генератор тактовых импульсов 38, триггер 39, элемент задержки 40, элемент или 41, блок 42 сравнения, регистр 43 памяти, триггер 44. ключи 45, 46, блок 47 памяти.

Информационный выход счетчика 1 (фиг. 1) соединен с адресным входом запоминающего устройства 2 и дешифратором 3, выходом подключенного к первому адресному входу запоминающего устройства 4. Выход запоминающего устройства 2 соединен с информационным входом сумматора 5 и с информационным входом запоминаю- щ-го устройства 4. Выход запоминающего устройства 4 через информационный вход ключа 6 подключен к выходной шине всего генератора.

Выход сумматора 5 соединен с первым входом блока 7 сравнения и с информационным входом ключа 8. Выход блока 7 срап нения подключен к управляющему входу ключа 6, к управляющему входу ключа 8 и второму (считывающему) адресному входу запоминающего устройства 4.

Запоминающее устройство 2 при поступлении сигнала на адресный вход передает содержимое К ячеек (где К - число компонентов реализации процесса или поля) на выход блока памяти. При этом адрес первого из К передаваемых чисел определяется в зависимости от значения сигнала на адресном входе.

Дешифратор 3 преобразует многоразрядное число (адрес) на своем входе в одиночный импульс на выходе. Запоминающее устройство 4 предназначено для временного хранения компонентов реализации многомерного случайного процесса или случайного поля, сумму которых вычисляет сумматор 5 и передачи этих компонентов через ключ б на выходную шину генератора, При этом сигнал на первом (записывающем) адресном входе устройства 4 обеспечивает запись информации в этот блок, а сигнал на втором (считывающем) адресном входе обеспечивает последовательную выдачу на выход запоминающего устройства 4 компонентов реализации, хранящейся в этом блоке. Ключ 6 разрешает передачу информации на выходную шину генератора из запоминающего устройства 4 только при определении ближайшей по сумме компонентов

реализации из всего набора реализаций, записанных в запоминающем устройстве 2, к последней прогенерированной реализации, Выход ключа 8 соединен с установочными входами счетчиков 9 и 10. Счетчик 9 работа0 ет в режиме увеличения содержимого с приходом счетный вход управляющего импульса, а сметчик 10- в режиме уменьшения содержимого. Выходы счетчиков 9 и 10 соединены соответственно с информзцион5 нымк входами ключей 11 и 12, выходы которых соединены через блок элементов ИЛИ 13 с вторым входом блока 7 сравнения. Выход блока 7 сравнения, помимо ключей 6 и 8 и запоминающего устройства 4, через эле0 мент задержки 14 подключен к управляющему входу датчика случайных некоррелированных чисел 15,выход которого соединен с информационным входом за- поминающего устройства 2. Датчик

5 случайных некоррелированных чисел 15 с приходом сигнала на управляющий вход осуществляет генерирование реализации многомерного случайного процесса или случайного поля с требуемым законом рас0 предления вероятностей, которая записывается в запоминающее устройство 2 в ячейки с адресами, определяемыми сигналами на адресном входе.

Кроме того, выход элемента задержки

5 14 через элемент задержки 16 и элемент ИЛИ 17 соединен с установленным в нуль входом счетчика 1. Информационный выход счетчика 1 подключен также к первому входу блока 18 сравнения, второй вход которо0 го соединен с выходом регистра памяти 19, а выход блока 18 сравнения через второй вход элемента ИЛИ 17 подключен ((установленному в нуль входу счетчика 1. Установленный в нуль вход сумматора 5 и счетный

5 вход счетчика 1 через третий элемент задержки 20, управляющие входы ключей 11 и 12 и счетные входы счетчиков 9 и 10 подключены сответственно к выходньы шмлам блока 21 управления. Выход блока 18 сравнения и

0 выход по переполнению счетчика 1 соединены через элемент ИЛИ 22 с входной шиной блока управления 21, а выход блока 7 сравнения подключен также к входной шине блока управления 21.

5 Запоминающие устройства 2,4 и сумматор 5 при выполнении действий оперируют с многомерными (К - мерными, К - 1, 2,...) реализациями случайного процесса, то есть, обрабатывают (читают, записывают, суммируют) группы К многоразрядных чисел.

Запоминающее устройство 2 (фиг. 2) выполняет две операции - запись К чисел и чтение К чисел, При этом адрес для записи (или чтения) первого из чисел обрабатываемого вектора задается на адресном входе запоминающего устройства 2,

Счетный вход счетчика 23 подключен к выходу генератора тактовых импульсов блока памяти 24. Управляющий вход генератора тактовых импульсов 24 соединен с прямым (единичным) выходом триггера 25, а единичный вход триггера 25 соединен через элемент задержки 26 с выходом первого дешифратора 27. Дешифратор 27 подключен своим входом к адресному входу запоминающего устройства 2 и предназначен для преобразования многоразрядного числа (адреса) в одиночный импульс.

Адресный вход запоминающего устройства 2 подключен также к установочному входу счетчика адреса 22 и к первому входу сумматора 28, второй вход которого подключен к регистру памяти 29, хранящему размерность генерируемого многомерного случайного процесса или случайного поля. Выход комбинационного сумматора 28, предназначенного для определения адреса хранения последнего К-го числа, подключен к первому входу блока 30 сравнения, второй вход которого соединен с выходом счетчика 23 адреса. Выход блока 30 сравнения подключен к инверсному (нулевому) входу триггера 25 и прямому (единичному) входу триггера 31. Инверсный (нулевой) вход триггера 31 через второй дешифратор 32 подключен к входной информационной шине запоминающего устройства 2. Дешифратор 31 преобразует многоразрядное число на своем входе в одиночный импульс.

Нулевой выход триггера 31 через ключ 33, а единичный вход триггера 31 через ключ 34 подключены соответственно к управляющим записывающему и читающему входам блока 35 памяти. Разрешающие входы ключей 33 и 34 соединены с выходом генератора тактовых импульсов 24, Сигнал на управляющем, записывающем входе обеспечивает только запись информации в блок 35, а сигнал на управляющем, читающем входе - только чтение информации на блоке 35. При этом адрес записи (или чтения) поступает на адресный вход блока 35 с выхода счетчика адреса 23. Информационный вход блока 35 подключен к информационному входу устройства. Эта же шина через первый вход блока ИЛИ 36 соединена с выходом запоминающего устройства 2. При этом второй вход блока элементов ИЛИ 36 подключен к выходу блока 35.

Запоминающее устройство 4 (фиг. 3) так же, как и запоминающее устройство 2 выполняет две операции - запись и чтение К чисел. При этом отличие устройства 4 от

устройства 2 состоит в том, что в устройстве 2 необходимо хранить некоторое количество реализаций случайного К- мерного процесса или поля, а в устройстве 4 - только одну реализацию. Поэтому принципы рабо0 ты устройств 2 и 4 одинаковы и отличие состоит лишь в способе задания адресов и конца записи (чтения) К случайных чисел, образующих реализацию генерируемого случайного процесса или поля,

5 В запоминающем устройстве 4 счетный вход счетчика адреса 37 соединен с выходом генератора тактовых импульсов 38. Управляющий вход генератора тактовых импульсов 38 подключен к единичному (пря0 мому) выходу триггера 39, единичный (прямой) вход которого через элемент задержки 40 соединен с выходом элемента ИЛИ 41.

Элемент ИЛИ 41 подключен входами к первой и второй управляющим шинам уст5 ройства 4, а выход элемента ИЛИ 41 кроме элемента задержки 40) соединен с установленным в начальный адрес входом счетчика адреса 37.

Адресный выход счетчик адреса 37 сое0 динен с первым входом блока 42 сравнения, второй вход которой подключен к регистру памяти 43, хранящему адрес хранения последнего числа в устройстве 4. Выход блока сравнения 42, сигнал на котором появляет5 ся в случае совпадения адресов на входах этого блока 42, сравнения, подключен к нулевому (инверсному) входу триггера 39.

Первая управляющая входная шина запоминающего устройства 4, подключенная

0 к выходу дешифратора 3 устройства, соединена с нулевым (инверсным) входом триггера 44. Вторая управляющая входная шина устройства 4, подключенная к выходу блока 7 сравнения устройства, соединена с еди5 ничными (прямым) входом триггера 44 . Нулевой (инверсный) выход триггера 44 и прямой (единичный) выход триггера 44 соединены с первыми входами соответственно ключей 45 и 46. Вторые входы ключей 45

0 и 46 соединены с выходом генератора тактовых импульсов 38. Выходы ключей 45 и 46 подключены к управляющему, соответственно записывающему и считывающему входу блока 47. Адресный вход блока 47

5 подключен к выходу счетчика адреса 37.

Информационный вход запоминающего устройства 4 через информационную входную шину устройства 4 подключен к выходу устройства 2 всего генератора случайных процессов и полей, а выход блока 47

через информационную выходную шину устройства 4 соединен с информационным входом ключа б (фиг. 1).

Генератор многомерных случайных процессов работает следующим образом.

В исходном положении счетчик 1 установлен в исходное (нулевое) состояние. В регистре памяти 19 зафиксировано целое число, определяющее объем ограниченной совокупности исходных реализаций случайного многомерного процесса или поля, ко- торйя обеспечивает подбор ближайщей по разности суммы реализации процесса (поля) к последней прогенерированной реализации. Содержимое регистра памяти 19 является параметром генератора, управляющим величиной корреляции, Запоминающее устройство 2 содержит независимые реализации случайного процесса (попя). Счетчики 9 и 10 содержат сумму компонентов реализации многомерного процесса (поля). Реализации процесса (поля) имеют требуемый закон распределения вероятностей, задаваемый датчиком случайных некоррелированных чисел 15. На выходе блэка 7 сравнения сигнал отсутствует, следовательно ключ 8 заперт и на входы счетчиков 9 и 10 сумма компонентов реализации с выхода сумматора 5 не подается. По этой же причине заперт ключ 6 и сигнала на считывающем входе запоминающего устройства 4 нет, что приводит к отсутствию чисел на выходе устройства. На выходе блока 11 сравнения сигнал также отсутствует.

Импульсы от генератора тактовых импульсов блока 21 управления передаются на установленный в нуль вход сумматора 5, через элемент задержки 20 - на счетный вход счетчика 1 и на разрешающий вход ключа 11. В счетчике 1 устанавливается очередное значение адреса устройства 2, которое поступает, во-первых, на адресный вход устройства 2; во-вторых, через дешифратор 3, преобразующий адрес в сигнал, на записывающий вход запоминающего устройства 4; в-третьих, адрес из счетчикз 1 поступает на вход блока 18 сравнения. Сигнал на выходе блока 18 сравнения появляется только в том случае, если адрес в счетчике 2 достиг максимального значения, определяемого содержимым регистра памяти 19. Число, записанное в регистре 19, предназначено для управления величиной корреляционной зависимости между реализациями многомерного случайного процесса иг- чя. С его увеличением значения корреляш/.ооных моментов возрастают, так как введение корреляции осуществляется путем подбора из набора реализаций, хранящихся в устройства 2, к ранее прогенерированной реализации по правилу минимизации модуля разности между суммой компонентов ранее прогенерированной последней реализации и выбираемой из устройства 2 реализации.

Чем больше сравнивается различных реализаций, тем больше возможностей для подбора ближайшей по сумме компонентов реализации в сравнении с последней прогенерированной реализацией, а следовательно, существенно больше величина корреляции. Поэтому в регистре 19 может быть записано любое число, в том числек и большее, чем количество реализаций, которое способно хранить устройство 2. Появление сигнала на выходе блока 18 сравнения аналогично по влиянию на работу генератора появлению сигнала на выходе по переполнению счетчика 1. Оба эти сигнала поступают на входы элемента ИЛИ 22, выход которого соединен с блоком 21 управления, В соответствии с адресом, записанным в счетчике 1, на выходе устройства 2 появится К чисел, которые передаются на вход сумматора 5 и на вход устройства 4, где и

хранятся до поступления сигнала на считывающем входе, После суммирования в сумматоре 5 компонентов реализации эта сумма поступает на информационный вход ключа 8 и на первый информационный вход

блока 7 сравнения.

На второй информационный вход блока сравнения 7 через ключ 11 и блок элементов ИЛИ 13 поступает число, записанное ранее в счетчике 9. На выходе блока 7 сравнения

появится сигнал, если сравнение произошло; в противном случае сигнал не вырабаты- вается. Следовательно, компоненты реализации процесса или поля, записанные в устройстве 4, на выход генератора не поступают, Из-за отсутствия сигнала на выходе блока сравнения 7, ключ 8 также заперт и сумма с выхода сумматора 5 не поступает на установочные входы счетчиков 9 и 10. Генератор будет работать аналогичным образом до тех пор, пока не появится сигнал сравнения на выходе блока сравнения, либо не произойдет переполнения счетчика 1, либо сравнения в блоке сравнения 18.

Пусть произошло переполнение счетчика 1 (или сравнение в схеме сравнения 18), то есть, осуществилось последовательное сравнение с тем количеством реализаций процесса или поля, которое задано содержимым регистра памяти 19). Счетчик 1 через элемент ИЛИ 17 переводится в исходное положение. На выходе по переполнению счетчика 1 или на оыходе блока 18 сравнения появляется сигнал который поступает в блок 21 управления.

Очередной импульс от блока 21 управления передается на счетный вход счетчика 10, уменьшая его содержимое на единицу.

Затем сумматор 5 сбрасывается в нулевое состояние и тот же сигнал, прошедший через элемент задержки 20, поступает на счетный вход счетчика 1, после чего сигнал передается на управляющий вход ключа 12. Появление нового адреса на выходе счетчика 1 вызывает see ранее записанные операции, то есть, на выходе запоминающего устройства 2 появляются К компонентов реализации, которые с помощью дешифратора 3 записываются в устройство 4. Эти же К чисел сумматором 5 суммируются и сумма подается на информационный вход ключа 8 и вход блока сравнения, Если на выходе блока сравнения 18 или выходе по переполнению счетчика 1 появляются сигналы, то действия по ним описаны и наличие хотя бы одного из этих сигналов означает окончание такта генерирования Если же этих сигналов нет, то на второй вход блока сравнения 7 через ключ 12 и блок элементов ИЛИ 13 поступает содержимое счетчика 10, В случае совпадения чисел, поступивших на входы блока 7 сранения, на его выходе появится сигнал. В противном случае генератор повторит цикл сравнения путем генерации нового импульса с выхода блока 21 управления,

Если сравнения всех заданных содержимых регистра памяти 19 или объемом устройства 2 сумм компонентов реализаций случайного процесса или поля с содержимым счетчика 10 не произойдет, то на выходе по переполнению счетчика 1 или на выходе блока 18 сравнения появится сигнал, запускающий блок 21,

Очередной импульс блока управления передается на счетный вход счетчика 9, увеличивая его содержимое на единицу. Далее работа генератора продолжается по описанной схеме до тех пор, пока не произойдет сравнения числа на выходе сумматора 5 с содержимым одного из счетчиков 9 или 10.

Если на выходе блока сравнения 7 появится сигнал сравнения, то он открывает ключ 76 и инициирует считывание информации из устройства 4 для передачи его на выход генератора. Этот же сигнал с выхода блока 7 сравнения открывает ключ 8 и сумма с выхода сумматора 5 записывается в счетчики 9 и 10. Эта сумма компонентов реализации случайного многомерного протцесса или случайного поля наиболее близка к сумме компонентов последней прогенериро- ванной реализации случайного процесса или поля. И, наконец, это г же сигал с выхода элемента задержки 14 поступает на вход

датчика случайных некоррелированных чисел 15 и на вход элемента задержки 16. Датчик случайных некоррелированных чисел 15 вырабатывает реализацию многомерного случайного процесса или поля, которая записывается на место реализации, поступившей на выход генератора, так как значение адреса в счетчике 1 не изменилось С выхода элемента задержки 16 сигнал

0 передается через элемент ИЛИ 17 на установочный вход счетчика 1 и устанавливает его в исходное состояние, соответствующее начальному адресу устройства 2. Этим генератор переводится, в исходное состояние и

5 такт работы генератора многомерных случайных процессов и полей заканчивается.

При работе устройства 2, как и других блоков и всего генераторта в целом, будем исходить из того, что К чисел, образующих

0 очередную реализацию многомерного случайного процесса или поля, подаются по соответствующим шинам последовательно. Перед началом записи или чтения информации триггер 23 находится в нулевом

5 состоянии, а триггер 31 - в единичном, что всегда обеспечивается выходным сигналом схемы сравнения 30.

При чтении 4 чисел блока 35 по адресной входной шине устройства 2 подается

0 адрес записи первого числа, а на информационной входной шине информация отсутствует. Адрес поступает на вход комбинационного сумматора 38, где, используя содержимое регистра памяти 39

5 (размерность генерируемого процесса), вычисляется конечный адрес, по которому хранится последнее (К-е) число реализации многомерного случайного процесса или случайного поля. Вычисленный (конечный) ад0 рее поступает на вход блока 40 сравнения. Начальный адрес с входной адресной шины устройства 2 записывается через установочный вход в счетчик адреса 23. Этот же адрес, преобразованный в единичный импульс де5 шифратором 27, пройдя через элемент задержки 26, поступает на единичный вход триггера 25 и переводит его в единичное состояние. Сигнал на единичном выходе триггера 25 запускает генератор тактовых

0 импульсов 24, частота импульсов на выходе которого существенно выше частоты импульсов на выходе блока 21 управления.

Сигнал с выхода генератора тактовых импульсов 24 поступает на разрешающие

5 входы ключей 33 и 34 и так как триггер 33 находится в единичном состоянии, то ключ 33 остается закрытым, а ключ 34 открывается и сигнал на его выходе поступает на считывающий вход блока 35. Так как счетчик 23 посредством генератора тактовых импульсов 24 будет последовательно устанавливаться в состояния, соответствующие адресу первого числа из реализации многомерного случайного процесса, адресу второго числа и так далее, а эти адреса поступают также на адресный вход блока 35, то на его выходе и выходе устройства 2 будут получены К чисел, являющихся реализацией многомерного случайного процесса, хранящейся в блока 35, начиная с заданного адреса.

Окончание чтения обуславливается совпадением адресов на входах блока 30 сравнения и выработкой соответствующего сигнала на его выходе. По этому сигналу триггер 35 переводится в нулевое состояние.

Запись информации в блок 35 производится аналогично с той разницей, что появление информации на входной шине запоминающего устройства 2 приводит, во- первых, к ее передаче через блок элементов ИЛИ 34 на входную шину устройства 2; во- вторых, после преобразования в этой ин- фоомации дешифратором 32 в единичный HN .улье он переводит триггер 31 в нулевое состояние, что обеспечивает открытие ключа 33 и закрытие ключа 34 (т.е., сигнал поступает на записывающий вход запоминающего устройства 35, и в - третьих, к подаче этой информации на информационный вход блока 35, Определение адреса записи последнего числа, вычисление и подача адресов на адресный вход блока 35, запуск и останов генератора тактовых импульсов 24 осуществляются так же, как и при чтении информации.

В запоминающем устройстве 4 перед началом выполнения записи или чтения информации счетчик адреса 37 установлен в состояние, соответствующее начальному адресу блока 47, а первый триггер 39 -К в нулевое состояние.

Операция записи К чисел в устройстве 4 начинается с приходом сигнала на его управляющий вход от дешифратора 3. Этот сигнал переводит триггер 44 в нулевое состояние и с нулевого выхода триггера 34 сигнал поступает на управляющий вход ключа 45, Сигнал поступает также через элемент ИЛИ 41 на вход элемента задержки 40 и установленный в начальный адрес вход счетчика адреса 37. Сигнал с выхода элемента задержки 40 поступает на единичный вход триггера 39, с единичного (прямого) выхода которого сигнал запускает генератор тактовых импульсов 38, частота генерирования импульсов которого существенно выше частоты генерирования имп/льсов блока 21 управления. Импульсы на выходе

генератора тактовых импульсов 38 поступают на управляющий вход ключа 45, обеспечивая тем самым поступление импульса на записывающий вход блока 47, т.е. блок 47,

приводится в состояние, обеспечивающее запись в него К-чисел, поступающих с информационного входа устройства. При этом адреса на адресном входе блока 47 формируются счетчиком адреса 37. Формиров-ание адреса ведется до тех пор, пока он не совпадет с конечным адресом, хранящимся в регистре памяти 43, и блок сравнения 42 не воспроизведет сигнал на своем выходе, По сигналу на выходе блока сравнения 42

триггера 37 переводится в нулевое состояние, и генератор тактовых импульсов 33 прекращает генерацию импульсов Операция записи К чисел в устройство 4 закончена,

Операция чтения К чисел из устройства 4 осуществляется аналогично операции записи, с той лишь разницей, что начальный сигнал поступает на вход элемента ИЛИ 41 через единичный вход триггера 44, устзновив его в единичное состояние, поступает на управляющий вход ключа 46, обеспечивая тем гамым поступление сигнала на читающий вход блока 47.

Таким образом блок 47 приводится в

состояние, обеспечивающее чтение из него К чисел, образующих реализацию генерируемого многомерного случайного процесса или случайного поля на выходе запоминающего устройства ц. При этом порядок запуска блока, формирование адресов и останов генератора тактовых импульсов 38 остаются такими же, как и при выполнении операции записи.

Формула изобретения

Генератор многомерных случайных процессов, содержащий первый блок памяти, три датчика, первый блок сравнения, три ключа, два элемента задержки, первый блок

элементов ИЛИ, блок управления и датчик случайных чисел, выхода которого соединен с информационным входом первого блока памяти, выход Равно первого блока сравнения подключен к входу задания режима

блока управления, к входу первого элемента задержки и через второй элемент задержки - к входу запуска датчика случайных чисел, первый и второй входы блока управления соединены с управляющими входами первого л второго ключей, выходы которых подключены к входам первого блока элементов ИЛИ, выход которого соединен с первым входом первого блока сравнения, выхода третьего ключа подключен к информационным входам первого и второго счетчиков,

выходы которых соединены с информационными входами одноименных ключей, а счетные входы подключены соответственно к третьему и четвертому выходам блока управления, отличающийся тем, что, с целью расширения функциональных возможностей за счет формирования корреляционной зависимости между реализациями многомерного случайного процесса, в него введены второй блок памяти, два генератора тактовых импульсов, четыре триггера, три дешифратора, три блока сравнения, два счетчика, пять ключей, три элемента задержки, три регистра памяти, второй блок элементов ИЛИ, три элемента ИЛИ, сумматор и накапливающий сумматор, выход которого соединен с вторым входом первого блока сравнения, выход Равно которого подключен к управляющим входам третьего и четвертого ключей, к первому входу первого элемента ИЛИ и к единичному входу первого триггера, прямой и инверсный выходы которого подключены к управляющим входам пятого и шестого ключей, выходы которых соединены соответственно с входами управления записью и считыванием второго блока памяти, выход которого соединен с информационным входом четвертого ключа, выход которого является выходом генератора, выход датчика случайных чисел подключен к входу первого дешифратора и к первому входу второго блока элементов ИЛИ, второй вход которого соединен с выходом первого блока памяти, а выход подключен к информационному входу второго блока и к информационному входу накапливающего сумматора, выход соединен с вторым входом первого блока сравнения и с информационным входом третьего ключа, тактовый вход которого подключен к пятому выходу блока управления, соединенному через третий элемент задержки со счетным входом третьего счетчика, выход которого подключен к входам второго и третьего дешифраторов, к информационному входу четвертого счетчика и к первому входу сумматора, второй вход которого соединен с выходом первого регистра памяти, а выход подключен к первому входу второго блока

сравнения, второй вход которого соединен с выходом четвертого счетчика, подключенным к адресному входу первого блока памяти, выход Равно второго блока сравнения

соединен с S-входом второго триггера и с R входом третьего триггера, прямой выход которого подключен ко входу запуска первого генератора тактовых импуйьсов; выход которого подключен к счетному входу четвертого счетчика и к информационным входам седьмого и восьмого ключей, выходы которых соединены соответственно с входами управления записью и считыванием первого блока памяти, выход первого

дешифратора подключен к R-входу второго триггера, инверсный и прямой выходы которого соединены соответственно с управляющими входами седьмого и восьмого ключей, выход третьего дешифратора через

четвертый элемент задержки соединен с S- входом третьего триггера, выход второго дешифратора подключен к нулевому входу первого триггера и к второму входу первого элемента ИЛИ, выход которого соединен с

установочным входом пятого счетчика и через пятый элемент задержки - с S-входом четвертого триггера, прямой выход которого подключен к входу запуска второго генератора тактовых импульсов, выход которого

соединен со счетным входом пятого счетчика и с информационными входами пятого и шестого ключей, выход пятого счетчика подключен к информационному входу второго блока памяти и к первому входу третьего

блока сравнения, второй вход которого соединен с выходом второго регистра памяти, а выход Равно подключен к R-входу четвертого триггера, первый и второй входы четвертого блока сравнения соединены соответственно с выходами третьего регистра памяти и третьего счетчика, а выход Равно подключен к первым входам второго и третьего элементов ИЛИ, второй вход которого соединен с выход ом второго элемента

задержки, а выход-с установочным входом третьего счетчика, выход переполнения которого подключен к второму входу второго элемента ИЛИ, выход которого соединен с входом запуска, блока управления.

15

л

15

-&

т

ьдддЛлмш

2

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1983 |

|

SU1111159A1 |

| Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике | 1989 |

|

SU1667092A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Устройство для определения изменения свойств случайных процессов | 1983 |

|

SU1205154A1 |

| Устройство для классификации нестационарных случайных процессов | 1987 |

|

SU1462358A1 |

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1778761A1 |

| Генератор многомерных случайных величин | 1984 |

|

SU1238068A1 |

| Генератор последовательностей случайных чисел | 1990 |

|

SU1836680A3 |

| Генератор последовательностей случайных чисел | 1986 |

|

SU1327102A1 |

| Генератор последовательностей случайных чисел | 1984 |

|

SU1179325A1 |

Изобретение относится к вычислительной технике и может быть использовано для моделирования случайных величин, процессов и полей Цель изобретения - расширение функциональных возможностей за счет формирования корреляционной зависимости между реализациями многомерного случайного процесса. Генератор содержит регистр памяти, счетчики, запоминающие устройства, ключи, дешифратор, накапливающий сумматор, датчик случайных чисел, блоки сравнения, блок элементов ИЛИ, элементы ИЛИ, элементы задержки и блок управления. 3 ил.

17

J

22

21

22

-Ј

Фиг.1

31

г:

33

J4

35

3L

4 8

13

11

12

/7

28

26

ДА

I

г

24

ЈJ

#W f

Редактор И.Касарда

Техред М.Моргентал

Заказ 2894ТиражПодписное

ВНИИПИ Государствен него комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская нзб , 4/5

фиг. 3

Корректор Л.Лукам

| Генератор многомерных случайных величин | 1986 |

|

SU1335992A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1179328A1 |

Авторы

Даты

1992-08-15—Публикация

1990-01-10—Подача