Изобретение может быть иснользовано в дискретных устройствах автоматики и вычислительной техники.

Известны схемы двоичных параллельных йакаН.Чивающих сумматоров потенциального Типа, построенных на булевых элементах «И, «ИЛИ, «НЕ, состоящие из регистра суммы, где хранится также одно из слагаемых в начале суммирования, регистра второго слагаемого и цепи переноса. Реги-стр суммы состоит из триггеров-счетчиков с входными клапанами (вентиля.ми), регистр второго слагаемого представляет собой обычный запоминающий регистр, а цепь переноса - комбинационную схему из элементов «И, «ИЛИ, «НЕ.

Недостаток известных схем наканливающих сумматров заключается в том, что они требуют больщого количества оборудования, вследствие чего имеют высокую стоимость, низкое быстродействие надежность. Кроме того, в этих схемах используются элементы задержки, которые малонадежны и нетехнологичны с точки зрения микроэлектроники.

С целью упрощения снижения стоимости и повышения надежности в предлагаемом сумматоре применены формальные нейроны и пороговые элементы вместо обычных булевых элементов. «И, «ИЛИ, «НЕ. Нрп этом в нем счетный вход каждого разряда регистра суммы, состоящего из двух индентичных формальных нейронов подключен к инверсному выходу порогового элемента с порогом - 1, имеющего три входа с весалш -1, -1 и -2, один из входов Которого с весом - 1 подключе 1 к единично.гу выходу триггера регистра второго слагаемого, второй вход с весом - I подключен к управляющей щине приема информации в регистр сумм, а вход с весом -2 подключен к выходу элемента переноса предыдущего разряда. Единичный выход первого формального нейрона каждого разряда регистра суммы подключен к одному из в.ходов порогового элеме 1та цепи переноса с порогом +3, имеющего четыре идентичных входа

с весами -f 1, второй вход подключен к единично.му выходу триггера регистра второго слагаемого, третий вход подключен к выходу элемента переноса предыдущего разряда, четвертый - к управляющей шине разрещения

переноса. Формальный нейрон (ФН) представляет собой обычный пороговый элемент (ИЭ) с встроенными булевымп элементами «И, «ИЛИ, «НЕ на входе. В данной схеме используются ФН с входны.ми элементами

«ИЛИ, а также обычные ИЭ.

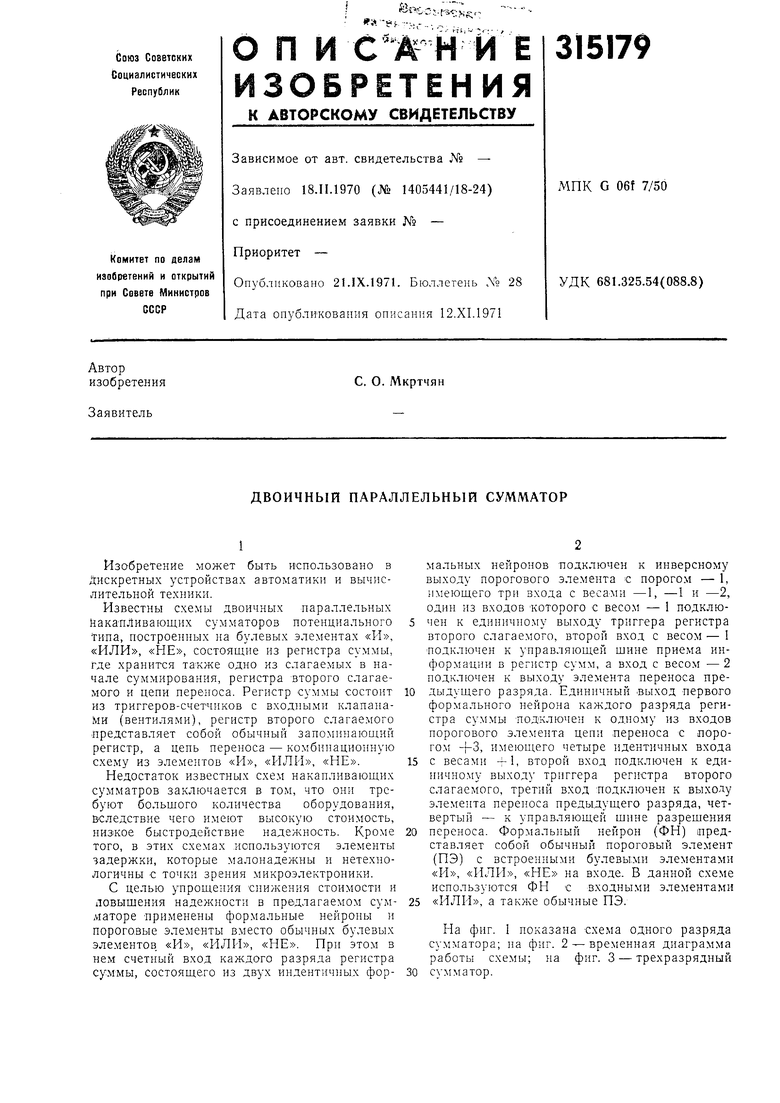

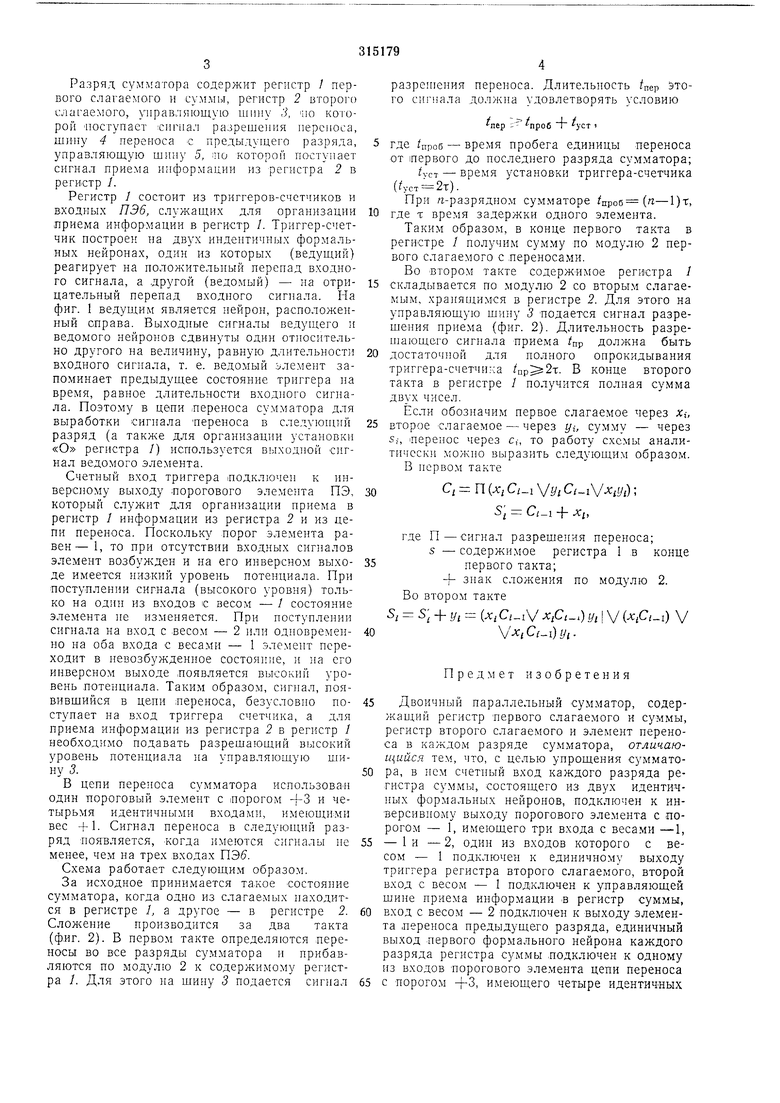

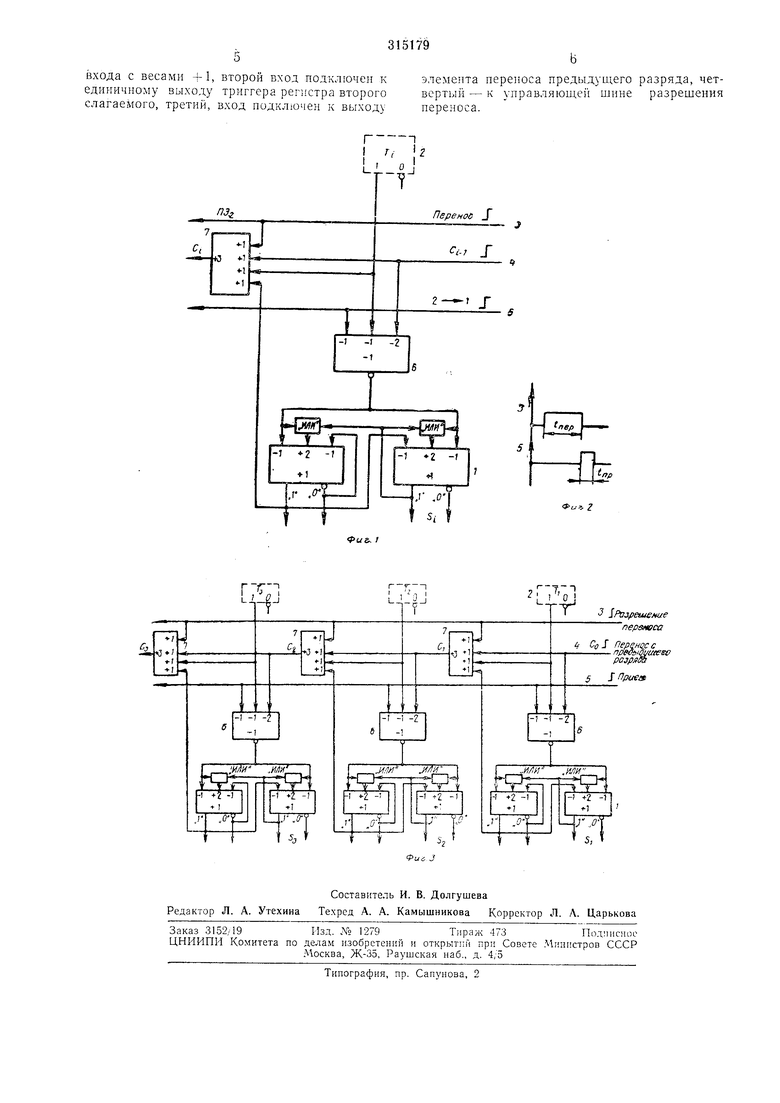

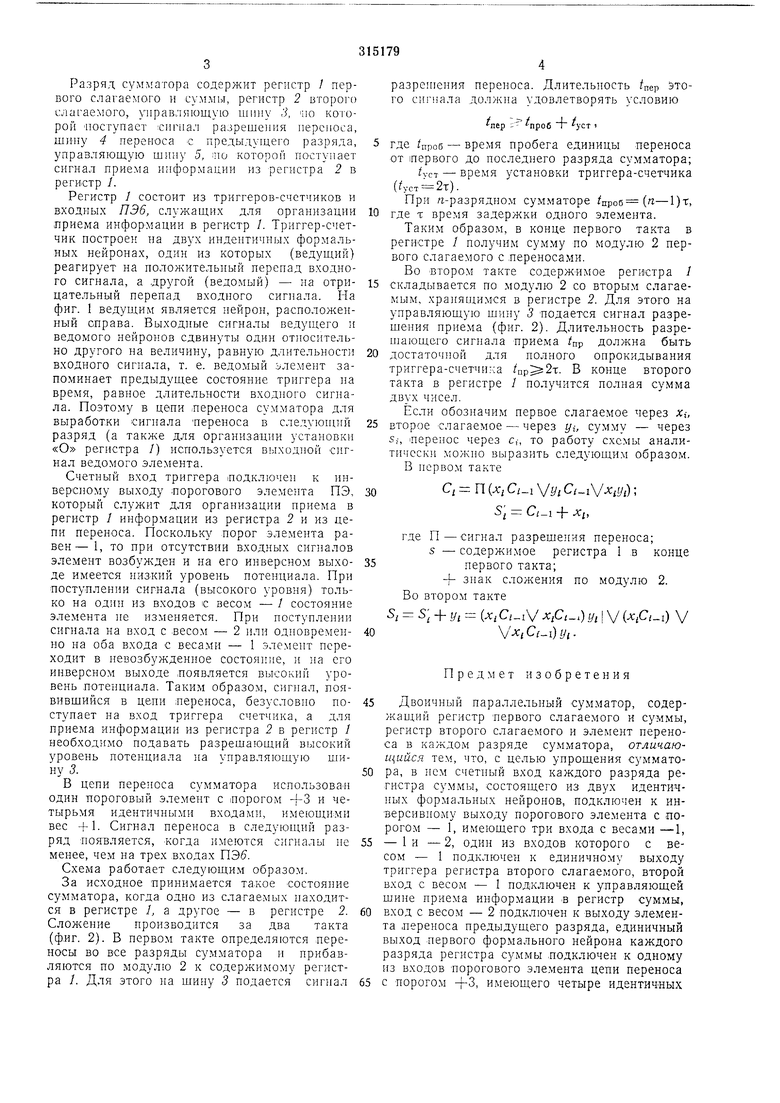

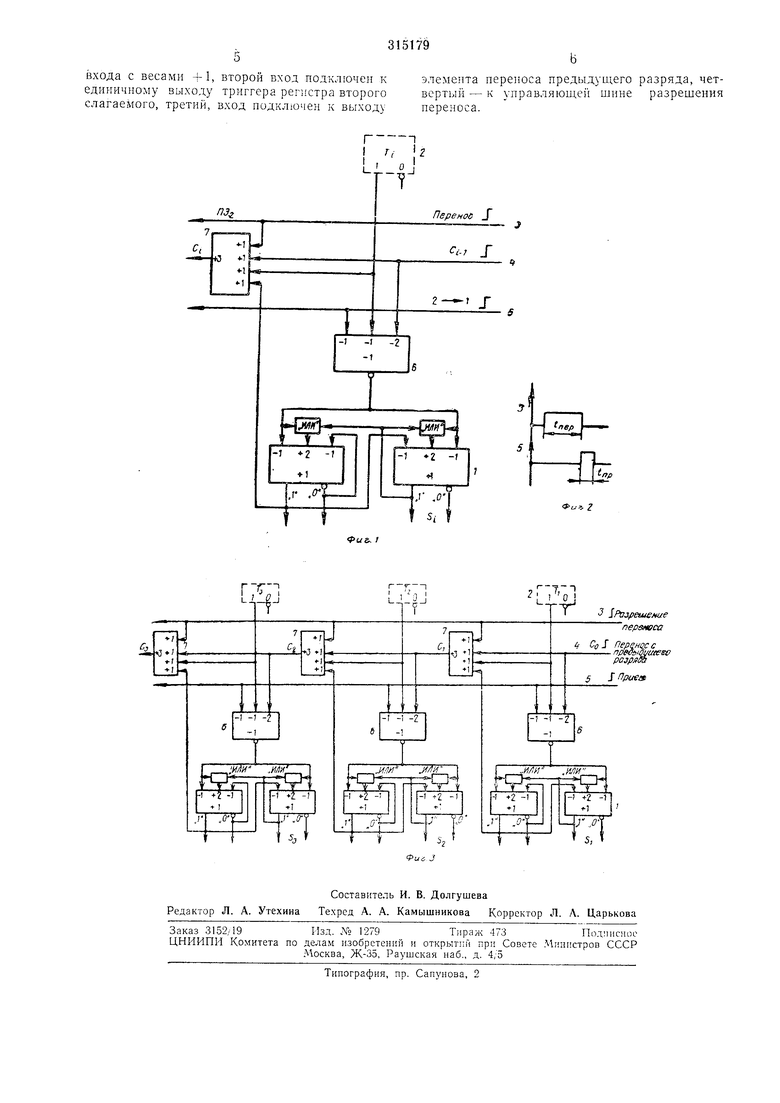

На фиг. 1 показана схема одного разряда сумматора; на фиг. 2 - временная диаграмма работы схемы; на фиг. 3 - трехразрядный сумматор.

Разряд cyм aтopa содержит регистр 1 первого слагаемого и суммы, регистр 2 второ1Ч) слагаемого, управляющую шипу 3, по которой Поступает спгпал разрептепия переноса, шППу 4 переноса с предыдуп1его разряда, управ.тяющую гпипу 5, по котороп поступает сигнал приема ппформацип из регистра 2 в регистр 1.

Регистр / состоит из триггеров-счетчиков и входных ПЭ6, служащих для оргапизации приема инфорМации в регистр /. Триггер-счетчик построен на двух иидептичиых формальных нейронах, один из которых (ведущий) реагирует на нолол ительный перепад входного сигнала, а другой (ведомый) - на отрицательный перепад входного сигнала. На фиг. 1 ведущим является нейрон, расположенный оправа. Выходные сигналы ведущего и ведомого нейронов сдвинуты один относительно другого на величину, равную длительности входного сигнала, т. е. ведомый ::/лемепт запоминает предыдущее состояние триггера на время, равное длительности входного сигнала. Поэтому в цепи .переноса сумматора для выработки сигнала переноса в следуюни1Й разряд (а также для организации установки «О регистра /) используется выходной сигнал ведомого элемента.

Счетный вход триггера подключен к инверспому выходу порогового элемента ПЭ, который служит для организации приема в регистр 1 информации из регистра 2 и из цепи переноса. Поскольку порог эле.мента равен- 1, то при отсутствии входных сигналов элемент возбужден и на его инверсном выходе имеется низкий уровень потенциала. При поступлении сигнала (высокого уровня) только на один из входов с весом - / состояние элемента не изменяется. При поступлении сигнала на вход с .весом - 2 или одновременно на оба входа с веса.ми - 1 элемент переходит в невозбужденное состояние, и iia его инверсном выходе появляется высокий уровень потенциала. Таким образом, сигнал, появивщийся в цепи переноса, безусловно поступает на вход триггера счетчика, а для приема информации из регистра 2 в регистр 1 необходимо подавать разрешающий высокий уровень потенциала на управляющую шину 3.

В цепи переноса сумматора использоваН один пороговый элемент с порогом +3 и четырьмя идентичными входами, имеюп и ми вес +1. Сигнал переноса в следующий разряд появляется, .когда имеются сигналы не менее, чем на трех входах ПЭ5.

Схема работает следующим образом.

За исходное принимается такое состояние сумматора, когда одно из слагае.мых находится в регистре /, а другое - в регистре 2. Сложение производится за два такта (ф.иг. 2). В первом такте определяются переносы во все разряды су.мматора и прибавляются по модулю 2 к содержимому регистра /. Для этого }ia шипу 3 подается сигнал

разрещепия переноса. Длительность fnep этого сигнала должна удовлетворять условию

пер ; проб Г уст i

где /проб - Время пробега единицы переноса

от первого до последнего разряда сумматора;

уст - время установки триггера-счетчика

(.).

При «-разрядном сумматоре /проб(«-1)т, где -с время задержки одного элемента.

Таким образом, в конце первого такта в регистре / получим сумму по модулю 2 первого слагаемого с переносами.

Во втором такте содержимое регистра 1 складывается по модулю 2 со вторым слагаемым, хранящимся в регистре 2. Для этого на управляющую шину 5 подается сигнал разрешения приема (фиг. 2). Длительность разреи ающего сигнала приема пр должна быть достаточной для полного опрокидывания триггера-счетчика . В конце второго такта в регистре / получится полная сумма двух чисел.

Если обозначим первое слагаемое через Xi,

второе слагаемое - через уг, сумму - через

S;, Перенос через с,-, то работу схемы аналитпчески можпо выразить следующим образом.

В псрво.м такте

Q П (Xi Jyi ,yi} S + Xi,

где П-сигнал разращения переноса;

S - содержимое регистра I в конце

первого такта; + знак сложения по модулю 2. Во втором такте

5, s; + У; (Xic,iV А-0 У1 V () V

jXiCi-i)tJi.

Предмет изобретения

Двоичный параллельный сумматор, содержап,ий ретистр первого слагаемого и суммы, регистр второго слагаемого и элемент переноса в каждом разряде сумматора, отличающийся тем, что, с целью упрощения сумматора, в нем счетный вход каждого разряда регистра суммы, состоящего из двух идентичных формальных нейронов, подключен к инверсивному выходу порогового элемента с порогом - 1, имеющего три входа с весами -1,

- 1 и - 2, один из входов которого с весом - I подключен к единичному выходу триггера регистра второго слагаемого, второй вход с весо.м - 1 подключен к управляющей шине приема информации в регистр суммы,

вход с весом - 2 подключен к выходу элемента переноса предыдущего разряда, единичный выход первого формального нейрона каждого разряда регистра суммы подключен к одному из входов порогового элемента цепи переноса входа с весами +1, второй вход подключен к единичному выходу триггера второго слагаемого, третий, вход подкл10чен к выходу

-1 элемента переноса предыдущего разряда, четвертый - к управляющей щнне разрешения переноса.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ «3» | 1973 |

|

SU361460A1 |

| Устройство для моделирования нейрона | 1991 |

|

SU1831715A3 |

| Накапливающий сумматор по модулю 3 | 1972 |

|

SU448460A1 |

| ЕСОЮЗН.АЦ I пдт1:нш-1шр - кд1| ВИБЛИо"ск^."""| | 1973 |

|

SU368600A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для моделирования нейрона | 1987 |

|

SU1479944A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

ГТЛ

р;

I-f-I

nepaivca

.JuWfflP

pajfM

Даты

1971-01-01—Публикация