Изобретение относится к элементам электронной вычислительной техники и может быть использовано при построении вычислительных машин, устройств автоматики и различных цифровых приборов, работающих в гс-значной логике.

Известны схемы динамических триггеров на феррит-транзисторных ячейках, в которых избыточность в кодировании информации используется для раснлиреиия логических возможностей, описываемых бинарной логикой.

Цель изобретения заключается в расширении логических возможностей динамических триггеров, работающих с фазоимпульсным кодированием информации, для использования их как элементов /с-значной логики.

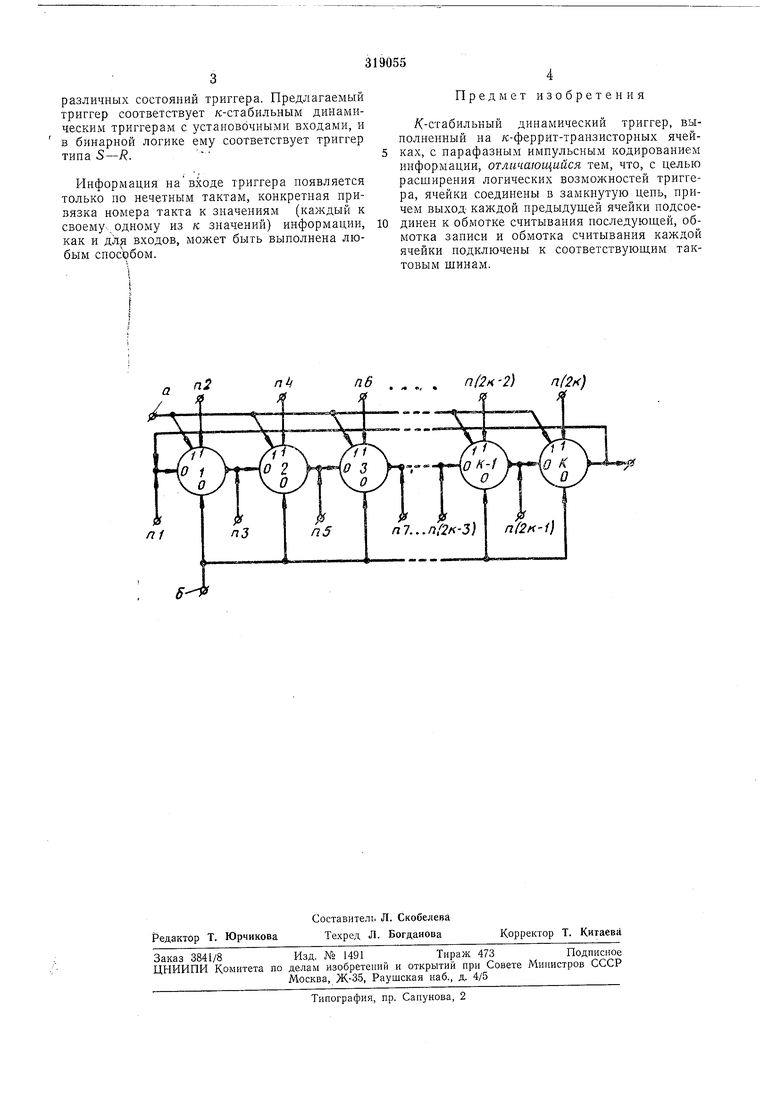

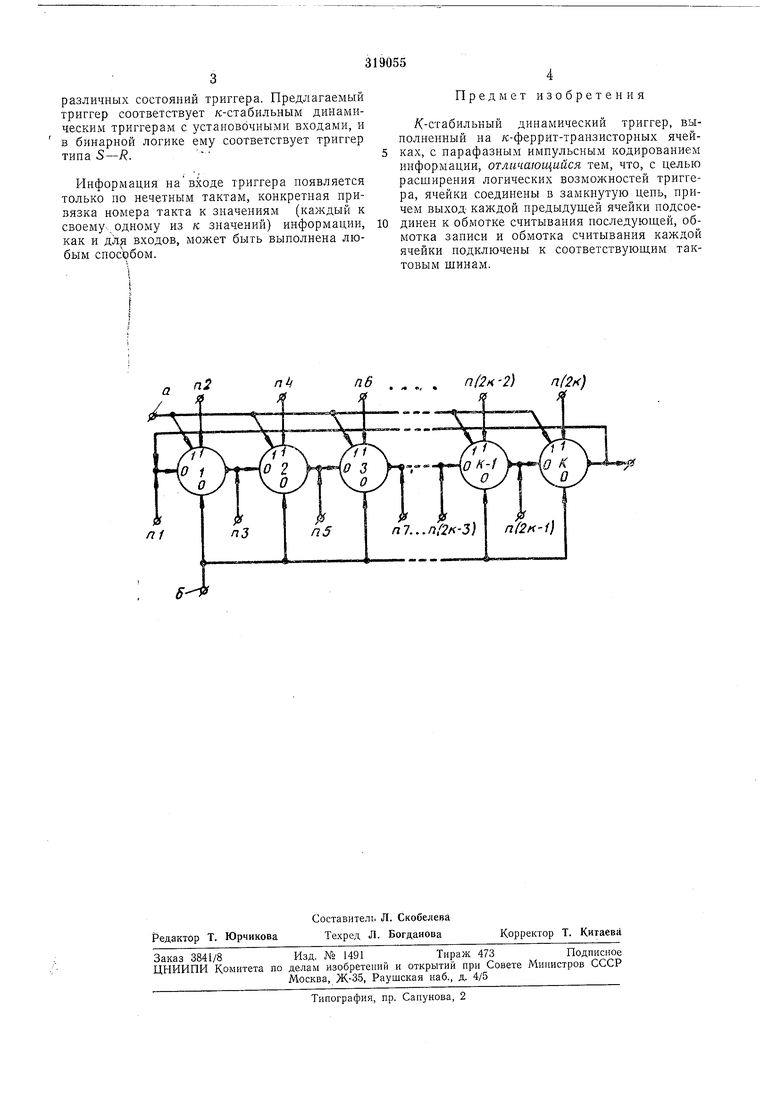

В предлагаемом /с-стабильном динамическом триггере на феррит-транзисторных ячейках это достигается путем построения замкнутой цепочки из ячеек, выход каждой из которых подан на обмотку считывания соответствующей следующей ячейки, и специальпым включением постоянщлх тактов. Номера последних увеличиваются в направлении считывания информации ячейками триггера.

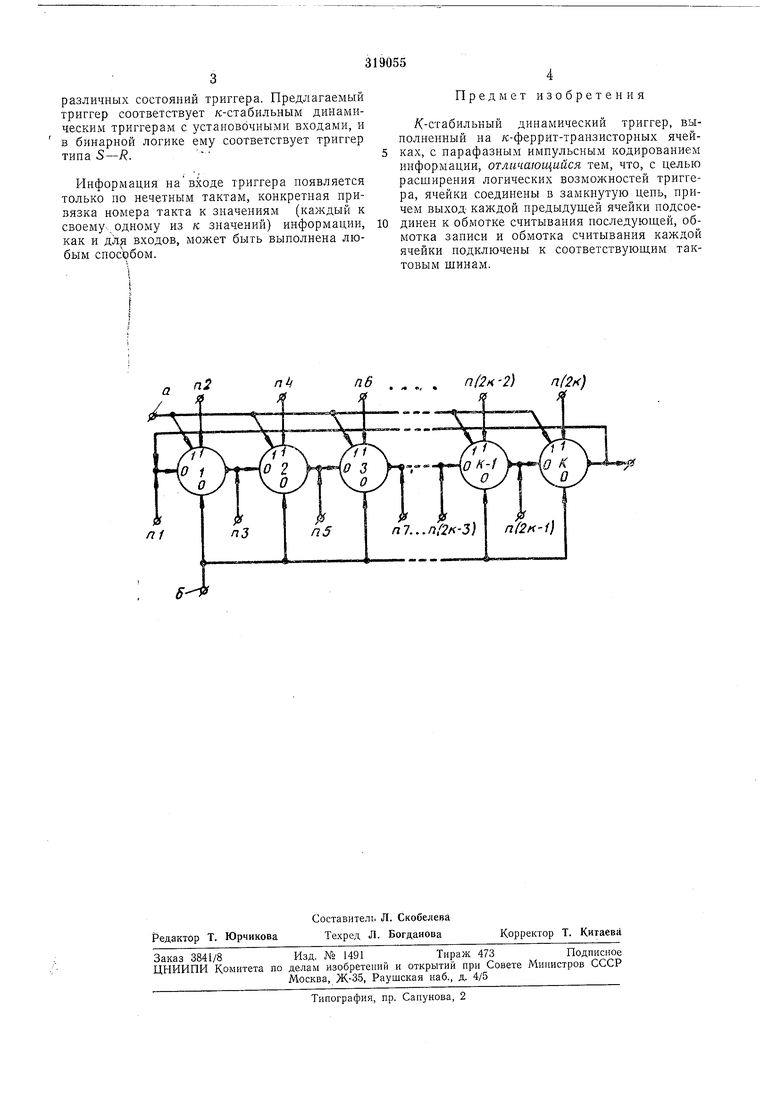

Схема /с-стабилыгого динамического триггера изображена на чертеже.

ет два входа а и б и один (как минимум) выход, например с ячейки к. Вход а подан на обмотки считывания, а вход б - на обмотки записи всех ячеек триггера. Выход каждой ячейки подсоединен к обмотке считывания следующей ячейки, причем выход последней ячейки к подключен к обмотке считывания первой ячейки и используется как выход триггера. В качестве выхода триггера может также использоваться выход любой из к-/ оставшихся ячеек (1, 2, 3,..., к-1). На ячейки подключены цостоянные такты п1, п2, пЗ,..., и (2к-У), номера которых по записи совпадают с удвоенным номером ячейки, а по считгз1вапию иа единицу меньше номера такта записи этой же ячейки.

Информация, поступающая на входы триггера, иредсгавляется в фазопмпульсном виде,

причем каждому из к зпачении соответствует наличие импульса тока в первом из пары своих рабочих тактов. В один цифровой период ла вход триггера подается лишь одно из к возможных значений (О, 1, 2, 3, ..., к-1),

при этом равенство каких-либо (всех) значений нулю соответствует отсутствию импульсов тока в паре соответствующих тактов. Отсюда следует, что количество постоянных тактов, необходимых для правильной работы трнггеразличных состояний триггера. Предлагаемый триггер соответствует к-стабильным динамическим триггерам с установочными входами, и в бинарной логике ему соответствует триггер типа S-R. Информация навходе триггера ноявляется только но нечетным тактам, конкретная нривязка номера такта к значениям (каждый к своему, одному из к значений) информации, как и для входов, может быть выполнена любым способом. 4 Предмет изобретения /С-стабильный динамический триггер, выполненный на ге-феррит-транзисторных ячейках, с парафазным импульсным кодированием информации, отличающийся тем, что, с целью расширения логических возможностей триггера, ячейки соединены в замкнутую цепь, причем выход- каждой предыдущей ячейки подсоединен к обмотке считывания последуюш,ей, обмотка записи и обмотка считывания каждой ячейки подключены к соответствующим тактовым шинам.

| название | год | авторы | номер документа |

|---|---|---|---|

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU268008A1 |

| РЕВЕРСИВНЫЙ ИНВЕРТИРУЮЩИЙ РЕГИСТР.ВОГООЮЗНАЯ^^^^•^•Ш1штт^''Б лис ТЕТКА | 1972 |

|

SU332578A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ К | 1972 |

|

SU341034A1 |

| РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1971 |

|

SU308517A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU272672A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 1967 |

|

SU197281A1 |

| БИБЛИОТЕЧКАА. Е. Бобров | 1971 |

|

SU320063A1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| УСТРОЙСТВО для АДРЕСОВАНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ ПОДЪЕМНО-ТРАНСПОРТНЫХ И ШАХТНЫХ УСТАНОВОК | 1970 |

|

SU270348A1 |

п/2н -2) п(2к}

Авторы

Даты

1971-01-01—Публикация