Изобретение относится к о-бласти электронных цифровых -вычислительных машин, а И1менно к одноразрядным сумматорам .по модулю К, выполненным на магнитно-транзисторных элементах, и (.может .быть использовано в устройствах вычислительной техники, автоматики И приборостроения.

Известны одноразрядные сум-маторы ПО модулю К, содержащие К-стабильный динамический триГГар, двухтактный регистр сдвига и дешифратор.

Однако схема такого устройства сложна и имеет большое число элементов.

Цель изобретения - уменьшение количества элементов и повышение надежности устройства.

Это достигается яутем специального соединения выходов двухярусного дешифратора со входами записи двухтактного регистра сдвига, позволяющего преобразовывать фазовмпульсный код слагаемого .в унитарный код, и соединения выхода двухтактного регистра сдвига с К-стабильньга динамическим триггером и выхода этого триггера со входом регистра сдвига ;по считыванию, что позволяет получать значение суммы ,по модулю К, .как устойчивое состояние К-стабильного динамического триггера.

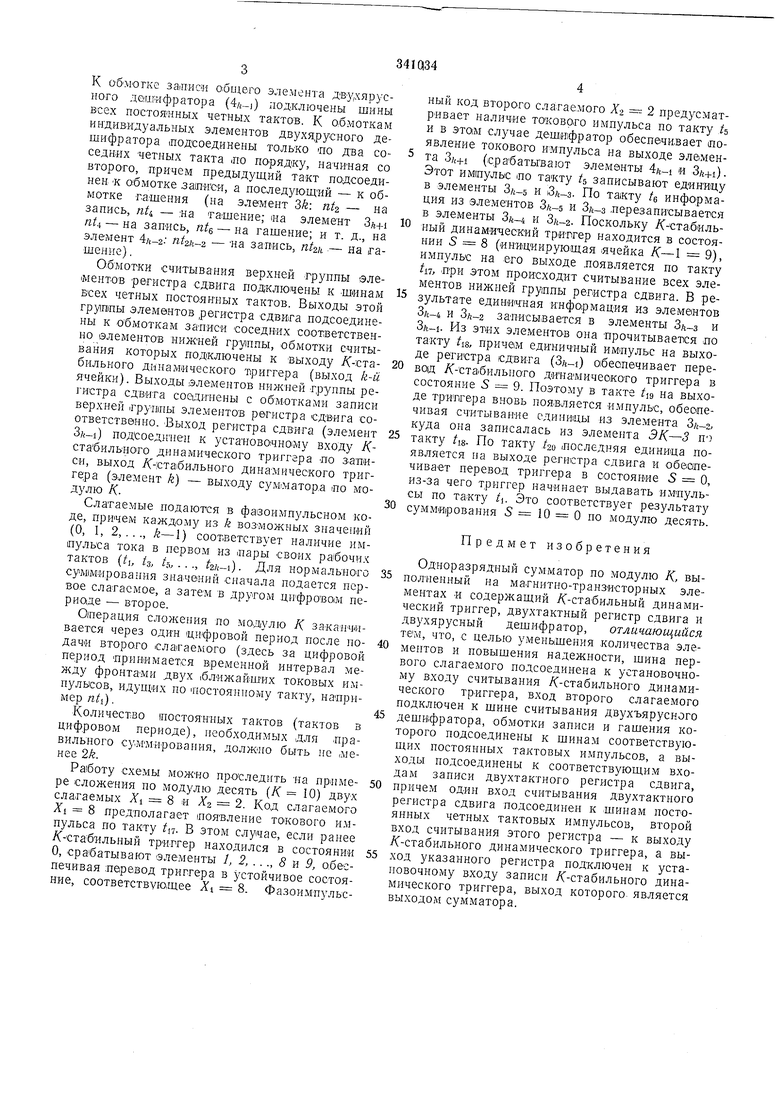

Сумматор содержит типовых ма гнитнотранзисторных элементов, из которых /е элементов 1, 2 .. ., fe,- 1 и k объединены в схеме /(-стабильного динаМйчеокого триггера,

элементов k , k + 2, /е + 3,. . ., и пре.дставляют собой двухтактный регистр сдвига и k элементов 3fe, 3k+i, , ..., и составляют схему двухярусного дешифратора, причем двухярусный дешифратор по выходу соединен со входами записи двухтактного регистра сдвига таким образом, что дешифратор и регистр работают как преобразователь значения фазоимпульсного кода второго слагаемого в соответствую щее число импульсов .последовательного унитарного кода. Сумматор имеет два входа Xj и Х и выход суммы S. Вход Xi первого слагаемого подсоединен к установочному входу но считыванию Я-стабильного динамического триггера (элементы 1, 2,..., k). Вход Х второго слагаемого подключен к обмоткам считывания двухЯрусного дешифратора (элементы 3k, 3k+i,..., и ), выходы которого подсоединены к обмоткам записи соответствую.щих элементов

двухтактного регистра сдвига, причем вторые концы обмоток записи этих элементов подключены .к началам обмоток записи (токовая сборка с соответствующим выходом двухярусного дешифратора) 1последую.щих элементов, на коК Обмогке залиси о:бщего элемента двудярусного деш-ифратора (4/i-j) подключены шины всех постоянных четных тактов. К 0 бмоткам индивидуальных элементов двухдрусного дешифратора лодсоединены только по два соседнйх четных такта ло порядку, начиная со второго, причем предыдущий такт подсоединен К обмотке записи, а последующий - к обмотке гашения (на элемент 3k: ntz - на запись, я/4 - :на ташение; «а элемент Зй+i - на запись, nt - на гашение; и т. д., па элемент . ntzh-z - на запись, ntzh - на гашение) .

Обмотки считывания верхней группы элементов регистра сдвига подключены к шинам всех четных ПОСТОЯНБЫХ тактов. Выходы этой гру1П1ПЫ элементов регистра сдвЕга подсоединены к обмоткам записи соседних соответственно елемептов нижней грунпы, обмотки считывания которых подключены к выходу /С-стабильного динамического т риггера (выход k-u ячейки). Выходы .-элементов нижней группы регистра сдвига соединены с обмотками записи верхней 1груи1пы элементов регистра сдвига соответственно. Выход регистра сдвига (элемент ) подсоединен к установо ЧН01Му входу Кстабильного динамического триггера ло з-аписи, выход /С-стабильного динамического триггера (элемент k) - выходу судмматор.а ло модулю К.

Слагаемые подаются в фазоимпульсном коде, причем каждому из /г возможных значений (О, 1, 2, ..., k-I) соответствует наличие импульса тока в первом из лары своих рабочих тактов (ti, /3, k, .. ., tzk-i). Для нормального сум1мироваг1ия значений сначала подается первое слагаемое, а затем в другом цифровоим периоде - второе.

Операция сложения по модулю К заканч ивается через один цифровой период после подачи второго слагаемого (здесь за цифровой период принимается временной интервал между фронтами двух |ближайших токовых импулысов, идущих по Постоянному такту, например n(i).

Количество постоянных тактов (тактов в цифровом периоде), необходимых для правильного суммировапия, должно быть не .менее 2k.

Ра1боту схемы можно проследить на примере сложения по модулю десять (К 10) двух слагаемых Xi 8 и Х 2. Код слагаемого Xi 8 предполагает появление токового импульса по такту /17. В этом случае, если ранее Я -стабильный триггер находился в состоянии О, срабатывают элементы 1, 2, . .., 8 и 9, обеспечивая .перевод триггера в -стойчивое состояние, соответствующее Xi 8. Фазоимпульсиый код второго слагаемого Х- -- 2 предусматривает наличие токового импульса по такту 4 и в этом случае дешифратор обеспечивает появление токового Импульса на выходе элемента 3/i+i (срабатывают элементы 4k-i и Зл+i). Этот импульс по такту 4 записывают единицу в элементы Зн-ь н йл-з. По такту /е информация из эле.ментов и ЗА-З перезаписывается в элементы Зй- и Зй-2. Поскольку /С-стабильный динамический тритгер находится в состоянии 5 8 (инициирующая ячейка 9), импульс на его выходе появляется по такту /17, при этом происходит считывание всех элементов нижней группы регистра сдвига. В результате единичная информация из элементов и Зл-2 записывается в элементы и . Из этих элементов она прочитывается по такту /18, приче1.м единичный импульс на выходе регистра сдвига () обеспечивает перевод /С-стабильного динамичеокого триггера в состояние 5 9. Поэтому в такте /ID на выходе трипгера вновь появляется импульс, обеспечивая считывание единицы из элемента Зл-г/ куда она записалась из элемента ЭК.-3 по

такту /18. По такту 4о последняя единица появляется па выходе регистра сдвига и обвапечивает перевод триггера в состояние 5 0, из-за чего триггер начинает выдавать импульсы по такту /ь Это соответствует результату

суммирования 5 10 О по модулю десять.

Предмет изобретения

Одноразрядный сумматор по модулю К, выполненный на магнитно-транзисторных элементах и содержащий /С-стабильный динамический триггер, двухтактный регистр сдвига и двухярусиый дешифратор, отличающийся тем, что, с целью уменьшения .количества элемептов и повышения надежности, шина первого слагаемого подсоединена к установочному входу считывания у -стабильного динамического триггера, вход второго слагаемого подключен к шине считывания двухъярусного

дешифратора, обмотки записи и гашения которого подсоединены к шина.м соответствующих постоянных тактовых импульсов, а выходы подсоединены к соответствующим входа.м записи двухтактного регистра сдвига,

причем один вход считывания двухтактного регистра сдвига подсоедипеп к шипам постоянных четных тактовых импульсов, второй вход считывания этого регистра - к выходу /С-стабильного динамического триггера, а выход указанного регистра подключен к устаповочному входу записи /С-стабильного динамического триггера, выход которого является выходом сумматора.

2,v.

X,.,-fit, 6 ntj fit2K-3

.,6 2A

| название | год | авторы | номер документа |

|---|---|---|---|

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| К-значный фазоимпульсатор сумматор | 1977 |

|

SU657435A1 |

| БИБЛИОТЕЧКАА. Е. Бобров | 1971 |

|

SU320063A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Дешифратор | 1978 |

|

SU809564A1 |

| 'ВСЕСОЮЗНАЯ __ПАТЕпт;:о- ._/;л;;ч:1С1гля , библиотека iVIbA | 1973 |

|

SU366583A1 |

| АНАЛИЗИРУЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU246156A1 |

Авторы

Даты

1972-01-01—Публикация