Изобретение может быть использовано в устройствах автоматики и вычислительной техники.

Известны универсальные логические элементы, содержащие два транзисторных инвертора, резисторы, коммутационные клеммы.

Предложенное устройство отличается от известных тем, что содержит конденсатор и транзисторный ключ, коллектор которого соединен с коллектором транзистора первого инвертора, с коммутационной клеммой и через резистор с базой транзистора второго инвертора, эмиттеры транзисторов инверторов объединены, подключены к общей шине питания через резистор и через конденсатор - к другой коммутационной клемме.

Это позволяет расширить функциональные возможности логического элемента.

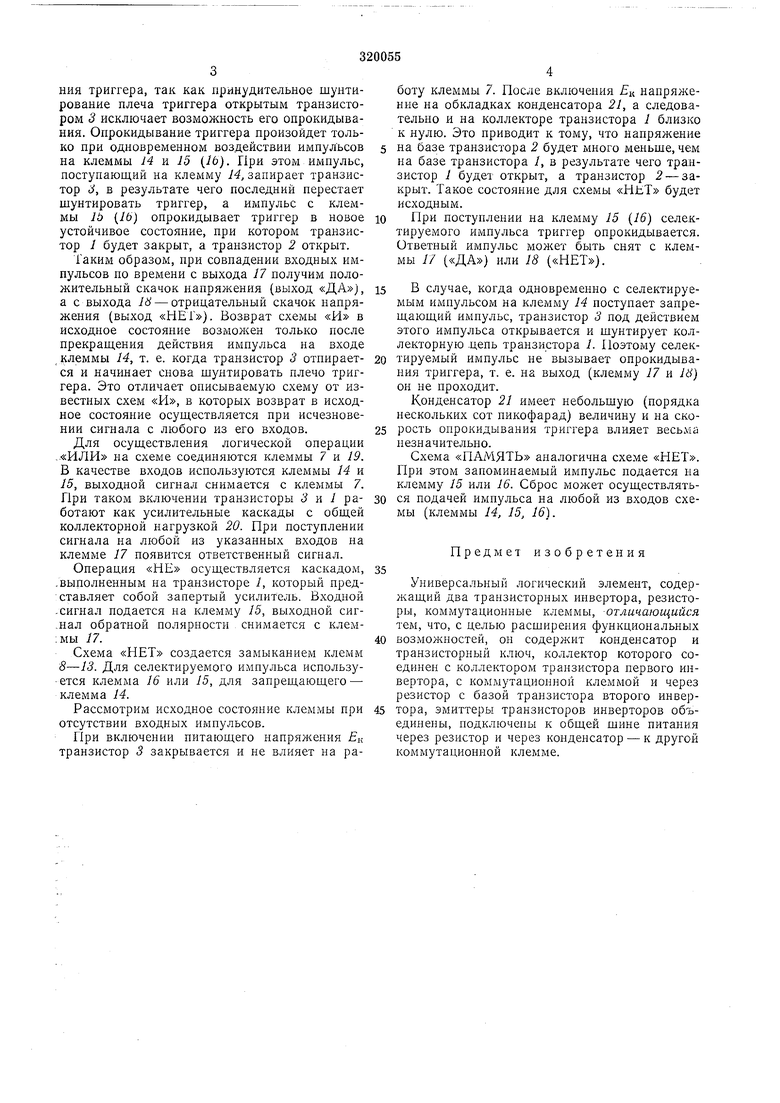

Иа чертеже изображена схема логического элемента.

Он содержит инверторы на транзисторах / и 2. К коллектору транзистора / подключен коллектор транзистора 5, необходимый режим которого обеспечивается резисторами 4, 5, 6. При замыкании коммутационных клемм 7 к 8 каскад находится в состоянии насыщения за счет смещения, ноступающего на его базу через резистор 4 от источника коллекторного напряжения к- При замыкании клемм 8, 9 каскад будет заперт за счет смещения, подаваемого в цепь эмиттера через резисторы 5, 6. Фиксация исходного состояния триггера, при котором транзистор 1 открыт, а транзистор 2 закрыт, осуществляется замыканием клемм 10, 11. Инверторы на транзисторах 1, 2 при замыКании клемм 12, 13 образуют асимметричный триггер с автоматическим смещением.

Логическое устройство при выполнении различных операций работает следующим обрам.

При выполнении логической операции «И (совпадение) соединяются коммутационные клеммы 7 и 5, /.2 и 13. Выходом для одного из сигналов служит клемма 14, для другого -15

или 16.

При включении напрял ения к транзнстор 3 оказывается открытым, вследствие чего он шунтирует коллекторную цепь транзистора / триггера. Напряжение на коллекторе транзистора / становится значительно меньше, чем на коллекторе транзистора 2. Это приводит к тому, что в схеме «И в исходном состоянии транзистор / всегда открыт, а транзистор 2 всегда закрыт. Появление импульса отрицательной полярности на клемме 14 не изменит исходного состояния триггера, так как это приведет только к запиранию транзистора 3, что равносильно отключению его от транзистора 1. Подача входного импульса только на клемму ния триггера, так как принудительное шунтирование плеча триггера открытым транзистором 3 исключает возможность его опрокидывания. Опрокидывание триггера произойдет только при одновременном воздействии импульсов на клеммы 14 и 15 (1Ь). При этом имнульс, поступающий на клемму 14, запирает транзистор 3, в результате чего последний перестает шунтировать триггер, а импульс с клеммы 1Ь (16) опрокидывает триггер в новое устойчивое состояние, при котором транзистор 1 будет закрыт, а транзистор 2 открыт. Гаким образом, при совпадении входных импульсов по времени с выхода 17 получим положительный скачок напряжения {выход «ДА), а с выхода 1 - отрицательный скачок напряжения (выход «НЕ Г). Возврат схемы «И в исходное состояние возможен только после нрекраш.ения действия импульса на входе клеммы 14, т. е. когда транзистор 3 отпирается и начинает снова шунтировать плечо триггера. Это отличает описываемую схему от известных схем «П, в которых возврат в исходное состояние осуществляется при исчезновении сигнала с любого из его входов. Для осуществления логической операции .-«ИЛИ па схеме соединяются клеммы 7 и 19. В качестве входов используются клеммы 14 и 15, выходной сигнал снимается с клеммы 7. При таком включении транзисторы 3 и 1 работают как усилительные каскады с обш,ей коллекторной нагрузкой 20. При поступлении сигнала на любой из указанных входов на клемме 17 появится ответственный сигнал. Операция «НЕ осуществляется каскадом, .выполненным на транзисторе /, который представляет собой запертый усилитель. Входной .сигнал подается на клемму 15, выходной сиг,нал обратной полярности снимается с клем; мы 17. Схема «НЕТ создается замыканием клемм 8-13. Для селектируемого импульса используется клемма 16 или 15, для запрещающего - клемма 14. Рассмотрим исходное состояние клеммы при отсутствии входных импульсов. При включении питающего напряжения к транзистор 3 закрывается и не влияет на работу клеммы 7. После включения « напряжение на обкладках конденсатора 21, а следовательно и на коллекторе транзистора 1 близко к нулю. Это приводит к тому, что напряжение на базе транзистора 2 будет много меньше, чем на базе транзистора /, в результате чего транзистор 1 будет открыт, а транзистор 2 - закрыт. Такое состояние для схемы «НЕТ будет исходным. При поступлении на клемму 15 (16) селектируемого импульса триггер опрокидывается. Ответный импульс быть снят с клеммы 17 («ДА) или 18 («НЕТ). В случае, когда одновременно с селектируемым импульсом на клемму 14 поступает запреш,аюш,ий импульс, транзистор 3 под действием этого импульса открывается и шунтирует коллекторную -цепь транзистора /. Поэтому селектируемый импульс не вызывает опрокидывания триггера, т. е. на выход (клемму 17 и Уй) он не проходит. Конденсатор 21 имеет небольшую (порядка нескольких сот пикофарад) величину и на скорость опрокидывания триггера влияет весьма незначительно. Схема «ПАМЯТЬ аналогична схеме «НЕТ. При этом запоминаемый импульс подается на клемму 15 или 16. Сброс может осуш,естБляться подачей импульса на любой из входов схемы (клеммы 14, 15, 16. Предмет изобретения Универсальный логический элемент, содержащий два транзисторных инвертора, резисторы, коммутационные клеммы, отличающийся тем, что, с целью расширения функциональных возможностей, он содерл ит конденсатор и транзисторный ключ, коллектор которого соединен с коллектором транзистора первого инвертора, с коммутационной клеммой и через резистор с базой транзистора второго инвертора, эмиттеры транзисторов инверторов объединены, подключены к обшей шине питания через резистор и через конденсатор - к другой коммутационной клемме.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| Ждущий генератор импульсов | 1980 |

|

SU894832A1 |

| УСТРОЙСТВО ТОКОВОЙ ЗАЩИТЫ ЭЛЕКТРОУСТАНОВКИ | 1993 |

|

RU2114496C1 |

| Мультивибратор | 1979 |

|

SU773913A1 |

| Многоканальный селектор импульсов по длительности | 1972 |

|

SU444313A1 |

| Система зажигания для двигателя внутреннего сгорания | 1991 |

|

SU1835462A1 |

| Частотно-фазовый детектор | 1980 |

|

SU921043A1 |

| Устройство для управления силовым транзисторным ключом | 1983 |

|

SU1127053A1 |

| Преобразователь постоянного напряжения | 1979 |

|

SU773609A1 |

| Импульсный стабилизатор напряжения | 1985 |

|

SU1325440A1 |

Даты

1971-01-01—Публикация