1

Изобретение относится к радиотехнике и может быть использовано в телеуправлении, телеизмерении и в устройствах автоматики.

Известны М|Ногоканальные селекторы импульсов по длительности, содержащие времязадающие цепи, формирующие каскады, логические схемы совпадения. Известны также времязадающие устройства, в которых используются диод-транзисторные ст|руктуры.

Однако известные многоканальные селекторы содержат реактивные элементы, что приводит к значительным трудностям .при реализации устройств в мик|роэлектронном исполнении, особенно для импульсов большой длительности (требуются конденсаторы и катушки индуктивности больших номиналов).

Кроме того, реализация селекторов в мйкроисполнении с .использованием тепловой связи между элементами без изменения существующей структурной схемы затруднительна, поскольку Постоянная времени теплопередающего элемента диод-транзисторной структуры при нагреве « охлаждении одина-.кова.

Целью изобретения является обеспечение распределения сигналов различной длительности по отдельным каналам.

Для этого в селекторе логические схемы выполнены на многоэмиттерных транзисторах, подсоединены первыми входами к выходу инвертора вторых сигналов, общего для iBcex каналов, а вторыми входами - к коллекторам транзисторов выходных инверторов соответствующих каналов, при этом третий вход логической схемы «И каждого предыдущего канала подсоединен к коллектору транзистора диод-транзисторной ст|руктуры последующего канала, а эмиттер входного инвертора каждого предыдущего канала соединен с коллектором выходного инвертора последующего канала.

В описании приведен пример .выполнения многоканального селектора по длительности для регистрации, например, импульсов трех различных длительностей (минимальной, средней и максимальной) с .последующим

распределением импульсов регистрации по .каналам.

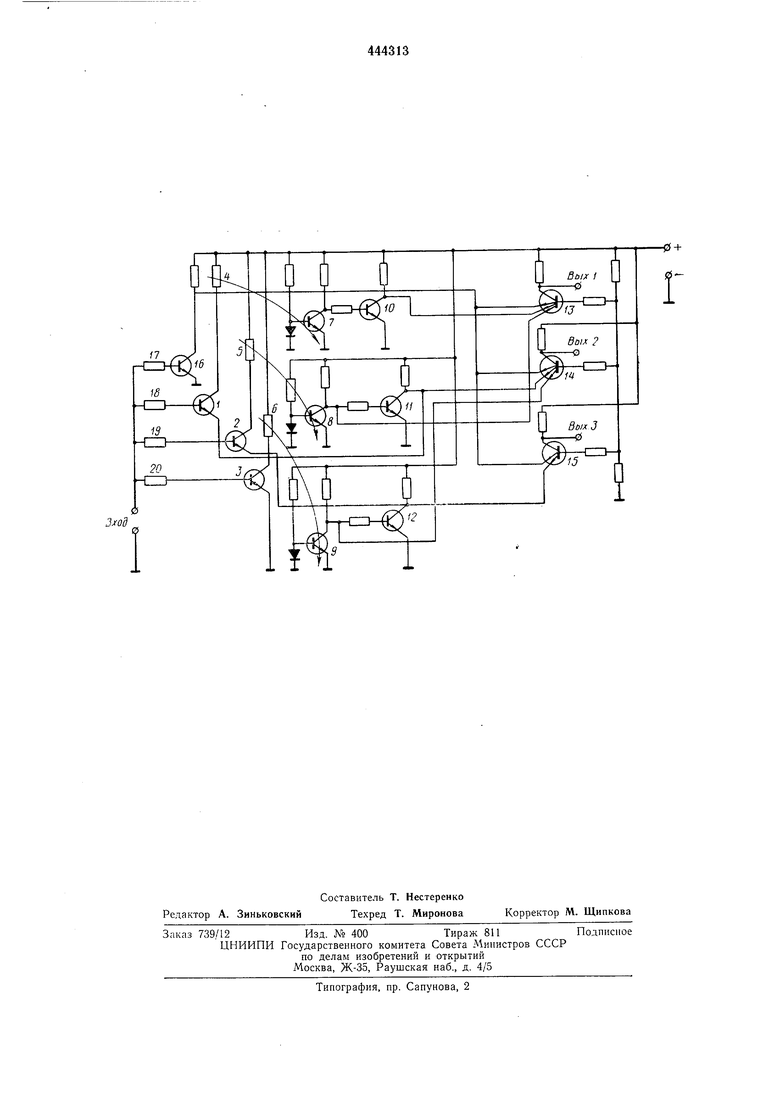

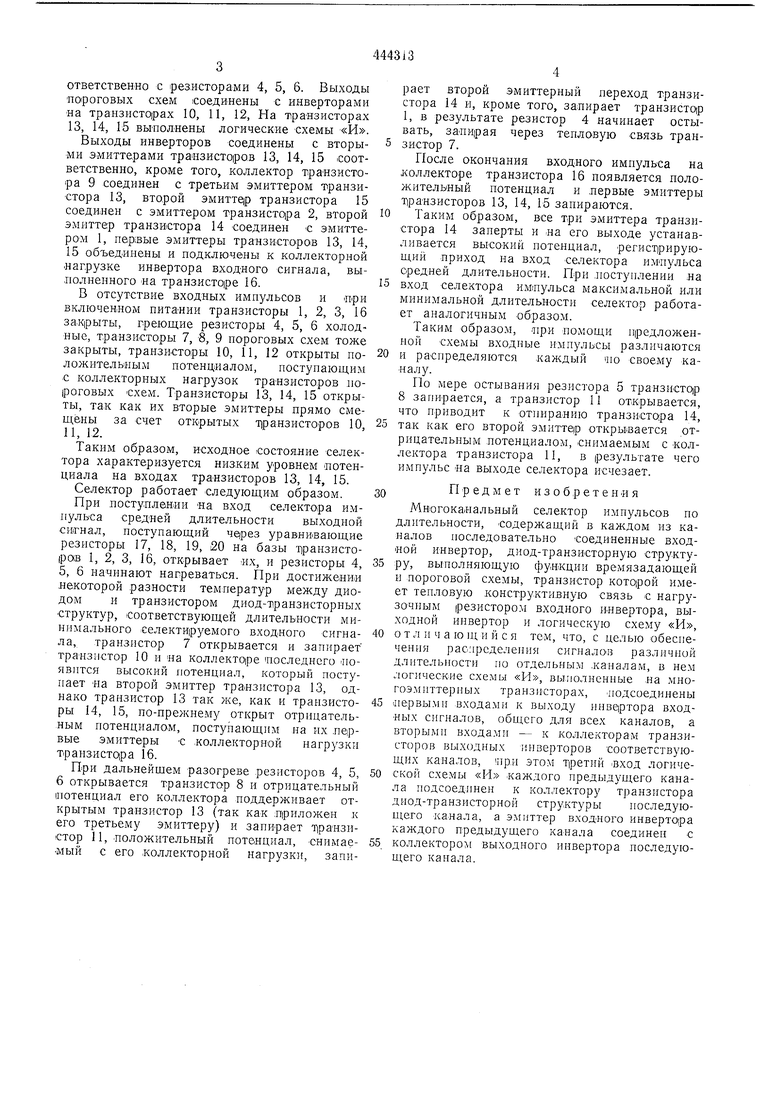

На чертеже приведена принципиальная электрическая схема селектора.

Многоканальный селектор «мпульсов по

длительности содержит транзисторы 1, 2, 3, коллекторными наг1рузками которых являются греющие резисторы 4, 5, 6, пороговые схемы, представляющие собой диод-транзисторные структуры с транзисторами 7, 8, 9, имеющие тепловую конструктивную связь соответственно с резисторами 4, 5, 6. Вььходы пороговых схем соединены с инверторами на транзисторах 10, 11, 12, На транзисторах 13, 14, 15 выполнены логические схемы «И.

Выходы инверторов соединены с вторыми эмиттерами транзисторов 13, 14, 15 соответственно, кроме того, коллектор транзистора 9 соединен с третьим эмиттером транзистора 13, второй эмитте|р транзистора 15 соединен с эмиттером транзистора 2, второй эмиттер транзистора 14 соединен с эмиттером 1, пер;вые эмиттеры транзисторов 13, 14, 15 объединены и подключены к коллекторной «агрузке инвертора входного сигнала, выполненного на транзисторе 16.

В отсутствие входных импульсов и при включенном питании транзисторы 1, 2, 3, 16 закрыты, греющие резисторы 4, 5, 6 холодные, транзисторы 7, 8, 9 пороговых схем тоже закрыты, транзисторы 10, И, 12 открыты положительным потенциалом, поступающим с коллекторных нагрузок транзисторов пороговых схем. Транзисторы 13, 14, 15 открыты, так как их вторые эмиттеры прямо смещены за счет открытых 11ранзисторов 10, И, 12.

Таким образом, исходное состояние селектора характеризуется низким уровнем потенциала на входах транзисторов 13, 14, 15.

Селектор работает следующим образом.

При поступлении на вход селектора импульса средней длительности выходной сигнал, поступающий че|рез уравнивающие резисторы 17, 18, 19, 20 на базы Т|ранзистоipOB 1, 2, 3, 16, открывает «х, и резисторы 4, 5, 6 начинают нагреваться. При достижении некоторой разности температур между диодом и транзистором диод-транзисторных структур, соответствующей длительности минимального селектируемого входного сигнала, транзистор 7 открывается и запирает транзистор 10 и на коллекторе последнего -появится высокий потенциал, который поступает на второй эмиттер транзистора 13, однако транзистор 13 так же, как и трапзисторы 14, 15, по-прежнему открыт отрицательным потенциалом, поступающим на их .neipвые эмиттеры с .коллекторной нагрузки транзистора 16.

При дальнейщем разогреве резисторов 4, 5, 6 открывается транзистор 8 и отрицательный потенциал его коллектора поддерживает открытым транзистор 13 (так как приложен к его третьему эмиттеру) и запирает Т|ранзистор 11, положительный потенциал, снимаемый с его .коллекторной нагрузки, запирает второй эмиттерный переход транзистора 14 и, кроме того, запирает транзистор 1, в результате резистор 4 начинает остывать, запирая через тепловую связь транзистор 7.

После окончания входного импульса на коллекторе транзистора 16 появляется положительный потенциал и первые эмиттеры Т|ранзисторов 13, 14, 15 запираются.

Таким образом, все три эмиттера транзистора 14 заперты и на его выходе устанавливается высокий потенциал, регистрирующий приход на вход селектора импульса средней длительности. При поступлении на

вход селектора импульса максимальной или минимальной длительности селектор работает аналогичным образом.

Таким образо.м, при помощи предложенной схемы входные импульсы различаются

и распределяются каждый чю своему каналу.

По мере остывания резистора 5 транзистор 8 запирается, а транзистор И открывается, что приводит к отпиранию транзистора 14,

так как его второй эмитте|р открЫВается отрицательным потенциалом, снимаемым с коллектора транзистора И, в результате чего импульс на выходе селектора исчезает.

Предмет изобретения

Л1ногоканальиый селектор импульсо1В по длительности, содержащий в каждом из каналов последовательно соединенные входной инвертор, диод-транзисторную структуру, выполняющую функции времязадающей и пороговой схемы, транзистор которой имеет тепловую конструктивную связь с нагрузочным резистором входного инвертора, выходной инвертор и логическую схему «И,

отличающийся тем, что, с целью обеспечения распределения сигнало-в различной длительности по отдельным .каналам, в не.м логические схемы «И, выполненные на .многоэмиттерных транзисторах, подсоединены

первыми входами к выходу пнвертора входных спгналов, общего для всех каналов, а вторыми входами - к коллекторам транзисторов выходных инверторов соответствующих каналов, при этом третий -вход логической схемы «И .каждого предыдущего канала подсоединен к коллектору транзистора диод-транзисторной структуры последуюД1,его канала, а эмиттер входного инвертора каждого предыдущего канала соединен с

коллекторов выходного инвертора носледующего канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одновибратор | 1978 |

|

SU733088A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Устройство преобразования однофазового логического сигнала в парафазный ток | 1976 |

|

SU570201A1 |

| ОДНОТАКТНЫЙ СТАБИЛИЗИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1991 |

|

RU2007826C1 |

| Формирователь импульсов | 1981 |

|

SU1018213A1 |

| Транзисторно-транзисторный элемент и-не/и | 1973 |

|

SU450365A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Селектор импульсов по длительности | 1980 |

|

SU881994A1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

Авторы

Даты

1974-09-25—Публикация

1972-09-08—Подача