Изобретение относится к вычислительным устройствам, действующим по принцину аналого-цифро-аналогового преобразования и предназначенным для выполнения операций умножения, деления и нелинейного преобразования. Может быть иснользовано в различных областях автоматики и вычислительиой техники для реализации и моделирования физических систем, где требуется выполнение названных операций с электрическими величинами.

Известные схемы преобразователей нанряжения в параллельный двоичный код содержат по два операционных усилителя и по одному сравнивающему и переключающему устройству на каждый разряд кода. Декодирующие преобразователи состоят из матрицы сопротивления и переключателей, количество которых равно удвоенному числу разрядов кода, причем управление переключателями для удобства согласования часто осуществляют через трансформаторы, что затрудняет микроминиатюризацию устройства.

Цель настоящего изобретения заключается в упрощении множительно-делительного устройства.

Упрощение схемы множительно-делительного устройства достигается реализацией в нем нринципа двукратного преобразования нараллельно о двоичного циклического кода путем непосредственного соединения кодирующего и

декодирующего преобразователей специального вида, каждый из которых ностроен на однотипных элементах - пропорциональных ключах, выполненных на основе операционных уоилителей; причем в каждом из преобразователей на один разряд кода приходится по одному пропорциональному ключу. Это обеспечивает унификацию входящих узлов, упрощает технологию изготовления устройства и позволяет

реализовать технологический процесс с получением множительно-делительного устройства в микросхемном исиолиеиии. Кроме того, предлагаемая схема позволяет реализовать нелинейное преобразование функций, в том числе

одновременно с выполнением операции умножения и деления, так как пропорциональные ключи в преобразователях кода имеют онределенное количество непосредственных соединений между собой, что позволяет подбором коэффициентов но входам ключей получить достаточное количество узлов интерполяции для приближения нелинейной функцни с заданной точностью.

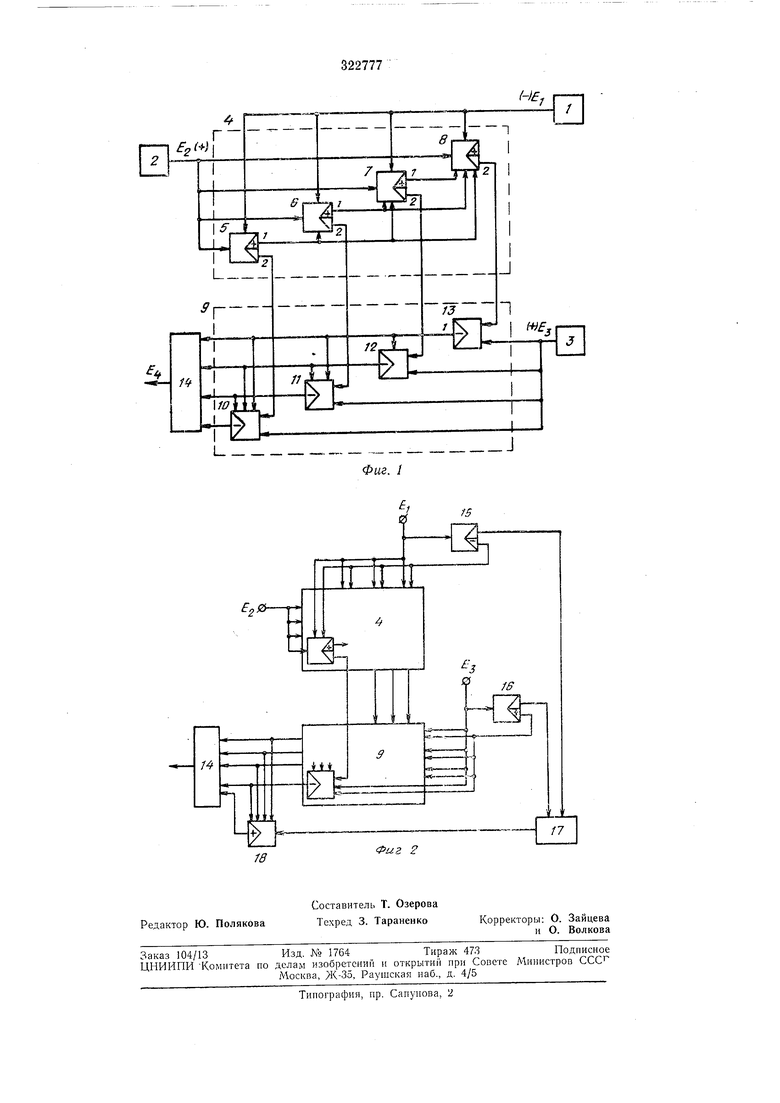

На фиг. 1 показана блок-схема одноквадратного множительно-делительного устройства (МОУ); на фиг. 2 - блок-схема того же устройства в четырехквадрантном исполнении. преобразователь (КП) 4, состоящий из пропорциональных ключей 5-8 с линейными и регистрирующими выходами, и декодирующий преобразователь (ДП) 9, состоящий из ключей 10-13 с линейными выходами и аналогового сумматора 14. Каждый из ключей КП двумя входами порознь непосредственно соединен с источниками , причем каждый из последующих ключей соединен другими своими входами с линейными выходами всех предыдущих ключей, а источник 3 соединен с соответствующими входами ключей ДП. При этом регистрирующие выходы ключей Л/7, образующие кодовый регистр КП, соединены непосредственно с разрядными входами соответствующих ключей ДП. Каждый из последующих ключей ДП соединен своими входами с выходами всех предыдущих ключей, а вглходы всех ключей ДП соединены со входами сумматора, выход которого является выходом устройства. Принцип действия множительно-делительного устройства состоит в следующем. В лииейном КП зависимость между двоичным циклическим кодом L на регистрирующих выходах ПК, преобразуемым электрическим сигналом jE| и напряжением Е. (при 2 :const оно вынолняет роль эталонного напряжения) может быть выражена следующим соотношением: I, , - , -величина напряжения-эквиMIвалент младшего разряда двоичного циклического кода; т, - постоянный коэффициент, равный максимальному значению числа, выражаемого установлеииым количеством разрядов кода преобразователя;/(i const - масштабный коэффициепт. Соответственно в линейном декодирующем преобразователе зависимость между выходиым напряжением .1, преобразуемым двоичным циклическим кодом La на его входе и напряжением .- (при 3 Const оно выполняет роль эталонного напряжения) может быть выражена следующим соотион1ением; E,r:L, К.„ где т2, К.2-постоянные коэффициенты, аналогичные /Пь К в (1). Так как преобразователи соединены последовательно, то выход КП является входом ДП. При этом: , m2 tni /Ci /(2, где /(, /Cj const (4) Таким образом, предлагаемое устройство позволяет производить операцию, при которой одна из электрических величин умножается на другую и делится на третью. При постоянстве одного из входных напряжений осуществляется операция умножения или деления. В кодирующем и декодирующем преобразователях подбором коэффициентов передачи по входам, соединяющим ПК между собой и с источниками 2 и 3, можно реализовать преобразование вида и некоторые другие пелинейные преобразования напряжения в код и кода в напряжение. Для этого искомая кривая напряжения заменяется приближенной ступенчатой функцией. Коэффициенты передачи для ПК подбираются по значениям функции в узлах интериоляции. Таким образом, иредлагаемое устройство позволяет производить операции умножения и деления с одновременным нелинейным преобразованием. Для реализации вычислительных операций с учетом знаков нанряжений ,, 2 и з в вынолняемом устройстве эти напряжения поступа ют на входы ключей соответствующих преобразователей не только непосредственно, как было ноказано на фиг. 1, но и через знаковые пропорциональные ключи 5 и 16 (см. фиг. 2) на соседние незанятые входы тех же ключей с удвоенным коэффициентом передачи. Каждая такая inapa входов обеспечивает для данного ключа электрический режим, эквивалентный режиму подачи на один вход однополярного напряжения. Действительно, пусть в исходном состояиии полярность напряжений i, 3 и проводимость ключей кодирующего и декодирующего преобразователей согласованы. Проводимость знаковых пропорциональных ключей /5 и 16 выбнрается такой, что они в этом случае закрыты. Признак этого состояния фн1;сирован высокиаМ уровнем напряжения па регистрирующих выходах этих ключей. Если напряжения i н з изменяют знак, то соответствующие знаковые ключи открываются, напряжения на их регистрирующих выходах становятся равными нулю, а на линейных выходах появляются папряжения i и з прежней нолярности и передаются с удвоенным коэффициентом передачи по отношению к входам, иа которые нанряжения и з поступают непосредственно. Таким образод, на ключах преобразователей неизменно поддерживается электрический режим, эквивалентный подаче однополярных напряжений. Аналогично может быть реализовано переключение напряжения 2. ние на выходе схемы 17 фиксируется на нуле, если по соотношению между знаками входных напряжений Е и з выходное напряжение должно изменяться в области отрицательных значений, или имеет высокий (положительный) уровень, если выходное напряжение должно быть положительным. Выход логической схемы выбора знака со- . единен со входом пропорнионального ключа 18, используемого для переключения знака вы- ю ходного напряжения. Коэффициент передачи аналогового сумматора по входу, соединяющему сумматор с выходом знакового ключа 12, равен удвоенной сумме коэффициентов передачи по остальным входам сум.матора, соеди- is няющшм его с выходами ключей ДП. Поэтому при нулевом уровне напряжения на выходе схемы /7 знаковый ключ 18 открыт и происходит одновременно алгеораическое суммированне н двойное инвертирование выходных 20 отрицательных напряжений ДП, в результате чего на выходе сумматора напряжение получается отрицательным, напротив, нри высоком (положительном) уровне напряжения на выходе схемы /7 ключ 18 закрыт, и на сумматоре 25 осуществляется арифметическое суммирование н инвертирование знака напряжений ДП с получением положительного выходного напряжения. При использовании в пропорциональных зо ключах операционных усилителей с невысоким коэффициентом усиления (500-1000) можно снизить погрешность ключей до уровня погрешностн входных масштабных сопротивлений применением схемы автоматической ком- 35 пенсации. Ко.мпенсация осуществляется с номощью вспомогательного нронорционального ключа, входы которого подключаются к линейному выходу и ко всем входам компенсируемого основного ключа. Проводимость40 обоих ключей одинакова. На выходе вспомогателыюго ключа вырабатывается сигнал ошибки, который затем добавляется к сигналу основного ключа. При закрытом основном ключе компенсирующий ключ также закрыт,45

поэтому на его выходе не появляется ложного 5

сумматора. сигнала при изменении знака напряжения 1. Для правильной работы схемы коэффициент передачи основного ключа выбирается с таким расчетом, чтобы ошибка, вносимая этим ключом, была односторонняя и была согласована с проводимостью компенсирующего ключа. Ошибку можно сделать односторонней также подачей смещения на один из входов основного ключа. Предмет изобретения 1. Множительно-делнтельное устройство, содержащее кодирующий и декодирующий преобразователи нараллельного двоичного цнклического кода, вынолненные на нропорциональных ключах с инвертированием знака и односторонней проводимостью на выходе, и аналоговый сумматор, отличающееся тем, что, с-целью упрощения устройства, преобразователи выполнены один относительно другого на пропорциональных ключах противоположной проводимости, причем входы ключей декодирующего преобразователя соединены с соответствующими им выходами ключей кодирующего преобразователя, каждый из которых соединен с двумя источниками нанряженнй, пропорциональных одному из сомножителей и делителю, а источник напряжения, пронорционального второму сомножителю, подключен ко входам всех ключей декодирующего преобразователя. 2. Устройство по п. 1, отличающееся тем. что, с целью расширения функциональных возможностей, оно содержит дополнительно логическую схему выбора знака, а каждый из источников нанряжения дополнительно соединен с каждым ключом соответствующего преобразователя через знаковый пропорциональный ключ, причем выходы этих ключей соедмиены через логическую схему выбора знака с выходом дополнительного ключа, другие выходы которого соединены с выходами ключей декодирующего преобразователя, а выход последнего подключен ко входу аналогового

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ | 1973 |

|

SU394817A1 |

| Устройство для функционального преобразования | 1978 |

|

SU734712A1 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

| Цифро-аналоговый множительно- ТРигОНОМЕТРичЕСКий пРЕОбРАзОВАТЕль | 1978 |

|

SU822223A1 |

| РЕВЕРСИВНЫЙ ЧИСЛО-ИМПУЛЬСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2429563C1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1280400A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU419921A1 |

| Стохастическое множительно-делительное устройство | 1991 |

|

SU1833861A1 |

| Цифроаналоговый преобразователь | 1981 |

|

SU1027811A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

Даты

1971-01-01—Публикация