Изобретение относится к аналого- вой вычислительной технике и может быть использовано в устройствах и системах автоматики.

Цель изобретения - повьшение точности умножения.

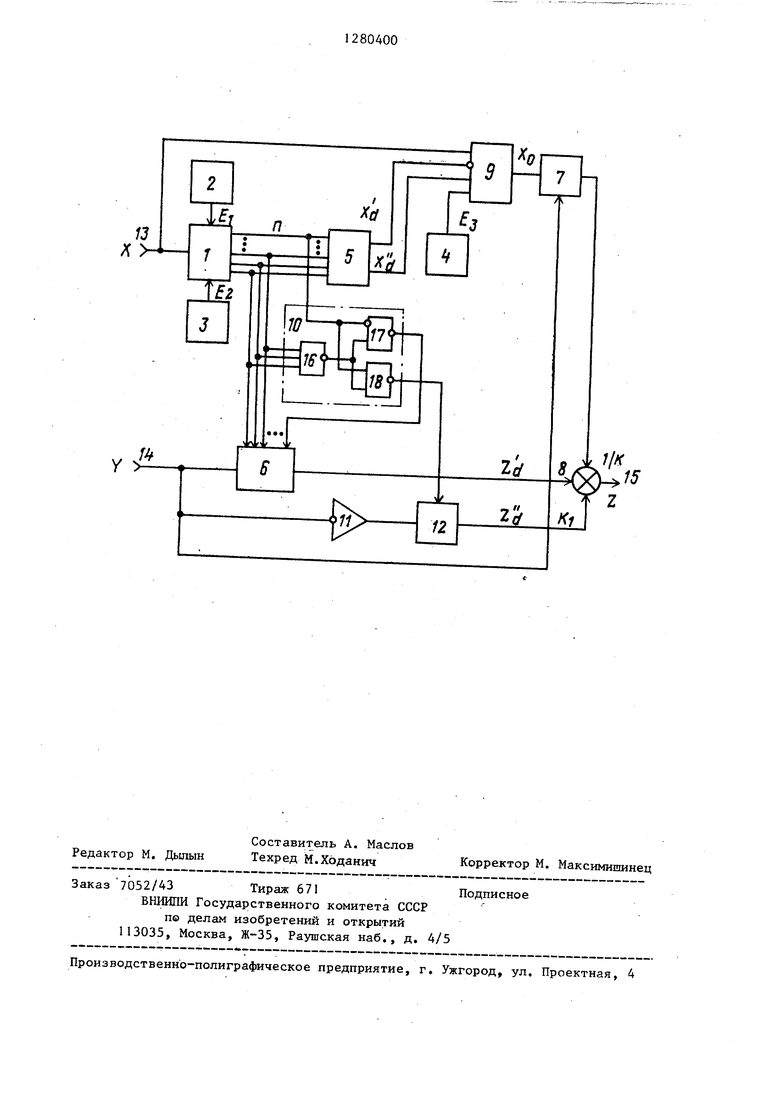

На чертеже приведена схема аналого-цифрового множительного устрой- ст.ва.

Множительное устройство содержит аналого-цифровой преобразователь (АЦП) 1 первый 2, второй 3 и третий 4 источники опорного напряжения (ионj цифроаналоговый преобразователь (ЦАП) 5, умножающий цифроаналоговый преобразователь (УЦАП) 6, аналоговый перемножитель (ЛП) 7, сумматор 8, блок суммирования - вычитания (БСВ) 9, блок управнения (ВУ) 10 умножением, на логический нуль, инвертор 11, .ключ 12, первый 13 и второй 14 вхо-. |ды и выход 15,устройства. Кроме того, БУ 10 содержит элементы ИЛИ-НЕ 16 и 17 и элемент И-НЕ 18. Перечисленные элементы и блоки соединены по приведенной схеме.

Аналого-цифровое множительное устройство работает следующим образом.

Первый знакопеременный сомножитель X поступает с входа 13 устройства на информационный вход АЦП 1. К опорным входам АЦП 1 приложены опорные напряжения Е -Е ИОН

2 и 3:

N

к-2 -2.. .

()

где X.

- максимальное значение

сомножителя X; Ы - число разрядов АЦП 1. Результат аналого-цифрового преобразования представлен параллельным смещенным двоичньм кодом п:

40

г,, (а)

. масштабный коэффициент АП 7.

(х+2 о.

Е

d+ьк),

(2)

Одновременно дискретная часть сомножителя X в форме двоичного смещенного кода п подается на соответству- 45 ющие разрядные входы УЦАП 6, причем N-1 младших разрядов кода п поступает на УЦАП 6 непосредственно, а старший (знаковый) разряд - через БУ 10. Логический сигнал на выходе

НИН, приведенная к вхо-50 элемента ИЛИ-НЕ 17 БУ 10, управляю- ду АЦП 1 ,щий старшим разрядом УЦАП 6, равен

где й я|5-г,-г интервал квантования; ли. - погрешность квантоваw-л

нулю для П42 и единице для п 2 Соответственно сигнал на выходе УЦАП 6 определяется соотношением

Кодовый сигнал п поступает на соответствующие разрядные входы ЦАП 5,, в котором осуществляется преобразование кода п в аналоговую форму, при- чем на основном выходе ЦАП 5 образуется дискретная часть х сомножителя X, а на дополняющем выходе - ее дополнение до максимального сигнала

X j , соответствующего значению входного кода -1. Таким образом:

. «оке цаг

,о.П

()d.

d -х-д) . (4)

Сигналы xj и поступают соответственно на инвертирующий и неинвертирующий входы блока 9, к двум другим неинвертирующим входам которого приложены сомножитель X и смещающее напряжение Е источника 4, На выходе блока 9 образуется остаток

(x+x j ).(5)

Подставив в последнее соотнощение выражения (3) и (4) и преобразовав, получим

X k (,. (6) Положив , получим

,

(7)

5 где К - масштабный коэффициент результата суммирования - вычитания, значение которого (с целью максимального снижения влияния погрешности 0 АП 7) выбирается близким к значению числа уровней квантования АЦП 1. Поступая далее на один их входов АП 7, остаток х умножается на вто- рой сомножитель Y, который подается с Входа 14 устройства.

Результат перемножения равен

40

г,, (а)

. масштабный коэффициент АП 7.

элемента ИЛИ-НЕ 17 БУ 10, управляю- щий старшим разрядом УЦАП 6, равен

w-л

нулю для П42 и единице для п 2 Соответственно сигнал на выходе УЦАП 6 определяется соотношением

т/nY - i 4

( d-t-л )Y,

(9)

N4

Для исключения составляющей смещения, в результате цифроаналогового умножения используется дополнительно введенная цепь инвертор 11 - ключ 12. Управляющий вход последнего подключен к выходу элемента НЕ БУ 10, на котором формируется логический сигнал, равный нулю, при и единице - во всех остальных случаях. Сигнал на выходе ключа 12 ./J-Y, М О,

N-1

.(10)

Результаты аналогового Z и дискретно-аналогового Zj умножения, а также компенсирующий сигнал Z поступают на входы сумматора 8 с коэффициентами суммирования 1/К; 1 и Кд, соответственно.

На выходе сумматора В образуется результат перемножения Z:

Z IZ+Z ,+K z, -К & Y+ К d 1 dor к

-К )Y+ ii - u J,

. .

1-,N-1

СП)

О,

-.«Заметим, что значение соот-зо ветствует значениям сомножителя X и результата Z, равным нулю. Поэтому

(K

„2 -K)Y+(-|- -Kan xY. (12)5

Уравняв масштабные коэффициенты умножения дискретной и аналоговой частей К ап и положив Кддп К-, получим окончательно .(13)

40

Формула

изобретения

Аналого-цифровое множительное устройство, содержащее аналого-циф-. ровой преобразователь, цифроаналого- вый преобразователь, умножающий циф- роаналоговый преобразователь, аналоговый перемножитель, блок суммирования-вычитания, ключ, инвертор и сумматор, выход которого является выходом устройства, а первый и второй входы соединены соответственно с ходом умножающего цифроаналогового преобразователя и с выходом аналого- вого перемножителя, подключенного одним входом к одному из информацион10

f5

20

1 25

-зо

)5

40

45 5055 ных входов устройства и к аналоговому входу умножающего цифроаналогового преобразователя, а другим входом - к выходу блока суммирования-вычитания, цифровые ВХО.ДЫ младших разрядов умножающего цифроаналогового i преобразователя подключены к соответствующим разрядным входам цифроаналогового преобразователя и к соответствующим разрядным выходам аналого- цифрового преобразователя, вход которого является другим информационным входом устройства, отличающееся тем, что, с целью повы- Щения точности, оно содержит первый, второй и третий источники опорного напряжения и блок управления умножением на логический нуль, выполнен П11Й в .виде двух элементов ИЛИ-НЕ и элемента И-НЕ, выход которого подключен к управляющему входу ключа, а два входа соединены соответственно с выходом первого и инвертирующим входом второго элементов ИЛИ-НЕ, группа входов первого элемента ИЛИ-НЕ блока управления умножения на логический нуль подключена к соответствующим выходам младщих разрядов аналого-цифрового преобразователя, выход старшего разряда которого соединен с входом старшего разряда цифроаналогового преобразователя и с инвертирующим входом второго элемента ИЛИ-НЕ, подключенного неинвертирующим входом и выходом соответственно к выходу первого элемента ИЛИ-НЕ блока управления умножением на логический нуль и к цифровому входу старшего разряда умножающего цифроаналогового преобразователя, два опорных входа аналого-цифрового преобразователя подключены к выходам соответственно первого и второго источников опорных напряжений, три неинвертирующих входа блока сложения-вычитания подсоединены соответственно к информационному входу аналого-цифрового преобразователя, дополняющему выходу цифроаналогового преобразователя и к выходу третьего источника опорного напряжения, а его инвертирующий вход соединен с Основным выходом цифроаналогового преобразователя, третий вход сумматора подключен через ключ к выходу инвертора, вход которого соединен с аналоговым входом умножающего цифроаналогового преобразователя.

Y

Редактор M. Дьшын

Составитель A. Маслов Техред М.Ходанич

Заказ 7052/43 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

;//r

/

Корректор М, Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое множительное устройство | 1984 |

|

SU1215122A1 |

| Устройство для воспроизведения функций двух переменных | 1987 |

|

SU1517046A1 |

| Гибридное множительное устройство | 1985 |

|

SU1325521A1 |

| СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ С ЧАСТОТНЫМ ВЫХОДОМ | 1992 |

|

RU2037830C1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2282937C1 |

| СЧЕТЧИК ПОТЕРЬ ЭЛЕКТРОЭНЕРГИИ С ИНДИКАЦИЕЙ ПОТЕРЬ МОЩНОСТИ (ВАРИАНТЫ) | 2010 |

|

RU2449356C1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Аналого-цифровая вычислительная система | 1987 |

|

SU1509955A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах и устройствах автоматики. Целью и брете-. НИН является повышение точности умножения. Поставленная цель достигается за счет изменения формы представления дискретной части одного из сомножителей вместо прямого кода со знаком, использовавшегося в известном устройстве, смещенным двоичным кодом, что позволило исключить источники погрешностей, связанные с обеспечением четырехквадрантнрго режима работы - инверторы и аналоговые коммутаторы из сигнальных цепей У ;т- ройства. Основные конструктивные отличия состоят во введении в устройство первого, второго и третьего источников опорного напряжения и блока управления умножением на логический нуль, содержащего два элемента ШШ-НЕ и элемент И-НЕ, а также в наличии новых связей между элементами и блока ми, чем и обеспечивается достижение поставленной цели. 1 ил. i (Л С

| Математическое моделирование и теория электрических цепей, вьш | |||

| II | |||

| - Киев: Наукова думка, 1973, с | |||

| Соломорезка | 1918 |

|

SU157A1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1215122A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1986-12-30—Публикация

1984-11-30—Подача