1

Изобретение относится к области вычислительной техники.

Известны устройства для интегрирования, содержащие кодирующие преобразователи переменной интегрирования и подынтегральной функции, блок управления, ключевые блоки, запоминающие регистры, множительные блоки, декодирующий преобразователь и выходной сумматор.

Предложенное устройство отличается от известных тем, что в него введены пороговый блок и формирователь, входы которого соединены с выходами кодирующего преобразователя переменной интегрирования, подключенного выходом к первому входу блока управления, другие входы которого соединены через пороговый блок с выходами формирователя и с первыми входами соответствующих множительных блоков, вторые входы которых соединены через соответствующие запоминающие резисторы с выходами первой пары ключевых блоков, подключенных первыми входами к выходам блока управления, а вторыми входами - к выходу кодируюи1,его преобразователя подынтегральной функции, соединенного через декодирующий преобразователь с выходами .второй пары ключевых блоков, первые входы которых подключепы к соответствующим выходам блока управления, а вторые входы которых соединены со вторыми входами множительных олоков, подключенных выходами ко входам выходного сумматора.

Это позволило повысить быстродействие

устройства.

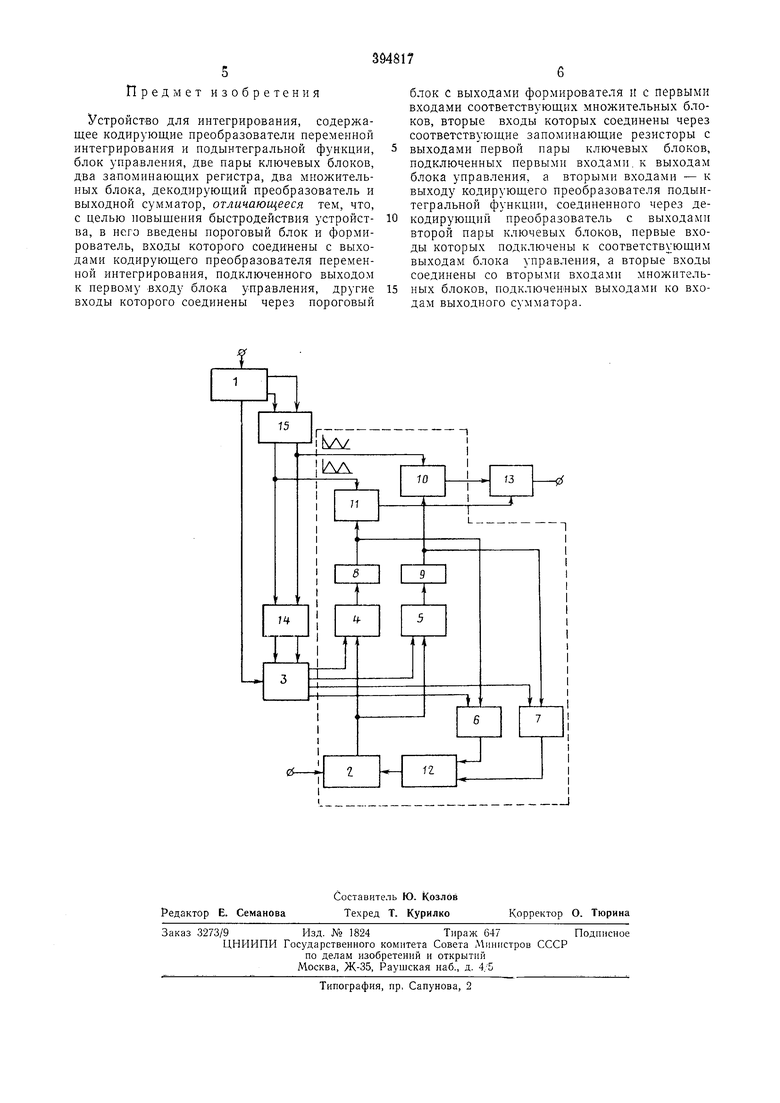

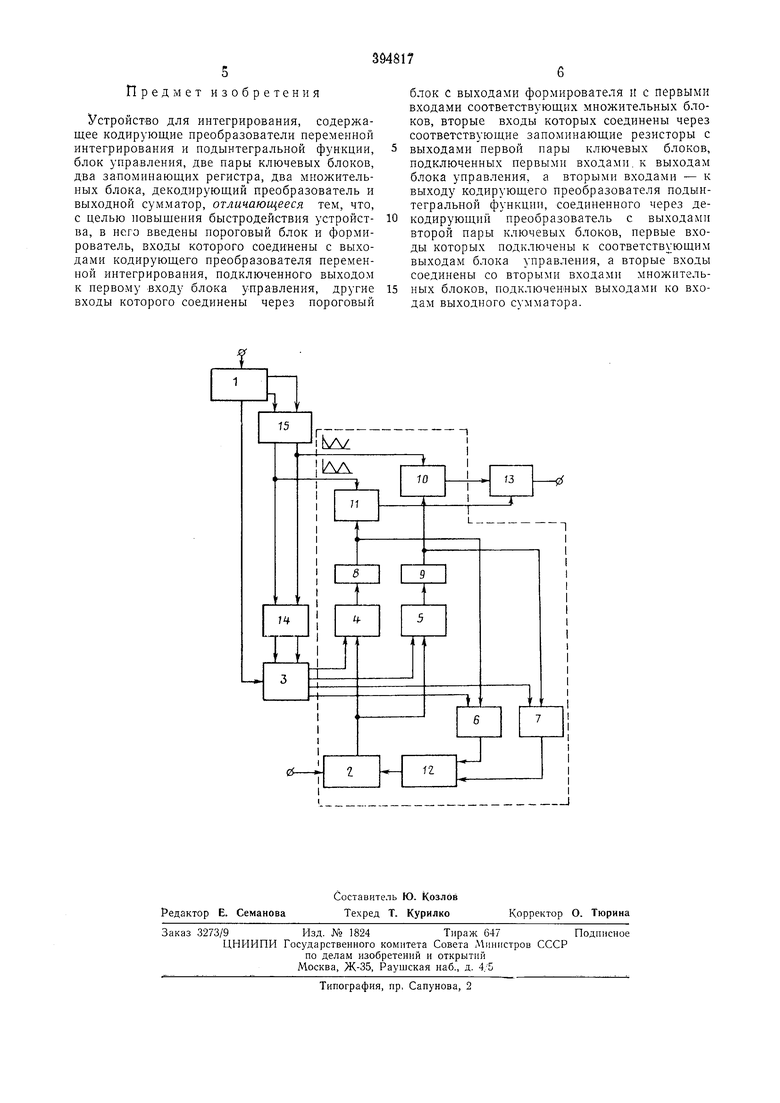

Блок-схема устройства ириведепа на чертеже.

Устройство содержит кодирующие преобразователи переменной интегрирования / и

подынтегральной функции 2, блок управления 3, две пары ключевых блоков 4, 5 и 6, 7, два запоминающих регистра 8 и 9, два множительных блока 10 и //, декодирующий преобразователь 12 и выходной сумматор 13.

Кроме того, в устройство введены пороговый блок 14 и формирователь 15.

Приближенное интегрирование по известной линейной интерполяционной формуле реализуется следующим образом.

С началом первого щага интегрирования сигнал подынтегральной функции суммируется на входе кодирующего преобразователя подынтегральной функции 2 с напряжением декодирующего преобразователя 12, которое

в определенном масщтабе соответствует коду запоминающего регистра 9, подключенного на этом щаге к преобразователю через ключевой блок 7. Код суммы с выхода кодирующего преобразователя подынтегральной функции 2 поступает через ключевой блок 4 в запоминающий регистр 8. Считываиие производится на участке изменепия переменпой по сигналу, который образуется в блоке управления из сигнала, соответствующего нечетному шагу интегрирования, и сигнала порогового бло.ка 14.

При нулевых начальных условиях в заномппающем регистре 9 записано число нуль, поэтому в этом случае на нервом шаге интегрнрован я в запоминающий регистр 8 записывается код нодыинтегральной функции, причем в первой ноловине гнага заиисывается его текун1ее значение в результате непрерывного прохождения кода е кодируюп1,его преобразователя подынтегральной функции 2 на заноминающий регистр. С нрекращеHfieM в середине шага интегрирования ностуиления сигнала в ключевой блок 4 заиись в запоминающий регистр 8 прекращается, и он переходит в режим запоминания. Выход запоминающего регистра 8 постоянно подключен к цифровому входу множительного блока

11,на другой вход которого поетупает линейно-нарастающее нанряжение. На выходе множительного блока 11 нанряжение изменяется по закону, близкому к линейному. Некоторое отклонение от линейного за,кона на одном участке происходит потому, что в течение этого полушага интегрирования значение кода в заиомииающем регистре 8 не фиксировано. Это отклонение направлено в сторону компенсации погрешности, присущей методу линейной иитерполяции.

С начала второго шага интегрирования по сигналу, который образуется в блоке управления 3, осуществляется считывание в запоминающий регистр 9 кода суммы, образующегося на выходе кодирующего преобразователя подынтегральной функции 2 в результате суммирования на его входе сигнала подынтегральной функции и выходного напряжения декодирующего преобразователя

12,соответствующего запомненному ранее значению кода, хранящегося в заноминающем регистре, который на этом шаге подключен к декодирующему преобразователю 12 через ключевой блок 6.

Нроцесс считывания за1канчи1ваеТСЯ в середине текущего шага с прекращением поступ лення сигнала с блока управления 3 в ключевой блок 5. В запомииающем регистре 9 запоминается код суммы с учетом значення подыннтегральной функции в середине шага интегрирования. Выход заноминающего регистра 9 постоянно подключен к цифровому входу множительного блока 10, на другой ВХОД которого поступает линейно-парастающее напряжение. Напряжение с выхода мцожительпого блока 10 суммируется с напряжением, поступающим с выхода множительного блока // на сумматор 13. Нри этом осуществляется компенсация уменьшающегося на втором шаге интегрнрования напряжения, снимаемого с выхода множительного блока

11, которое на этом шаге моделирует интегрирование фактически отсутствующего отрицательного нрямоугольника с начальными условиями, определениы.м истинным интегрированнем на нерво.м шаге ноложнтельлого прямоугольника, площадь которого рав.на площади отрицательного нрямоугольннка. Описанное «ложное ннтегрированне компенс фуется с номощью второго множительного

блока 10 тем, что умножаемый в течение шага код в заг1омннаюн 1ем регнстре 9 равен сумме кода запоминаю цего регистра 8 н кода нодыинтегральной функцни. Комненсацня обеспечивается также тем, что вторые сомножители на входах множнтельных блоков 10 н // - треугольные функцнн нанряжения нормнрованы но амплитуде, которая равна установленной шкале нанряжения (10 в, 30 в или 100в). В результате суммирования ланряжепне, поступающее на выход сумматора 13, равное сумме наПряжений множительных блоков 10 и 11, изменяется от уровня, достигнутого в точке, с крутизной, нроиорциональной значению нодыиитегральной функции в

середине шага интегрирования. При этом происходит отклонение от пропорциональнбстн. Это отклонение снособствует частичной компенсации иогрешноетн линейной интерноляции.

Аналогично осуществляется процесс интегрирования на следующих шагах. В первой половине каждого нечетного шага происходит запись в запомипающий регистр 8 суммы

кода запоминающего регистра 9 и кода подынтегральной функцни. В течение последующей половины данного нечетного шага и веего следующего четного шага заноминающий регистр 8 сохраняет запомненное значенне кода. Нодобным же образом в нервой ноловнне каждого четного шага происходит запись в запоминающий регистр 9 суммы кода запоминающего регистра 8 и кода подыинтегральной функции.

В течение последующей половины данного четного шага н всего следующего нечет1юго шага запоминающий регистр 9 сохраияет запомненное значенне кода. Происходит непрерывная компенсация участков треугольных

функций с отрицательной крутизной.

Оиерации суммирования на входе кодируюHiero нреобразователя нодынтегральной функнии 2 осуществ;1яются с учетом знаков суммируемых кодов. Знак результата выдается

в знаковые разряды заиомииающих регистров, которые управляют включением или выключением инверторов в множительных блоках 10 н //.

Колнмество разрядов кодирующего преобразователя подыинтегральной функции 2 соответствует числу, которое получается в результате суммироваиия на его входе максимальных значений подынтегральной

в течение всех шагов ннтегрирования.

Предмет изобретения

Устройство для интегрирования, содержащее кодирующие преобразователи переменной интегрирования и подынтегральной функции, блок управления, две пары ключевых блоков, два запоминающих регистра, два множительных блока, декодирующий преобразователь и выходной сумматор, отличающееся тем, что, с целью новышения быстродействия устройства, в него введены пороговый блок и формирователь, входы которого соединены с выходами кодирующего преобразователя неременной интегрирования, подключенного выходом к первому входу блока управления, другие входы которого соединены через пороговый

блок с выходами формирователя с первыми входами соответствующих множительных блоков, вторые входы которых соединены через соответствующие запоминающие резисторы с выходами первой пары ключевых блоков, подключенных первыми входами, к выходам блока управления, а вторыми входами - к выходу кодирующего преобразователя подынтегральной функции, соединенного через декодирующий преобразователь с выходами второй пары ключевых блоков, первые входы которых подключены к соответствующим выходам блока управления, а вторые входы соединены со вторыми входами множительных блоков, подключенных выходами ко входам выходного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1971 |

|

SU322777A1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU294156A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1972 |

|

SU328482A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1971 |

|

SU291216A1 |

| Решающий блок цифровой интегрирующей структуры | 1976 |

|

SU650085A2 |

| Интегрирующее устройство интегрирующей машины последовательного типа | 1974 |

|

SU526927A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОЙ МОДЕЛИ | 1967 |

|

SU223472A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

I

Авторы

Даты

1973-01-01—Публикация