Изобретение относится к вычислительной технике и автоматике и может найти применение в аналого-цифровых и цифроаналоговых преобразователях, гибридных вычислительных системах, дисплейных устройствах ввода-вывода графической информации для ЭВМ, в которых требуется высокая линейность цифро-аналогового преобразования.

Известен цифро-аналоговый преобразователь, содержащий источники тока, матрицы резисторов, ключи и источник опорного напряжения .1 J .

Недостатком устройства является сложность и низкая линейность выходной характеристики в точках, где изменяются значения старших разрядов входной величины.

Известен также цифро-аналоговый преобразователь, содержащий регистр входы которого подключены к входным шинам устройства, сумматор, три декодирующих преобразователя и ис точник аналогового напряжения, выход которого подключен к аналоговым входам первого и второго декодирующих преобразователей, выходы которых соединены с входами третьего декодирующего преобразователя, выход которого через сумматор подключен к выходу устройства 23

Однако известное устройство имеет недостаточно высокую линейность и быстродействие из-за того, что при изменении кодов старших разрядов входной величины происходит переключение на выходах как первого, так и второго декодирующих преобразователей..

Цель изобретения - повышение линейности выходной характеристики преобразователя и повышение быстродействия.

Поставленная цель достигается, тем, что в цифро-аналоговый преобразователь, содержащий регистр, входы которого подключены к входным шинам устройства, сумматор, три декодирующих преобразователя и источник аналогового напряжения, выход которого подключен к аналоговым входам первого и. второго декодирующих преобразователей, выходы которых соединены с входами третьего декодирующего преобразователя, выход которого через сумматор подключен к выходу устройства, введены два блока преобразователей кодов и дополнительный ра.зрядный элемент, первый и второй

аналоговые входы которого соединены соответственно с выходами первого и второго декодирующих преобразователей, выход - со вторым вХОПОМ CVMматора, при этом управляющие входы первого декодирующего преобразователя подключены к первым рыходам первого преобразователя кодов, вторые выходы которого соединены с управляющими входами второго декодирующего преобразователя, выходы с первыми выходами регистра, соответствующими старшим разрядам входного кода, вторые выходы регистра, соответствующие младшим разрядам входного кода, подключены к первым входам второго преобразователя кодов, второй вход которого соединен с выходом регисТ-ра, соответствующим наименее значащему из старших разрядов входного кода, и с управляющим входом дополнительного разрядного элемента, а выходы с управляющими входами третьего декодирующего преобразователя.

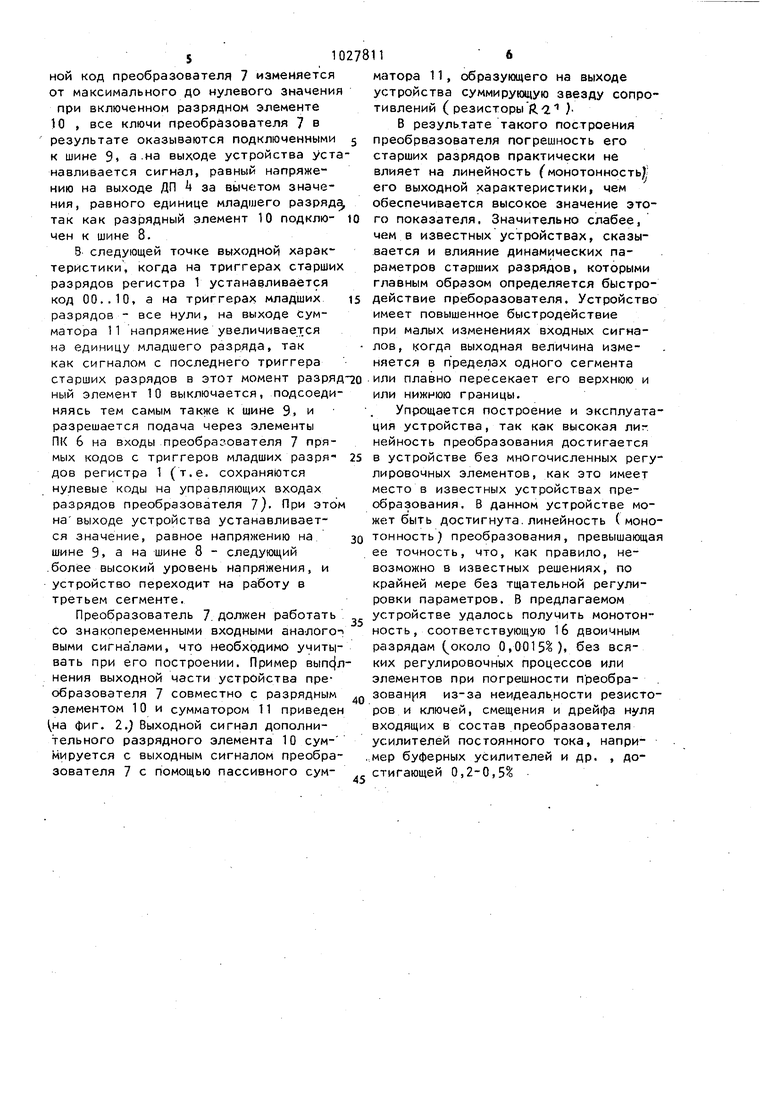

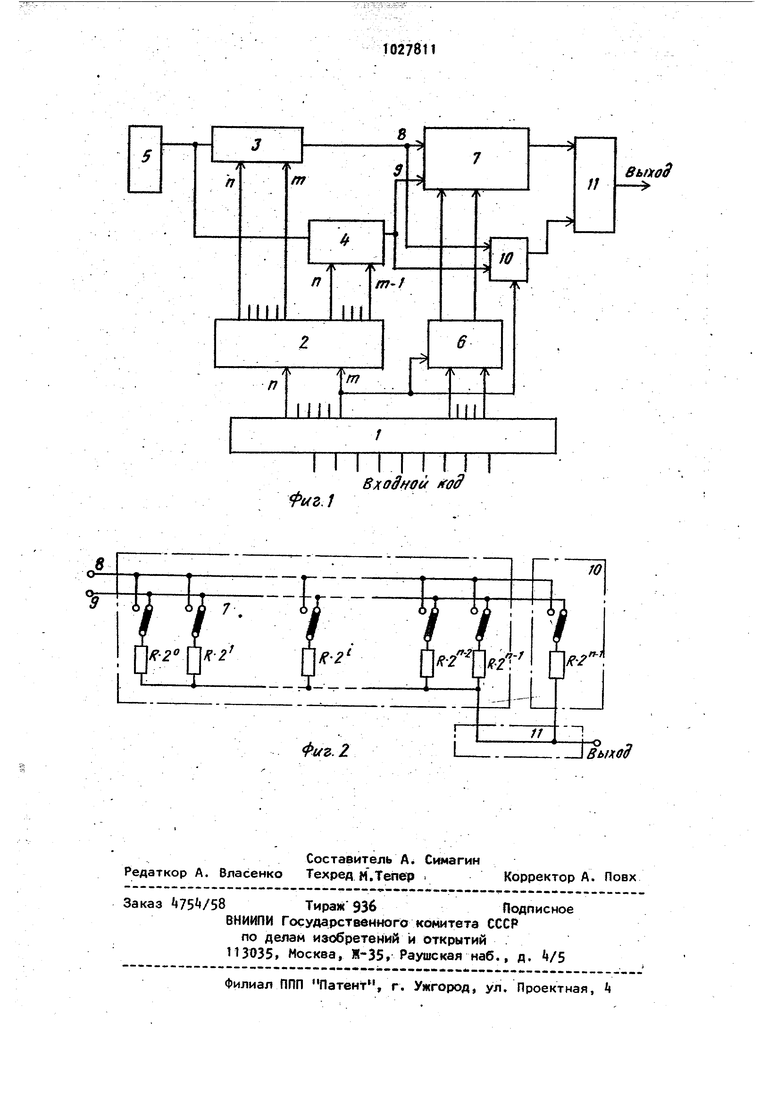

На фиг. 1 представлена структурная схема цифро-аналогового преобразователяг на фиг. 2 - пример принципиальной схема цифро-аналогового Q преобразователя младших разрядов с сумматором и дополнительным разрядным элементом.

Устройство содержит регистр 1, первые выходы которого, соответствующие старшим разрядам входного кода, подключены к первому преобразователю кода 2. Выходы преобразователя

2кодов соединены с управляющими входами первого 3 и второго декодирующих преобразователей, аналоговые входы которых подключены к выходу иисточника 5 опорного напряжения. Вторые выходы регистра 1 соединены через второй Преобразователь 6 кодов

с третьим декодирующим преобразователем 7 входы 8 и 9 которого объединены с входами дополнительного разрядного элемента 10 и .подключены к вы ходам декодирующих преобразователей

3и 4. Выход третьего декодирующего преобравзователя 7 соединен с первым

а выход дополнительного разрядного элемента 10 - со вторым входом сумматора 11, выход которого подключен к выходу устройства. Управляющий 5 вход дополнительного разрядного элемента 10 соединен со вторым входом преобразователя 6 кодов -и выходом регистра 1, который соответствует наименее значащему из старших разрядов входного кода. Устройство работает следующим образом. Входной код поступает на входы регистра 1, с выходов которого К старших разрядов подаются на входы первого преобразователя кодов (ПК-) 2. Если декодирующие преобразовател (ДК) 3 и используют разные систем кодов, то в ПК 2 ос тцествляется пре образование кодов из одной системы в другую (например, из двоичной э позиционную единичную). Если на выходе регистра 1 и на выходах ДП 3 и применяются одинаковые системы кодов, то выходы К-1 старших разрядов регистра 1 подаются на входы ДП 3 без изменения. На вход, соответствюущий младшему .разряду ДП 3 из преобразователя кодов 2 постоянно поступает сигнал, соответствующий уровню 1, при этом на входы ДП постоянно поступает нечетный код. На управляющие входы jfUl подается чеТ ный код. Примем к значению кода К старших разрядов, поступающего на вход ПК 2, прибавляется единица. При использовании на входе ДП k дво ичных кодов на его вход подается кО старших К-1 разрядов полученной сум мы, т.е. всегда четная величина. Таким образом, с помощью ДП 3 и выбирается часть диапазона (сегмент выходного сигнала устройства, соответствующая единице- наименее значащего из старших разрядов кода, поступающих на вход ПК 2. Сигналы с вы ходов ДП 3 и определяют границы этих- сегментов, причем ДП 3 задает верхнюю границу нечетного и нижнюю границу четного ceгмeнтoв a ДП k нижнюю границу нечетного и верхнюю границу четного сегмента. Сигналы с выходов ДП 3 и 4 подаются в качес ве опорных на аналоговые входы ДП J Код с выходов регистра 1, соотве ствующих младшим разрядам входного кода, поступает на входы ПК 6, который, если код в-старших К разрядах является четным, без изменения передает код на входыДП 7 или форм рует на своих выходах обратный код, если код в старших К разрядах нечет ный. Для исключения погрешности, ра ной единице младшего разряда, возни кающей при смене входного кода ,с пря мого на обратный, используется дoпoлнитeJJlьный разрядный элемент 10, величина выходного сигнала которого равна величине сигнала, соответствующего младшему разряду ДП 7. На входы сумматора 11 поступают выходные сигналы ДП 7 и разрядного элемента 10, при этом на выходе сумматора 11 формируется аналогвоый эквивалент входного кода устройства. Рассмотрим работу преобразователя на примерах перехода выходной величины из первого сегмента во второй и из второго в третий. В пределах первого сегмента, когда на К старших триггерах регистра 1 записан код 00..00, на аналоговые входы 1ЦП 1 (шины 8 и 9) с выходов ДП 3 и поступают сигналы соответственно первого и нулевого уровней напряжения. С увеличения кода младших разрядов регистра 1 отдельные разрядные элементы преобразователя 7 (фиг. 2) переключаются от шины 9 к шине 8. .И когда на всех триггерах младших разрядов регистра 1 установятся единичные значения, все ключи разрядов преобразователя 7 окажутся подключенными к шине 8. На выходе сумматора 11 при этом установится сигнал, равный напряжению на выходе ДП 3 за вычетом значения, равного единице младшего разряда. В следующей точке выходной характеристики на К триггерах старших | разрядов регистра 1 установится код 00..р1, а на триггерах младших разрядов.- все нули. При этом одновременно .сигналом с последнего триггера старшего разряда разрешается прохождение через ПК 6 на входы преобразователя 7 обратных кодов с триггеров младших разрядов регистра 1 т.е. сохраняются единичные значения сигналов на входах разрядов преобразователя 7 , и включается разрядный элемент 10. Таким образом, при одновременном изменении состояния всех триггеров младших разрядов меняется управляющий сигнал только на входах разрядного элемента 10, и выходной сигнал устройства становится равным напряжению на входной шине 8. На входной шине тем же сигналом с послед него триггера старших разрядов устанавливается новое значение напряжения соответствующее верхней границе второго .сегмента. С дальнейшим увеличением кода на триггерах младших разрядов регистра 1 от всех нулей до всех единиц входной код преобразователя 7 изменяется от максимального до нулевого значения при включенном разрядном элементе 10 , все ключи преобразователя 7 в результате оказываются подключенными к шине 9. а.на выходе устройства уста навливается сигнал, равный напряжению на выходе ДП k за значения, равного единице младшего разряду так как разрядный элемент 10 подключен к шине 8. 5 следующей точке выходной характеристики, когда на триггерах старших разрядов регистра 1 устанавливается код 00..10, а на триггерах младших разрядов - все нули, на выходе Сумматора 11 напряжение увеличивается на единицу младшего разряда, так как сигналом с последнего триггера старших разрядов в этот момент разряд ный элемент 10 выключается, подсоединяясь тем самым также к щине 9, и разрешается подача через элементы ПК 6 на входы преобразователя 7 прямых кодов с триггеров младших разрядов регистра 1 (т.е. сохраняются нулевые коды на управляющих входах разрядов преобразователя 7). При это на выходе устройства устанавливается значение, равное напряжению на шине 9, а на шине 8 - следующий .более высокий уровень напряжения, и устройство переходит на работу в третьем сегменте. Преобразователь 7. должен работать со знакопеременными входными ана-лого выми сигналами, что необхрдимо учиты вать при его построении. Пример выпс:|л нения выходной части устройства преобразователя 7 совместно с разрядным элементом 10 и сумматором 11 приведен на фиг. 2.) Выходной сигнал дополнительного разрядного элемента 10 суммируется с выходным сигналом преобра зователя 7 с помощью пассивного сумматора 11, образующего на выходе устройства суммирующую звезду сопротивлений ( резисторы И.-2 } В результате такого построения преобрвазователя погрешность его старших разрядов практически не влияет на линейность (монотонность/ его выходной характеристики, чем обеспечивается высокое значение этого показателя. Значительно слабее, чем в известных устройствах, сказывается и влияние динамических параметров старших разрядов, которыми главным образом определяется быстродействие преборазователя. Устройство имеет повышенное быстродействие при малых изменениях входных сигналов, когда выходная величина изменяется в пределах одного сегмента или плавно пересекает его верхнюю и или нижнюю границы. Упрощается построение и эксплуатация устройства, так как высокая лигнейность преобразования достигается в устройстве без многочисленных регу лировочных элементов, как это имеет место в известных устройствах преобразования. В данном устройстве может быть достигнута, линейность Смонотонность} преобразования, превышающая ее точность, что, как правило, невозможно в известных решениях, по крайней мере без тщательной регулировки параметров. В предлагаемом устройстве удалось получить монотонность, соответствующую 16 двоичным разрядам (около 0,0015) без всяких регулировочных процессов или элементов при погрешности преобразова у я из-за неидеаль.ности резисторов и ключей, смещения и дрейфа нуля входящих в состав преобразователя усилителей постоянного тока, например буферных усилителей и др. , достигающей 0,2-0,5

вьпод

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Цифроаналоговый преобразователь | 1983 |

|

SU1152091A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1562971A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1984 |

|

SU1259492A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1971 |

|

SU322777A1 |

| Устройство для преобразования сигналов информационно-измерительной системы | 1982 |

|

SU1062751A1 |

ггт I :т I I I I / Фиг. 2

Bxodffou ffoS . I BbixaS

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| .Мохофф И | |||

| Изготовление эффективных преобразователей данных в виде монолитных интегральных схем | |||

| Электроника, 1979, № Ю, с | |||

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США W 3997892, DA, кл | |||

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1983-07-07—Публикация

1981-01-11—Подача