Изобретение отноеится к области автоматизаци нронзводствснных нроцессов и может быть иснользовано в системах цифрового проrpaiMMHoro уиравления станками для преобразования двоичио-десятичного кода программоносителя в двоичный код системы н для вычисления нонравок к занрограммироваиной эквидистанте. Устройство применяется в системах унравления, использующих встроенный линейно-круговой интерполятор с оценочной функцией.

Известны устройства для вычисления поправок к запрограммирова)1ной эквидистанте, а также устройства для преобразования двоично-десятичного кода программоносителя в двоичный КОД системы.

Известные устройства коррекции эквидистанты требуют для реализации большого количества оборудования, включающего линейный интерполятор с оценочной фу}1кцней для вычисления поправок к запрограммированной эквидистанте и специального устройства для определения момента окончания вычисления поправок.

В устройствах коррекции эквидистанты и устройствах для перевода двоично-десятичного кода в двоичный коэффициент загруженности их сложного оборудования очень ннзко. Так онерации по преобразованню кода осуществляются лингь в короткие интервалы времени

при вводе И1формации в снстему, а операции

по вычислению коррекции в пределах сотен

импульсов занн.мают мельще 10 м-сек. Вместе

с тем количество оборудования, необходимого

для перевода кодов и вычисления коррекции,

обычно в несколько раз презосходнт объем

оборудования, необходимого для построе1П я

интерполятора.

Предлагаемое устройство нозволяет уменьщцть количество оборудоваиня, необходимого для реализации операций но преобразованию двоично-десятичного кода программоносителя в двоичный код системы п оборудования, необходимого для вычисления поправок к запрограммированпой эквидистанте.

Сущность изобретения заключается в том, что преобразование двоично-десятичного кода программоносителя в двоичпый код и вычисление поправок к эквндистанте выполнены на

одном и том же оборудовании, для чего преобразователь входной информации содержит две дополнительные схемы параллельной передачи кодов, триггер с раздельными входами, две схемы совпаде 1ия и генератор тактовых

нмнульсов, иричем выходы дополнительных схем передачи кодов соединены со входами сумматора, одн входы этих схем соединены соответственно с .менными выходами триггера и с одними входами схем совпадения,

кодов соединены с выходами запоминающих регистров, а их третьи входы соединены с выходом генератора тактовых импульсов, который также Подсоединен к других входам схем совпадения и через элемсит задержки - к нулевому входу триггера, единичный вход которого соединен с выходом переполнения параллельного сумматора.

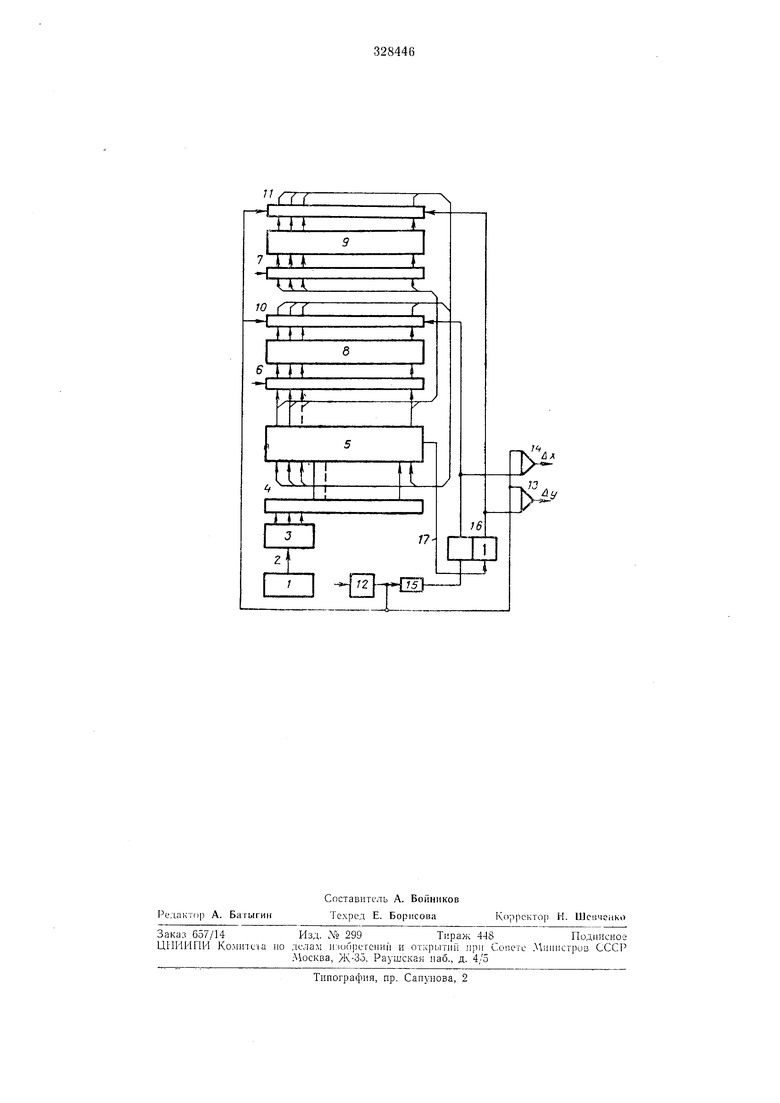

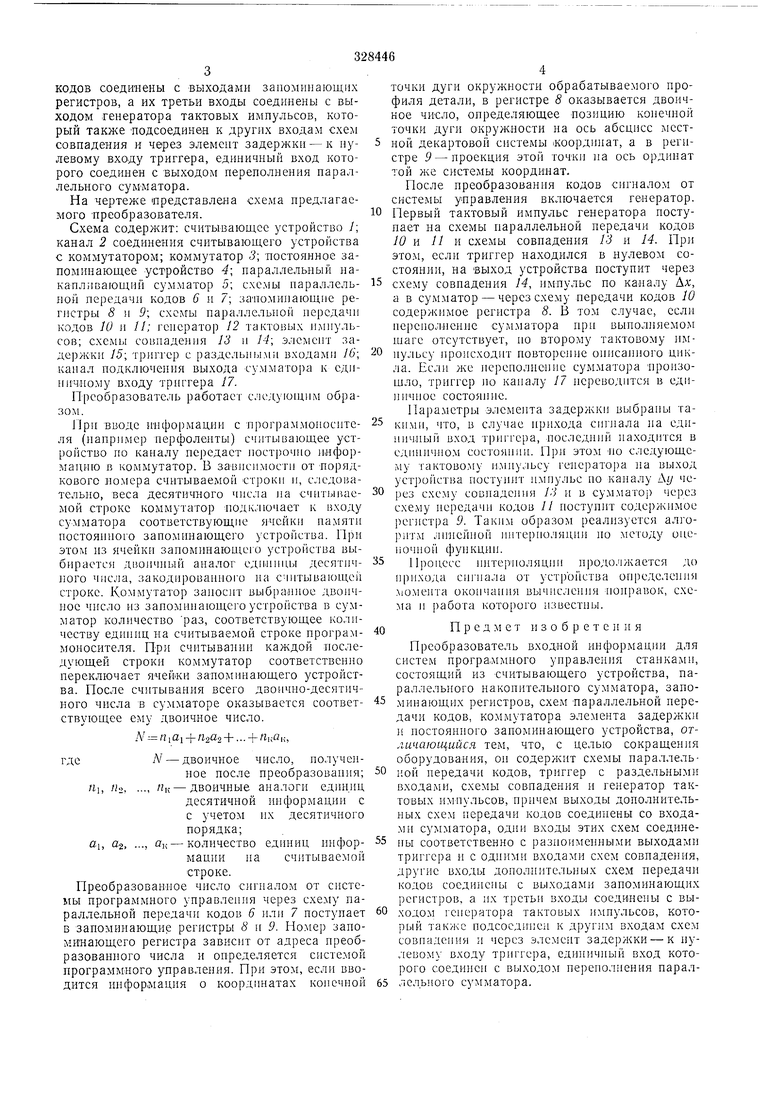

На чертеже представлена схема предлагаемого Преобразователя.

Схема содержит: считывающее устройство /; канал 2 соединения считывающего устройства с коммутатором; коммутатор 3; постоянное запоминающее устройство 4 параллельный накапливающий сумматор 5

схемы параллельной передачи кодов 6 и 7 запо.мипающие регнстры 8 и 9; схемы пар кчлельиой иередачи кодов 10 и //; генератор 12 тактовых импульсов; cxejMbi совпадения 13 и 14; элемсит задержки 15; триггер с раздельными входами 16; канал подключения выхода сумматора к единичному входу триггера 17.

Преобразователь работает слсдуюидим образом.

При вводе информации с ирограммоиосителя (иаиример перфоленты) считывающее устройство по каналу иередает построчно ннформаиию в коммутатор. В за зисимости от порядкового номера считываемой строки и, следовательно, веса десятичного числа па считываемой строке коммутатор тюдк тючает к входу сумматора соответствующие ячейки памяти постоянного заноминающего устройства. При этом из ячейкн заноминающего устройства выбирается двоичный аналог едииицы десятичного числа, закодированно1о на сч1ггывающей строке. Коммутатор занос1гт выб)аиное двоичное число из запоминающего устройства в сумматор количество раз, соответствующее количеству единиц на считываемой строке программоносителя. При считывании каждой носледующей строки коммутатор соответственно переключает ЯчеЙ1КИ запоминающего устройства. После считывания всего двоичио-десятичного числа в сумматоре оказывается соответствующее ему двоичное число.

jV riiai + n2a2 + ...-f «кОн,

гдеЛ - двоичное число, полученное после преобразования; «1, Но, ..., «к - двоичные аиалоги едингщ десятичной 1Н формации с с учетом их десятичного порядка;

GI, uz, ..., OK - количество единиц ииформации иа считываемой строке.

Преобразоватшое число сигналом от системы программного управления через схему параллельной передачи кодов 6 или 7 поступает в запоминающие регистры 8 и 9. Помер запоминающего регистра зависит от адреса преобразованного числа и оиределяется системой программного управления. При этом, если вводится инфорамация о координатах конечной

точки дуги окружности обрабатываемого ирофиля детали, в регистре 8 оказывается двоичное число, онределяющее нозицию конечной точки дуги окружности на ось абсцисс местной декартовой системы координат, а в регистре 9 - проекция этой точки иа ось ординат той же системы координат.

После иреобразования кодов сигналом от системы управления включается генератор.

Первый тактовый импульс генератора поступает на схемы иараллельной передачи кодов 10 и 11 и схемы совпадения 13 и 14. При этом, если триггер находился в нулевом состоянии, на ВЫХОД устройства поступит через

схему совнадения 14, имиульс по каналу Дл;, а в сумматор - через схему иередачи кодов 10 содержимое регистра 8. В том случае, если переиолненне сумматора нрн выиол 1яемом шаге отсутствует, но второму тактовому нмпульсу происходит новтореиие оиисанного цикла. Если же неренолпеиие сум.матора произошло, триггер но каиалу 17 переводится в едпии чиое состоянне.

Пара.метры элемента задержки выбраны такими, что, в случае нрихода сигиала iia единичный вход триггера, цоследню находится в едииичио.м состояиии. При этом но следующему тактово.му имиульсу генератора на выход устройства ностушгг имиульс но каналу А;/ через схему совпадения 13 и в су.м.мато) через схе.му иередачи кодов 11 ностунит содержимое регистра 9. Таким образом реализуется алгоритм линейиой 1И1териоляц11и но методу оненочиой фуикции.

Процесс интериолящи продо.11жается до прихода сигиала от устройства оиределеиия момента окончания вычисления нонравок, схема и работа которого известиы.

Предмет изобретения

Преобразователь входной информации для систем ирограммиого унравления станками, состоящий из считывающего устройства, параллельного накопительного сум.матора, запоминающих регистров, схем параллельной передачи кодов, коммутатора эле.мента задержки и постоянного заноминающего устройства, отличающийся тем, что, с целью сокращения оборудования, он содержит схемы нараллельнон передачи кодов, триггер с раздельными входами, схемы совнадения и генератор тактовых имиульсов, иричем выходы дополнительиых схем нередачи кодов соединены со входами сумматора, одни входы этих схем соединены соответственно с разноименными выходами

триггера и с одиими входами схем совпадения, другие входы дополнительных схем передачи кодов соединеиы с выходами запоминающн.к регистров, а их т)етьи входы соединены с выходом геиератора тактовых импу«тьсов, который также подсоед1И ен к другим входам схем совпадеиия и через элемент задержки - к нулевому входу триггера, единичный вход которого соедииен с выходом неренолнения парал

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство для измерения параметров газовых сред | 1980 |

|

SU894527A1 |

| УСТРОЙСТВО для ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1973 |

|

SU369561A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

| ЦИФРОВАЯ СЕЙСМОРАЗВЕДОЧНАЯ СТАНЦИЯ | 1973 |

|

SU396648A1 |

| Отсчетное устройство | 1974 |

|

SU548858A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

Даты

1972-01-01—Публикация