1

Изобретение относится к области автоматического управления и предназначено для использования в системах числового программного управления многокоординатными металлообрабатывающими станками..

Известны многокоординатные системы числового программного управления, содержаш:ие последовательно соединенные считывающий узел, входной регистр и коммутатор входной информации, один выход которого через шифратор адреса нолупостоянного запоминающего устройства (ЗУ) и узел полупостоянного запоминающего устройства связан с арифметико-логическим узлом, второй выход через щифратор адреса оперативного ЗУ - также с арифметико-логическим узлом, третий выход через дещифратор функций - с индикаторами номера кадра и номера инструмента, а четвертый - с дешифратором кодов алгоритмов, пульт оператора, соединенный с входным регистром, соответствующий выход которого через узел контроля входной информации связан со считывающим узлом, выходной коммутатор, вход которого соединен с арифметико-логическим узлом, который связан с коммутатором входной информации, и узел контроля выполнения технологических команд.

Однако эти системы имеют узкую область применения и невысокую надежность.

Предлагаемая система отличается тем, что она содержит узел приоритетов, узел выдачи управляющих воздействий и узел контроля, коррекции и резервирования, причем узел приоритетов соединен со считывающим узлом, коммутатором входной информации, узлом микропрограммного управления, узлом полупостоянного запоминающего устройства, узлом контроля выполнения технологических команд, арифметико-логическим узлом, дешифратором кодов алгоритмов и узлом выдачи управляющих воздействий, соответствующие входы которого подключены к пульту оператора и узлу микропрограммного управления, а выход - к выходному коммутатору, узел контроля, коррекции и резервирования подсоединен к арифметико-логическому узлу.

Благодаря этому расщиряется область применения и повышается надежность работы системы.

Кроме того, узел приоритетов содержит коммутатор очередности, входы которого связаны с дешифратором кодов алгоритмов и узлом микропрограммного управления, а выходы - с двумя регистрами заявок и регистром алгоритмов шага, выходы регистров заявок соединены с регистром алгоритмов шага, к входам которого подсоединены шины коммутатора опроса и тактирующая схема, а выходы соединены с управляющими входами

шифратора адресов, выходы тактирующей схемы подсоединены к шифратору адреса и регистру-счетчику, связанным с входами первой схемы сравнения, выход которой подключен к тактирующей схеме, соединенной с регистрами заявок, коммутатором опроса, регистром адреса группового оператора, регистром времени, считывающим узлом, коммутатором входной информации, узлом микропрограммного управления, узлом контроля выполнения технологических команд и с второй схемой сравнения, к входам которой подключены выходы узла выдачи управляющих воздействий и регистра времени, связанного с выходами узла полупостояпного запоминающего устройства, которые подключены также к регистру адреса группового оператора, соединенного с узлом микропрограммного управления, и регистру-счетчику, соединенному с арифметикологическим узлом.

Узел выдачи управляющих воздействий содержит счетчики шагов по координатным осям, выходы которых связаны с управляющими шинами первого дешифратора, матрицу коэффициентов скорости, входы которой связаны с выходами дешифратора, регистр скорости, выходы которого соединены со счетчиком периода управляющих воздействий, связанным по выходу с собирательной схемой, первый счетчик номера скорости связан через схемы совпадения с вторым счетчиком номера скорости, причем выходы обоих счетчиков соединены со схемой сравнения, второй дешифратор, входы которого связаны с выходами второго счетчика номера скорости, а выходы - с матрицей скорости и пути, двоичный счетчик изменения номера скорости, выходы которого через собирательные схемы связаны с входом схемы совпадения, выход которой соединен с входами первого счетчика номера скорости.

Узел контроля, коррекции и резервирования содержит схему расширения оснований, выполненную в виде каскадно соединенных групп модифицированных матриц сложения, входы которых связаны с арифметико-логическим узлом, а выходы с первыми входами матриц вычитапия, вторые входы матриц вычитания соединены с арифметико-логическим узлом, а их выходы - со схемой сравнения, выход которой через последовательно соединенные регистр адреса поправок, пассивную таблицу и параллельный регистр связан с коммутатором модульных каналов и арифметико-логическим узлом.

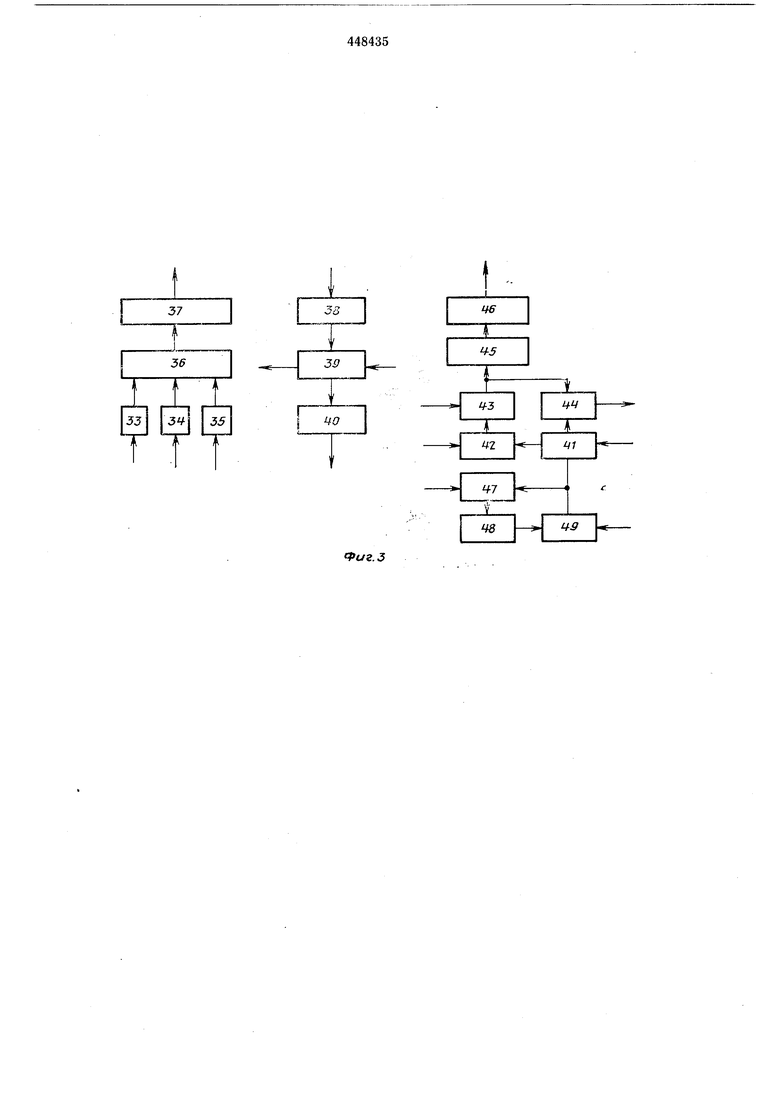

На фиг. 1-4 показаны блок-схемы описываемой системы и ее функциональных узлов.

Блок-схема содержит считывающий узел 1, входной регистр 2, коммутатор 3 входной информации, узел 4 контроля входной информации, пульт 5 оператора, шифратор 6 адреса полупостоянного ЗУ, шифратор 7 адреса оперативного ЗУ, узел 8 выдачи управляющих воздействий, арифметико-логический узел 9, дешифратор 10 функций, дешифратор 11 кодев алгоритмов, узел 12 микропрограммного управления, индикатор 13 номера кадра, индикатор 14 номера инструмента, индикатор 15 перемещения, выходной коммутатор 16, узел 17 связи с приводами, узел 18 полупостояпного запоминающего устройства, узел 19 контроля выполнения технологических команд, узел 20 контроля, коррекции и резервирования, узел 21 приоритетов, коммутатор 22 очередности (фиг. 2), регистры 23 заявок, регистр 24 алгоритмов щага, тактирующую схему 25, коммутатор 26 опроса, шифратор 27 адреса, схему 28 сравнения, регистр-счетчик 29, регистр 30 адреса группового оператора, схему 31 сравнения, регистр 32 времени, счетчики 33, 34 и 35 шагов (фиг. 3), дешифратор 36, матрицу 37 коэффициентов скорости, регистр 38 скорости, счетчик 39 периода управляющих воздействий, собирательную схему 40, первый счетчик 41 номера скорости, схему 42 совпадения, второй счетчик 43 номера скорости, схему 44 сравнения дешифратор 45, матрицу 46 скорости и пути, счетчик 47 изменения номера скорости, собирательную схему 48, схему 49 совпадения, схему 50 расширения основания (фиг. 4), группы матриц 51 сложения, матрицы 52 вычитания, схему 53 сравнения, регистр 54 адреса поправок, пассивную таблицу 55, параллельный регистр 56 и коммутатор 57 модульных каналов.

Система работает следующим образом.

Входная информация о перемещениях и командах поступает со считывающего узла 1 во входной регистр 2. В пего же с пульта 5 поступает информация о режимах работы, скорости подачи, величинах коррекций на длину и радиус инструмента. С входного регистра коммутатор 3 входной информации распределяет информацию по узлам: информацию об алгоритмах посылает в дешифратор кодов алгоритмов; информацию о номере кадра, номере инструмента и скорости шпинделя - в дешифратор функции, числовую информацию о перемещениях - в преобразователь в систему остаточных классов (СОК) арифметикологического узла 9; команды о перемещениях-в шифратор адреса оперативного запоминающего устройства; информацию об операторах- в шифратор адреса полупостоянного запоминающего устройства и в узел 4 контроля. Из дещифратора кодов алгоритмов информация об алгоритмах в кадре в виде кодовых признаков поступает в узел 21 приоритетов. Из дешифратора вспомогательных и других функций информация подается на индикаторы номера кадра, номера инструмента и на исполнительные механизмы станка.

Информация о конце ввода кадра и строки поступает от коммутатора входной информации в узел приоритетов, позволяя ему тактировать считывающий узел. Индикация перемещений осуществляется индикатором 15, на который поступают данные после преобразования в арифметико-логическом узле. 5 Набор и последовательность групповых операторов и кодов, определяющих время их выполнения, хранятся в узле 18. В нем хранятся также количество групповых операторов по каждому алгоритму, номер ячейкиs полупостоянного запоминающего устройства, в которой записан состав данного алгоритма и номер ячейки оперативного запоминающего устройства, закрепленной за данным алгорит oj -10Информация об алгоритмах, выполняемых в каждом кадре программы, поступает на шифратор 6, формулирующий адрес полупостоянного запоминающего устройства, по которому хранится содержание алгоритма.15 Часть этого содержания - адрес оперативного запоминающего устройства, соответствующии данному адресу полупостоянного запоминающего устройства, а также число, определяющее количество групповых операторов20 в алгоритме, переписываются по указанному адресу в оперативное запоминающее устройство арифметико-логического узла. В узле контроля контролируется вводимая информадия по длине слова и на четность25 пробивок в строке перфоленты. При наличии сбоя считывающий узел останавливается сигналом от узла контроля. Так как обработка операндной информации производится в СОК. то вводом в оперативное запоминающеезо устройство арифметико-логического узла информация преобразуется из двоично-десятичного кода в СОК в арифметико-логическом узле. Адрес ячейки оперативного запоминающего устройства формируется шифратором 7.35 Обработка операндной информации о перемещениях производится параллельными oneрациями над модульными частями от целочисленных операндов с помощью арифметикелогического узла. В соответствии с выбран-40 ным по приоритету групповым оператором узел приоритетов управляет узлом 12, переключающим структуру модульного арифметико-логического узла и формирующим процесс вычисления. Результаты обработки one-45 рандной информации направляются в выходной коммутатор 16, который опрашивается в периоды выдачи управляющих воздействий .узлом выдачи управляющих воздействий. Коммутатор 16 управляет узлом 17 связи с50 .приводами станка. Обработка и выдача информации в системе зависит от выполнения отдельных технологических команд. Контроль за их выполнением55 осуществляется узлом контроля выполнения технологических команд, связанным входом со станком, а выходом с узлом приоритетов. Так как система функционирует в реальном масштабе времени, для обеспечения макси-60 мальной загрузки всех функциональных узлов системы предусмотрен режим разделения машинного времени. Организация режима разделения времени осуществляется узлом 21 приоритетной реализацией алгоритмов.65 6 В отличие от общепринятых методов дуплексного или тройного резервирования в си„еме введено 30%-ное резервирование путем использования ее модульной организации при функционировании в непозиционной системе счисления остаточных классов. Для этого служит узел контроля коррекции и резервирования модульных каналов, выявляющий дефектный модульный канал и управляющий заменой его резервным. узел приоритета работает следующим образомПри вводе информации очередного кадра признаки алгоритмов с дешифратора алгоритмое (фиг. 1) поступают на коммутатор очередности (фиг. 2), который направляет эту информацию на вход того из регистров зая алгоритмов, который содержит признаки основных алгоритмов, выполняемых в следующем кадре. На второй вход коммутатора очередности поступает коммутирующий сигнал микропрограммного управления. Этот ,g коммутатор управляет перезаписью, приз„,0 алгоритмов из регистров заявок алгоритмов в регистр алгоритмов шага Переза„д ь осуществляется после окончания каждого Приоритет алгоритмов определяется поразрядным опросом регистра 24, очередность разрядов в котором говорит о приоритетном размещении алгоритмов, выраженных бинар„ ми признаками Поразрядный опрос проводится в каждом начиная со старших разрядов регистра 24, т. е. с самых главных по приоритету алгоритмов. Опрос осуществляется коммутатором 26 с предельной частотой схемных элементов дд момента обнаружения первого единичного признака алгоритма. В момент выявления признака алгоритма в коммутатор опроса поступает сигнал наличия заявки, прекращающ„й опро, останавливающий коммутатор на номере этого разряда регистра 24 с тем чтобы последующий опрос в данном шаге осуществлялся с разряда, на котором произошел останов. Одновременно с остановом коммутатора 26 „а вход шифратора адресов алгоритмов в оперативное запоминающее устройство поступает выявленный сигнал заявки, вызывая на выходе шифратора код адреса оперативного запоминающего устройства. Этот код подается на схему 28 сравнения, на вторые входы котоpgg подается адрес предыдущего алгоритма, храняющийся в регистре-счетчике 29, в котором, кроме адреса алгоритма, записано, количество выполняемых групповых операторов. Резуль аты сравнения поступают на вход тактирующей схемы 25. В случае совпадения кодов выполняется предыдущий алгоритм и пз регистра количества групповых операторов поступает на узел 18 код адреса следующего группового оператора этого же алгоритма. После этого содержимое ячейки полупостоянного запоминающего устройства по этому адресу переписывается в регистры 30 и 32.

В случае несовпадения кодов из тактирующей схемы подаются сигналы на регистр-счетчик и шифратор 27, по которым содержимое регистра-счетчика переписывается в оперативное запоминающее устройство арифметикологического узла по адресу, содержащемуся в этом регистре. Далее регистр-счетчик очищается, а в него из оперативного запоминающего устройства по адресу, поступившему из шифратора 27, записываются данные следующего, нового алгоритма. Эти данные из регистра-счетчика записываются в полупостоянное запоминающее устройство в качестве адреса, по которому из этого устройства поступают на регистры 30 и 32 номер очередного группового оператора и время его выполнения. В регистре-счетчике после выполнения каждого группового оператора происходит вычитание единицы из количества операторов. Это позволяет определять очередность выполнения групповых операторов и вызов из полупостоянного запоминающего устройства их признаков (номер и время выполнения) в регистры 30 и 32. Число, определяющее время выполнения группового оператора в тактах, из регистра 32 поступает на схему 31 сравнения, на второй вход которой из узла 8 поступает величина времени, оставшегося до конца шага интерполяции.

Если время выполнения группового оператора меньше оставшегося до конца шага, на схему 25 поступает сигнал, разрешающий выполнение данного группового оператора. По этому сигналу схема 25 вырабатывает сигнал, поступающий на вход регистра 30 и разрещающий считывание номера группового оператора в узел 12. Если время реализации группового оператора больще оставшегося до конца шага, поступает сигнал, запрещающий выполнение данного алгоритма.

Схема 25 вырабатывает сигнал, воздействующий на регистры 29, 32 и 30, устанавливающий их в начальное состояние. Одновременно появляется сигнал, воздействующий на коммутатор 26, о продолжении опроса регистра 24, определяющего следующий алгоритм. Содержание выбранного алгоритма через шифратор адреса вызывается из оперативного запоминающего устройства арифметико-логического узла в регистр 29, а затем по содержанию из полупостоянного запоминающего устройства в регистр 30 номер очередного группового оператора, а в регистр 32 - время его выполнения.

При выполнении технологических команд узел приоритета начинает функционировать после их окончания. Сигналы о выполнении технологических команд поступают от станка на узел контроля выполненных команд, а с него по запросу узла приоритета - на схему 25.

После выполнения микропрограммы очередного группового оператора из узла микропрограммного управления на тактирующую схему подается сигнал окончания данного

группового оператора, по которому из схемы 25 поступает сигнал уменьшения на единицу количества групповых операторов в регистресчетчике 29.

5 Если после уменьшения на единицу количество групповых операторов не равно нулю, т. е. алгоритм еще не выполнен, схема 25 посылает сигнал установки коммутатора 26 в исходное, состояние и осуществляются опрос заявок и определение приоритета для следующего группового оператора. Если после уменьшения на единицу количество групповых операторов становится равным нулю, что определяет окончание данного алгоритма, сигналом 15 от схемы 25 снимается заявка на выполнение этого алгоритма.

При выполнении всех заявок кадра из одного из регистров 23 поступает сигнал на схему 25, по которому вырабатывается сигнал пуска 0 считывающего узла. Информация о прохождении каждой строки перфоленты и окончании считывания кадра подается с коммутатора входной информации на схему 25 узла приоритета.

5 Узел выдачи управляющих воздействий работает следующим образом.

Номер скорости, который задан в данном кадре обработки, поступает из оперативного запоминающего устройства арифметико-логи0 ческого узла в двоично-десятичный счетчик 41. Так как скорости подачи задаются на перфоленте своими номерами, изменение скорости с пульта производится изменением номера скорости. Целочисленная величина изменения но5 мера скорости заносится с пульта оператора в трехразрядный вычитающий двоичный счетчик 47 изменения номера скорости. Тактовые импульсы, поступающие от схемы 49, сбрасываIQT счетчик 47 в нуль и одновременно поступа0 ют на вход счетчика 41, изменяя его содержимое. В момент равенства содержимого счетчика 47 нулю прохождение тактовых импульсов сигналом, поступающим из схемы 48, запрещается. В счетчике 41 сохраняется изменен5 ный номер скорости. Такой процесс изменения номера скорости происходит в каждом новом кадре.

Код номера скорости со счетчика 41 поступает через схему 42 совпадения (вторые вхо0 ды которой управляются узлом 12) на второй счетчик 43 номера скорости. Двоичные счетчики 33, 34 и 35 шагов, связанные с выходным коммутатором 16, подсчитывают количество шагов вдоль координатных осей. При перепол5 нении одного или нескольких счетчиков щагов дешифратор 36 разрешает считывание с матрицы 37 величины соответствующего коэффициента скорости, код которого с выхода поступает в арифметико-логический узел 9. Одновременно со считыванием коэффициентов с матрицы 37 разрешается обращение к матрице 46 скорости и пути по сигналу из узла 12 микропрограммного управления. Величина заданной скорости, записанная в матрице 46 в системе остаточных классов, умножается в арифметико-логическом узле на выбранный из матрицы 47 коэффициент и заносится (после преобразования в код со смешанными основаниями) в регистр 38 скорости. Из счетчика 39 импульсами тактовой частоты начинают вычитаться единицы до момента равенства его содержимого нулю. В момент равенства содержимого счетчика 39 нулю выдается разрешение на выдачу управляюшего воздействия из выходного коммутатора 16 на узел связи с приводом станка. После этого в счетчик 39 вновь переписывается содержимое регистра скорости,и процесс повторяется. Управление контурной скоростью при разгоне и торможении осуш;ествляется следующим образом. По признаку разгона увеличивается содержимое второго счетчика 43 номера скорости на единицу. Величина новой скорости и величина времени отработки пути с этой скоростью с матрицы 46 передаются в арифметико-логический узел, где они в результате перемножения образуют величину ступени пути, который система числового программного управления должна отработать с новой скоростью. В каждом такте интерполяции эта величина пуТи сравнивается с величиной перемешения по максимальной координате. В момент равенства величины пути и перемеш,ения по максимальной координате выдается разрешение на переход к следующему номеру скорости, для чего содержимое счетчика 43 увеличивается вновь на единицу и т. д. Процесс повторяется до тех пор, пока схема 44 сравнения не выдаст сигнал равенства текущей скорости, номер которой хранится в счетчике 43, и конечной скорости разгона, номер которой хранится в счетчике 41. Этот сигнал запрещает дальнейшее увеличение номера скорости и номера ступени пути. С этого момента в системе осуществляется выдача управляющих воздействий с периодом, соответствующим конечной скорости разгона, заданной на перфоленте. Замедление в системе осуществляется аналогично разгону. По признаку замедления, записанному на перфоленте, разрешается уменьшение содержимого второго счетчика номера скорости на единицу. Величина новой скорости с матрицы скорости заносится в регистр 38, а величина ступени пути с матрицы скорости и пути передается в арифметико-логический узел, где вычитается из пути замедления хранящегося в оперативном запоминающем устройстве арифметико-логического узла. В каждом такте интерполяции эта величина пути сравнивается и перемещением по максимальной координате и при их равенстве формируется разрешение на переход к следующей ступени пути и вновь уменьшается содержимое счетчика 43 и т. д. Процесс заканчивается, когда номер скорости в счетчике 43 становится равным номеру скорости в счетчике 41. Работа узла контроля, коррекции и резервирования происходит следующим образом. При реализации узлом приоритета числового программного управления программного оператора контроля любая элементарная арифметико-логическая операция в системе остаточных классов (СОК), выполняемая с помощью табличных схем сложения, вычитания, умножения, преобразования и сравнивающей схемы, осуществляется одновременно по основным и избыточным модулям СОК. По остаткам для можества путем расширения оснований СОК определяются с помощью схемы 50 два вспомогательных остатка для {гпгс}, из которых в схеме формирования адреса вычитаются остатки по избыточным модулям N+1 - N+e, сформированные в избыточной части регистра арифметико-логического узла. Соответствующие разности между вспомогательными и избыточными остатками |A|jv+t- |А|л+е (при условии, ЧТО обе разности по определению в схеме 53 сравнения не равны нулю) используются в качестве адреса пассивной таблицы 55 поправок. Если только одна из контрольных разностей равна нулю, вспомогательные остатки для {m,v) заменяют избыточные. Текущее значение результирующего операнда считается достоверным и не подлежит корректировке только в случае |А1л.-+г |А|л+р 0. По сформированному адресу из пассивной таблицы 55 в выходной регистр 56 заносится выбранная поправка, которую необходимо сложить по дефектному модулю с ошибочным остатком операнда (двоичный код номера канала указан в этом же выбранном слове). По двоичному коду номера дефектного канала коммутатор 57 разрешает сложение остатка текущего операнда по дефектному модулю и полученной поправки в соответствующей модульной матрице сложения арифметико-логического узла. Результат коррекции принимается за истинное значение остатка по дефектному модулю. Если дефектный модуль дает регулярные сбои при многократном прохождении программного оператора коррекции, коммутатор переключает стационарно дефектный модульный канал на резервный или на один из избыточных. При построении системы числового программного управления на основе двоичной системы счисления, а не СОК организация процесса идентификации и коррекции ошибок, аналогичная использованной, потребовала бы применения проверочных кодов с числом конрольных операций, пропорциональным колиеству разрядов информационной части опеандов, а не числу информационных модулей ОК, что резко снизило бы эффективное бытродействие системы числового программного правления. предмет изобретения 1.Многокоординатная система числового программного управления, содержащая последовательно соединенные считывающий узел, входной регистр и коммутатор входной информации, один выход которого через шифратор адреса полуиостоянного запоминающего устройства и узел полупостоянного запоминающего устройства связан с арифметико-логическим узлом, второй выход через шифратор адреса оперативного запоминающего устройства также с арифметико-логическим узлом, третий выход через дешифратор функций -с индикаторами номера кадра и номера инструмента, а четвертый - с дешифратором кодов алгоритмов, пульт оператора, соединенный с входным регистром, соответствующий выход которого через узел контроля входной информации связан со считывающим узлом, выходной коммутатор, вход которого соединен с арифметико-логическим узлом, а выход - узлом связи с приводами, индикатор перемещения и узел микропрограммного управления, соединенные с арифметико-логическим узлом, который связан с коммутатором входной информации, и узел контроля выполнения технологических команд, отличающаяся тем, что, с целью расширения области применения и повышения надежности работы, она содержит узел приоритетов, узел выдачи управляющих воздействий и узел контроля, коррекции и резервирования, причем узел приоритетов соединен со считывающим узлом, коммутатором входной информации, узлом микропрограммного управления, узлом полупостоянного запоминающего устройства, узлом контроля выполнения технологических команд, арифметико-логическим узлом, дешифратором кодов алгоритмов и узлом выдачи управляющих воздействий, соответствующие входы которогоподключены к пульту оператора и узлу миккропрограммного управления, а выход - к выходному коммутатору, узел контроля, коррекции и резервирования подсоединен к арифметико-логическому узлу. 2.Система по п. I, отличающаяся тем, что узел приоритетов содержит коммутатор очередности, входы которого связаны с дешифратором кодов алгоритмов и узлом микропрограммного управления, а выходы - с двумя регистрами заявок и регистром алгоритмов шага, выходы регистров заявок соединены с регистром алгоритмов шага, к входам которого подсоединены шины коммутатора опроса и тактирующая схема, а выходы соединены с управляющими входами шифратора адресов, выходы тактирующей схемы подсоединены к шифратору адреса и регистру-счетчику, связанным с входами первой схемы сравнения, выход которой подключен к тактирующей схеме, соединенной с регистрами заявок, коммутатором опроса, регистром адреса группового оператора, регистром времени, считывающим узлом, комутатором входной информации, узлом микропрограммного управления, узлом контроля выполнения технологических команд и с второй схемой сравнения, к входам которой подключены выходы узла выдачи управляющих воздействий и регистра времени, связанного с выходами узла полупостоянного запоминающего устройства, которые подключены также к регистру адреса группового оператора, соединенного с узлом микропрограммного управления, и регистру-счетчику, соединенному с арифметико-логическим узлом. 3.Система по п. 1, отличающаяся тем, что узел выдачи управляющих воздействий содержит счетчики шагов по координатным осям, выходы которых связаны с управляющими шинами первого дешифратора, матрицу коэффициентов скорости, входы которой связаны с выходами дешифратора, регистр скорости, выходы которого соединены со счетчиком периода управляющих воздействий, связанным по выходу с собирательной схемой, первый счетчик номера скорости связан через схемы совпадения с вторым счетчиком номера скорости, причем выходы обоих счетчиков соединены со схемой сравнения, второй дешифратор, входы которого связаны с выходами второго счетчика номера скорости, а выходы - с матрицей скорости и пути, двоичный счетчик изменения номера скорости, выходы которого через собирательные схемы связаны с входом схемы совпадения, выход которой соединен с входами первого счетчика номера скорости. 4.Система по п. 1, отличающаяся тем, что узел контроля, коррекции и резервирования содержит схему расширения оснований, выполненную в виде каскадно соединенных групп модифицированных матриц сложения, входы котооых связаны с арифметико-логическим узлом, а выходы - с первыми входами матриц вычитания, вторые входы матриц вычитания соединены с арифметико-логическим узлом, а их выходы - со схемой сравнения, выход которой через последовательно соединенные регистр адреса поправок, пассивную таблицу и параллельный регистр связан с коммутатором модульных каналов и арифметикологическим узлом.

37

56

ТУТ

I5tf

v :

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Цифровая логическая машина | 1974 |

|

SU558278A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

Авторы

Даты

1974-10-30—Публикация

1972-08-10—Подача