(Л

t

СП

о

О5

Изобретение относится к вычислительно технике, а именно к арифметическим устройствам, и может быть использовано в цифровых вычислительных устройствах для быстрого умножения, деления и преобразования шестнадцатиричных и десятичных чисел.

Цель изобретения - расширение Функ1диональнь1х возможностей за счет выполнения операций деления и преоб- j разования.

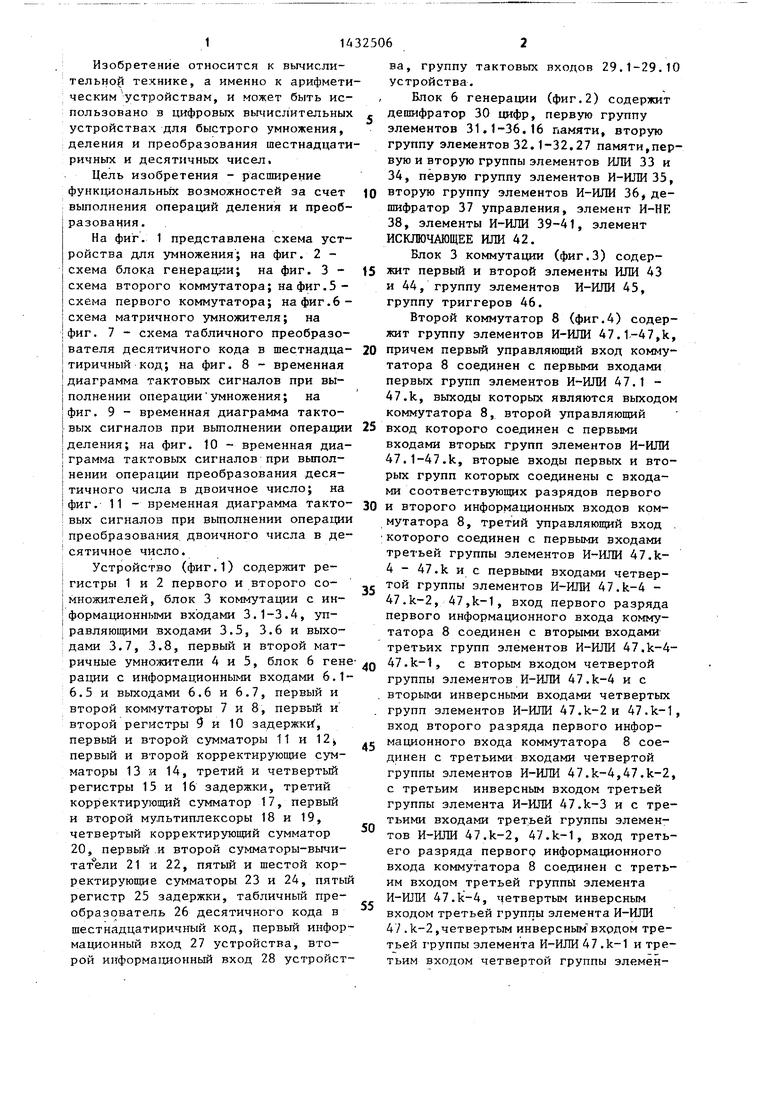

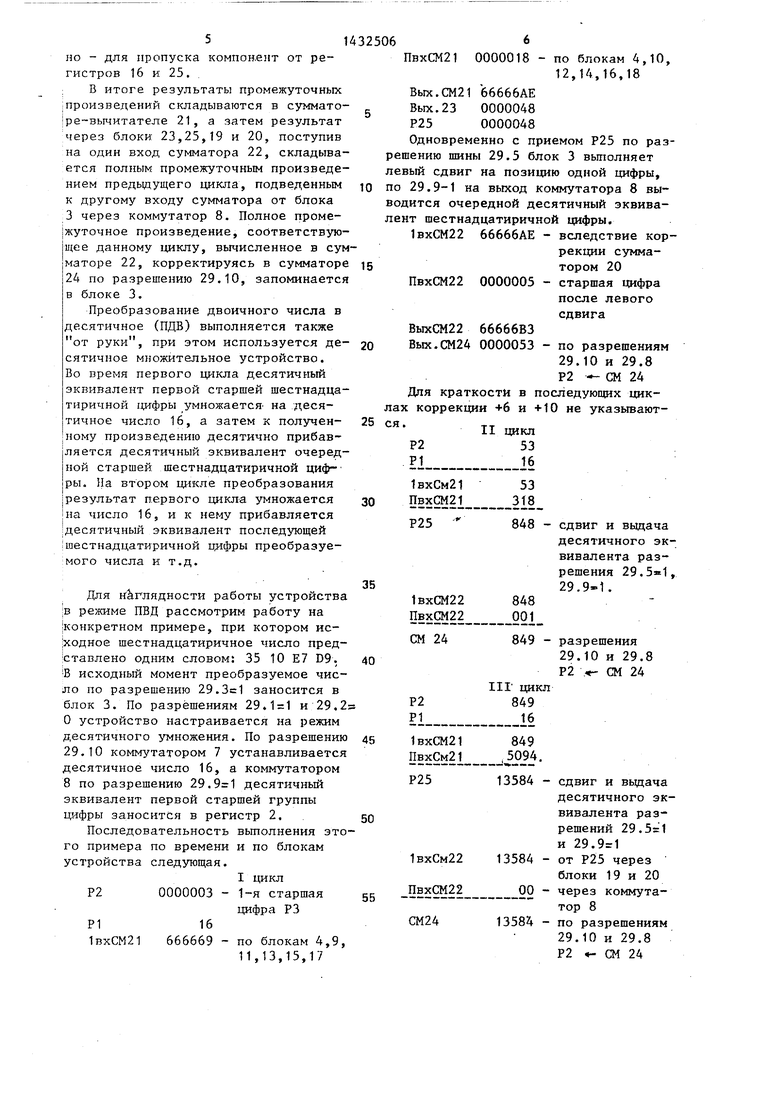

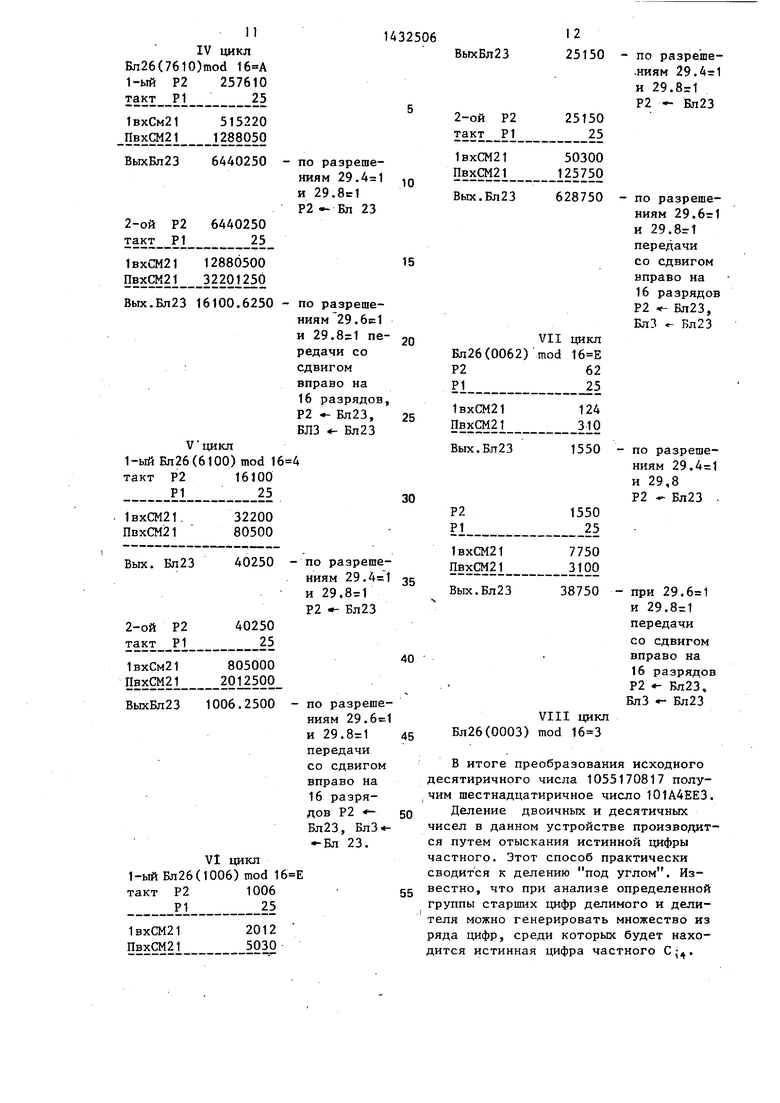

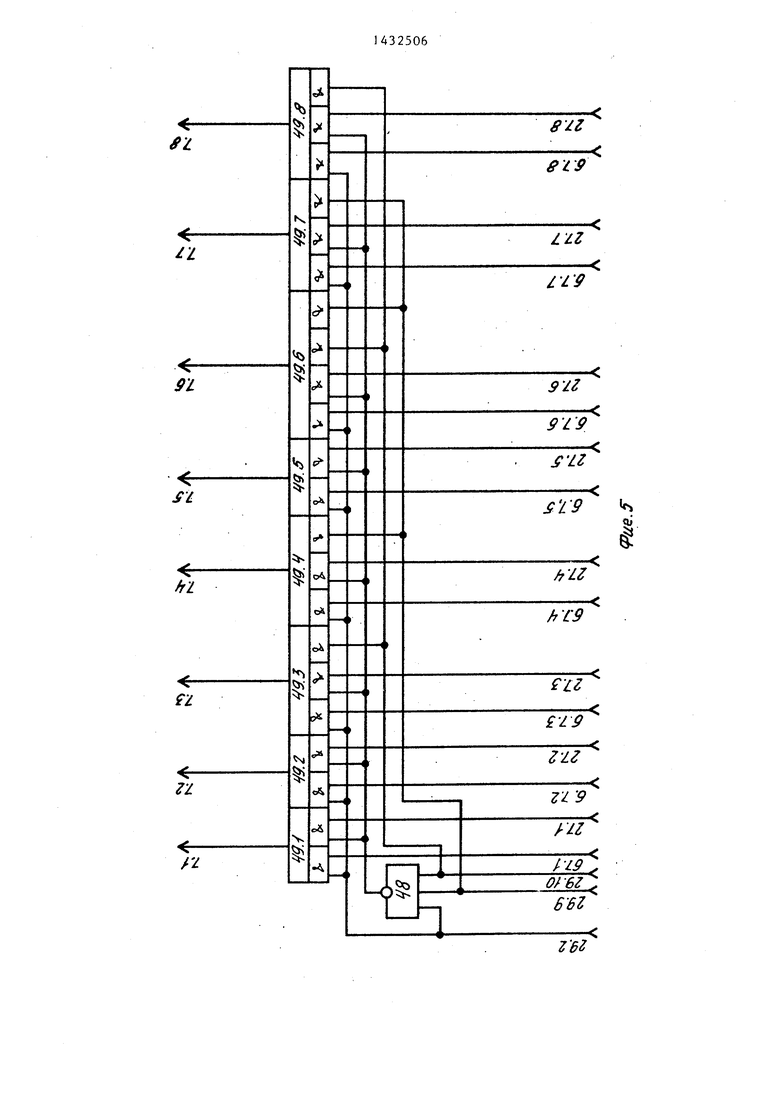

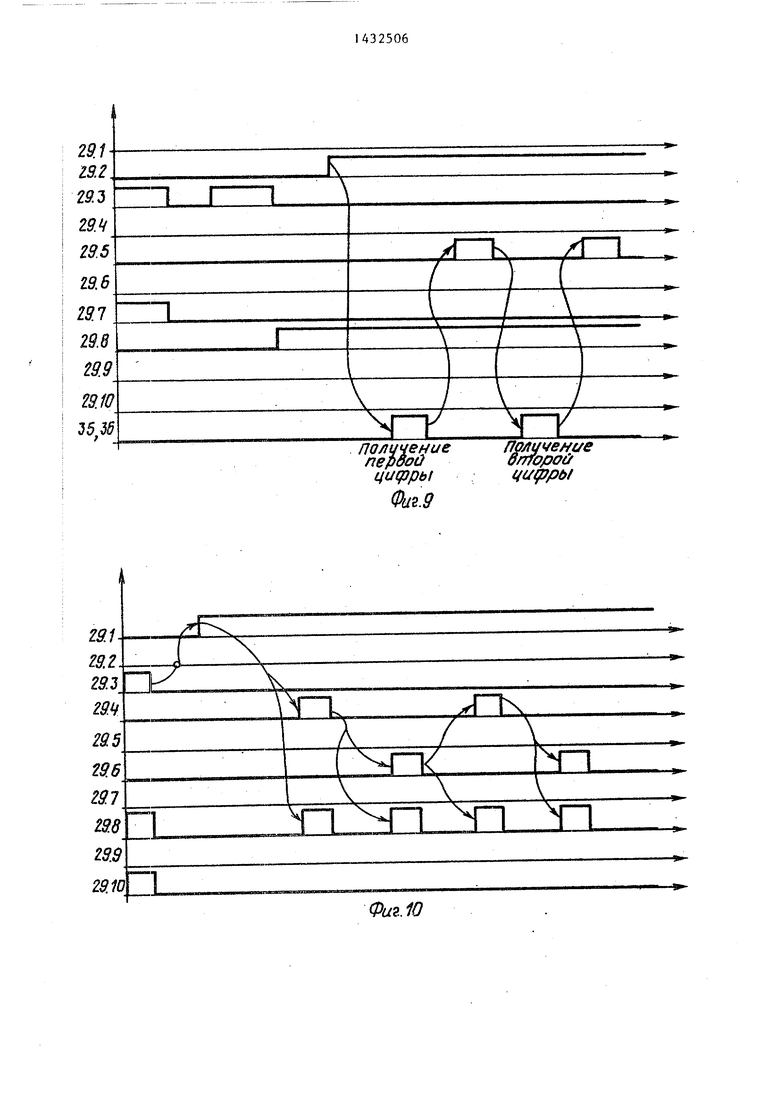

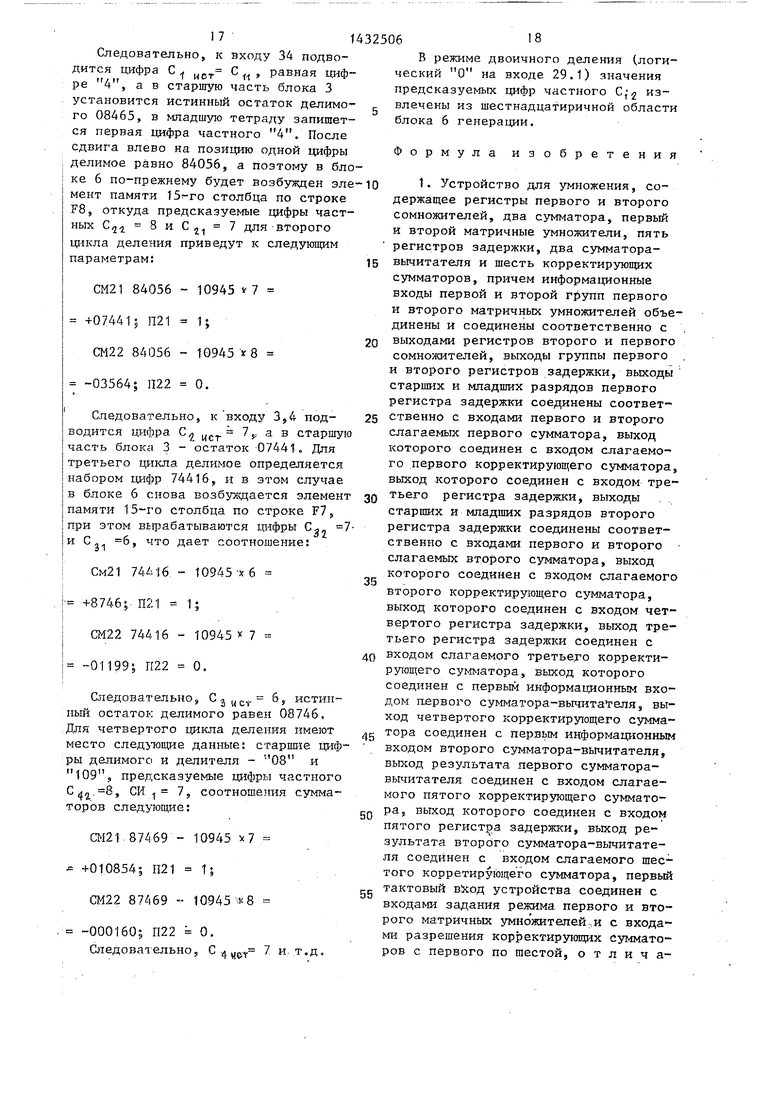

На фиг. 1 представлена схема устройства для умножения; на фиг. 2 - схема блока генерации; на фиг. 3 - I схема второго коммутатора; на фиг.5- I схема первого коммутатора; на фиг.6- I схема матричного умножителя; на 1ФИГ. 7 - схема табличного преобразо- j вателя десятичного кода в шестнадца- jтиричный код; на фиг. 8 - временная I диаграмма тактовых сигналов при вы- I полнении операции умножения; на I фиг. 9 - временная диаграмма такто- вых сигналов при вьтолнении операции I деления; на фиг. 10 - временная диа- I грамма тактовых сигналов при вьшол- I нении операции преобразования деся- Iтичного числа в двоичное число; на 1ФИГ. 11 - временная диаграмма такто- : вь1х сигналов при выполнении операции преобразования двоичного числа в де- :сятичное число.

; Устройство (фиг.1) содержит ре- гистры 1 и 2 первого и второго со- i множителей, блок 3 коммутации с ин- I формационными входами 3.1-3.А, уп- I равлягощими входами 3.5, 3.6 и выхо- : дами 3.7, 3.8, первый и второй матричные умножители 4 и 5, блок 6 генерации с информационными входами 6.1- 6.5 и выходами 6.6 и 6.7, первый и второй коммутаторы 7 и 8, первый и второй регистры 5 и 10 задержк, первый и второй сумматоры 11 и 12 j первый и второй корректирующие сумматоры 13 и 14, третий и четвертый регистры 15 и 16 задержки, третий корректирующий сумматор 17, первый и второй мультиплексоры 18 и 19, четвертый корректирующий сумматор 20, первый и второй сумматоры-вычи- тат ели 21 и 22, пятый и шестой корректирующие сумматоры 23 и 24, пятый регистр 25 задержки, табличный пре- образоватепь 26 десятичного кода в шестнадцатиричный код, первый информационный вход 27 устройства, второй ииформатщоннЕЛЙ вход 28 устройст0

5

0

5

0

5

0

5

0

5

ва, группу тактовых входов 29.1-29.10 устройства.

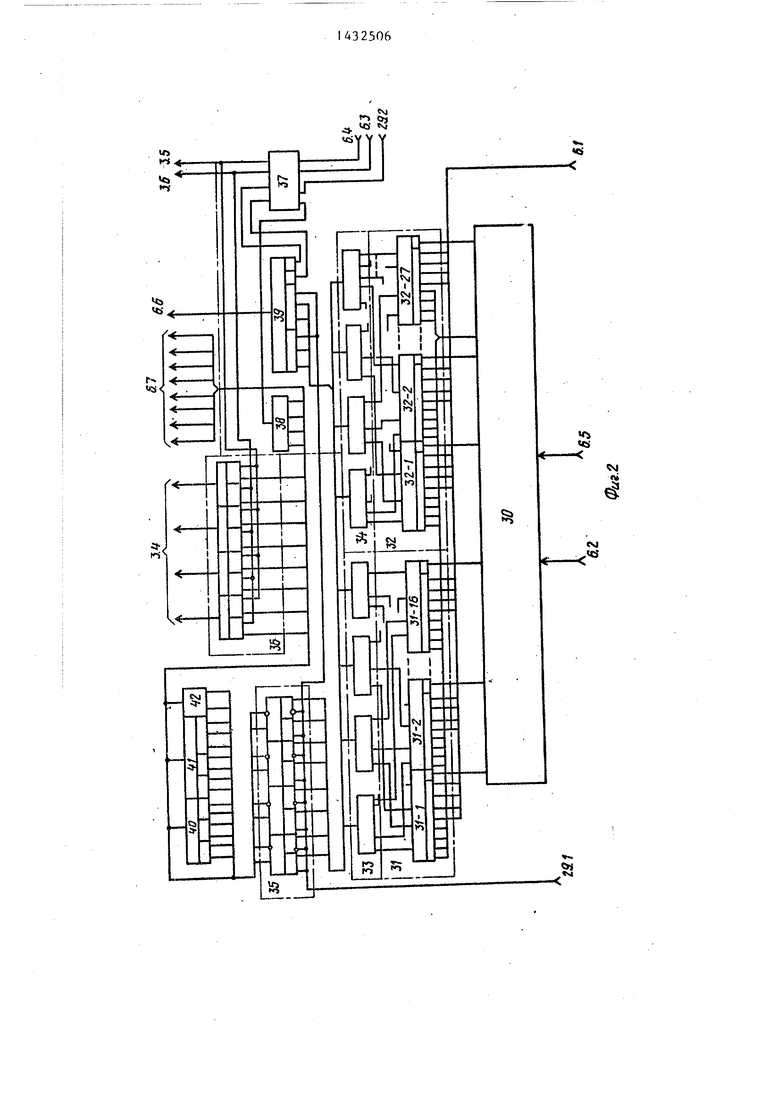

RnoK 6 генерации (фиг.2) содержит дешифратор 30 цифр, первую группу элементов 31,1-36,16 памяти, вторую группу элементов 32,1-32,27 памяти,первую и вторую группы элементов ИЛИ 33 и 34, первую группу элементов И-ИЛИ35, вторую группу элементов И-ИЛИ 36, дешифратор 37 управления, элемент И-НЕ 38, элементы И-ИЛИ 39-41, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 42.

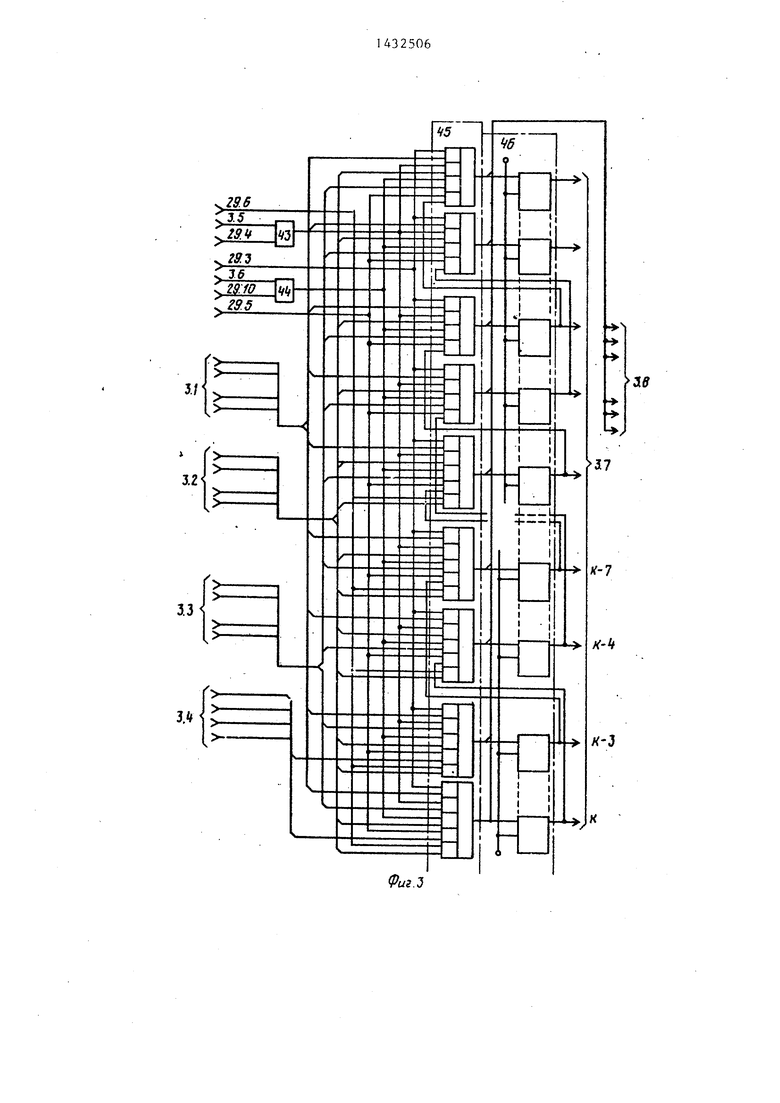

Блок 3 коммутации (фиг.З) содержит первый и второй элементы ИЛИ 43 и 44, группу элементов И-ИЛИ 45, группу триггеров 46.

Второй коммутатор 8 (фиг.4) содержит группу элементов И-ИЛИ 47.1-47,k, причем первый управляющий вход коммутатора 8 соединен с первыми входами первых групп элементов И-ИЛИ 47.1 - 47.k, выходы которых являются выходом коммутатора 8, второй управляющий вход которого соединен с первыми входами вторых групп элементов И-ИЛИ 47.1-47.k, вторые входы первых и вторых групп которых соединены с входами соответствующих разрядов первого и второго информационных входов коммутатора 8, третий управляющий вход , ;которого соединен с первыми входами третьей группы элементов И-ИЛИ 47.k- 4 - 47.k и с первыми входами четвертой группы элементов И-РШИ 47.k-4 - 47.k-2, 47,k-1, вход первого разряда первого информационного входа коммутатора 8 соединен с вторыми входами третьих групп элементов И-ИЛИ 47.k-4- 47.k-1, с вторым входом четвертой группы элементов И-ИЛИ 47.k-4 и с вторыми инверсными входами четвертых групп элементов И-ИЛИ 47.k-2и 47.k-1, вход второго разряда первого информационного входа коммутатора 8 соединен с третьими входами четвертой группы элементов И-ИЛИ 47.k-4,47.k-2, с третьим инверсным входом третьей группы элемента И-ИЛИ 47.k-3 и с третьими входами третьей группы элементов И-ИЛИ 47.k-2, 47.k-l, вход третьего разряда первогр информационного входа коммутатора 8 соединен с третьим входом третьей группы элемента И-ИЛИ 47.k-4, четвертым инверсным входом третьей группы элемента И-ИЛИ 47 .k-2,четвертым инверсным вхрдом третьей группы элемента И-ИЛИ 47 .k-1 и третьим входом четвертой группы элемен

та И-ИЛИ 47.k-1, вход четвертого разряда первого информационного входа коммутатора 8 соединен с вторым входом третьей группы элемента И-ИЛИ A7.k.

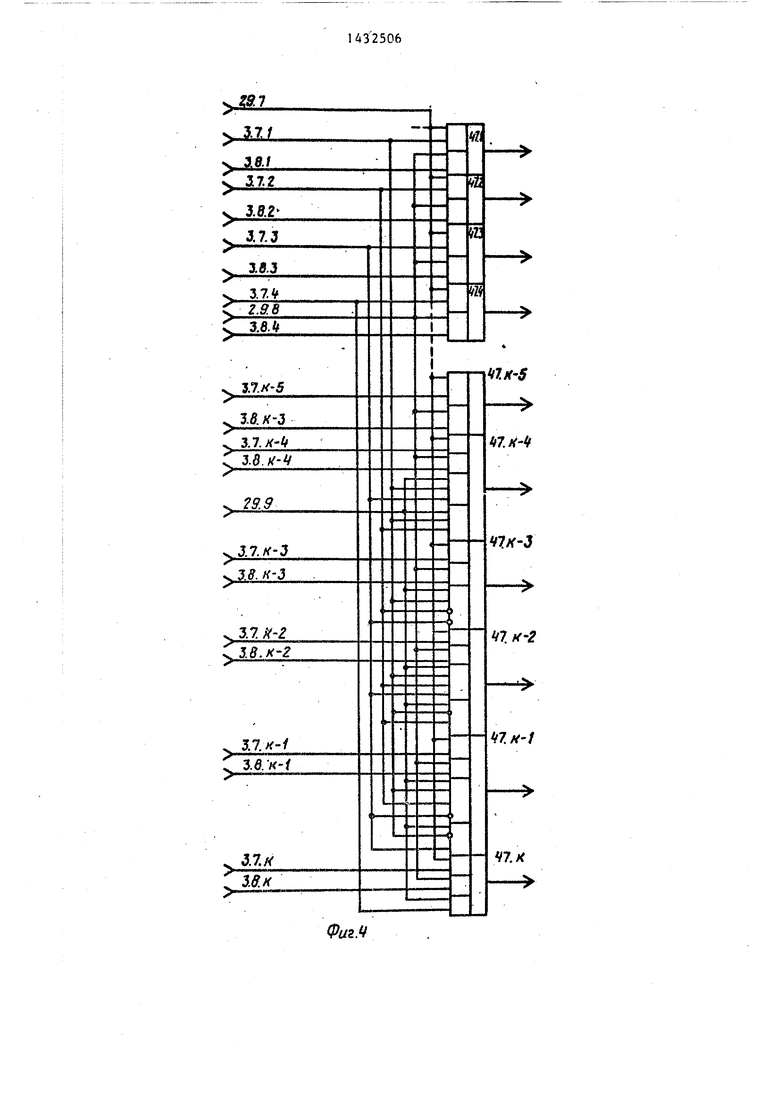

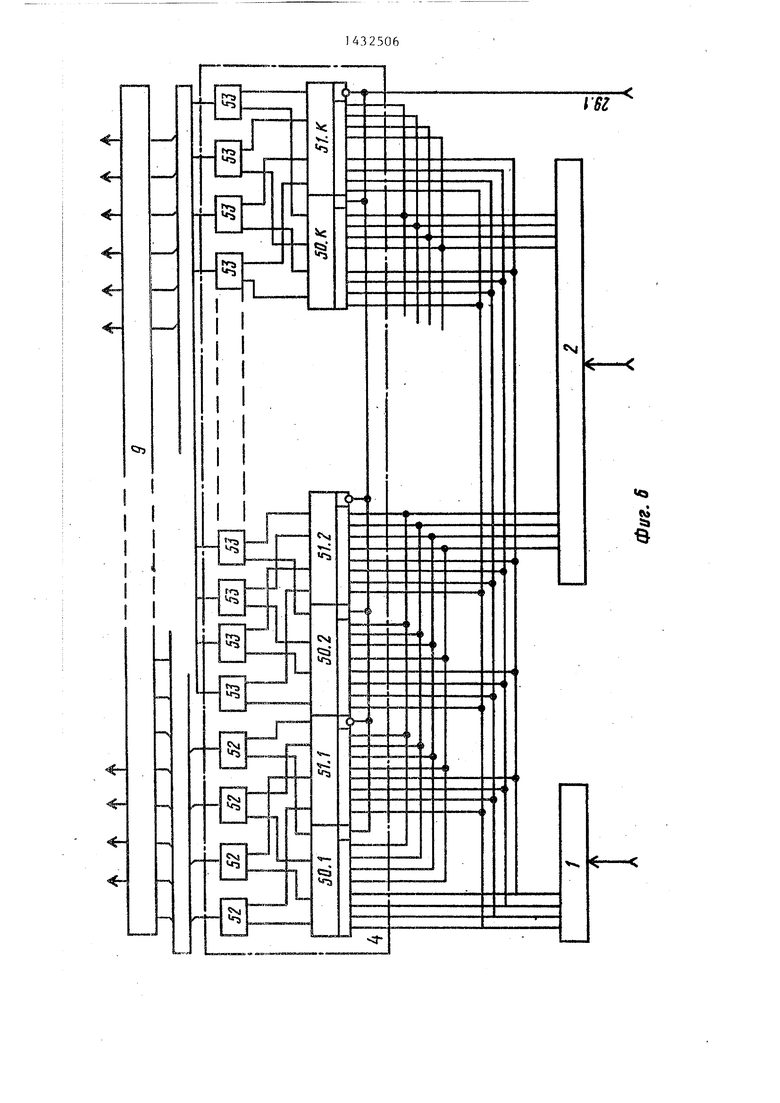

Первый KONfMyTaTop 7 (фиг,5) содержит элемент ИЛИ-НЕ 48 и группу элементов И-ИЛИ 49.1-49.8, причем первый, второй и третий управляющие входы коммутатора 7 соединены соответственно с входами элемента ИЛИ-НЕ 48, первый управляющий вход коммутатора 7 соединен с первыми входами первых групп элементов И-ШТИ 49.1- 49.8, выходы которьрс являются выходо коммутатора 7, выход элемента ИЛИ-Н 48 соединен с первыми входами вторых групп элементов И-ИЛИ 49.1-49.8, вторые входы первых и вторых групп кото рых соединены соответственно с входами разрядой второго и первого информационных входов коммутатора 7, второй управляющий вход которого соединен с входами третьей группы элементов И-ИЛИ 49.4, 49.6, 49.7, третий управляющий вход коммутатора 7 соединен с входами третьих групп.элементов И-ИЛИ 49.3, 49.8 и с входом четвертой группы элемента И-ШТИ 49.6. Матричный умножитель 4 -(фиг.6) содержит первую группу элементов 50.1-50.k памяти, вторую группу элементов 51.1-51.k памяти, первую группу элементов ИЛИ 52, вторую группу элементов ИЛИ 53, причем информационные входы первой группы умножителя 4 соединены соответственно с первыми адресными входами элементов 50.1-50.k, 51.1-51.k памяти, вторые адресные входы которых соединены с информационными входами второй группы умножителя 4, вход задания режима которого соединен с входами раэреше- ния элементов 50.1-50.k памяти и с . входами запрета элементов 51.1-51.k памяти, вькоды соответствующих элементов памяти 50.1-50.k и 51.1-51.k соединены с первыми и вторыми входами элементов ИЛИ 52 и 53 групп, выходы которых являются выходами группы (старшей и мпадшей частей произведения) умножителя 4.

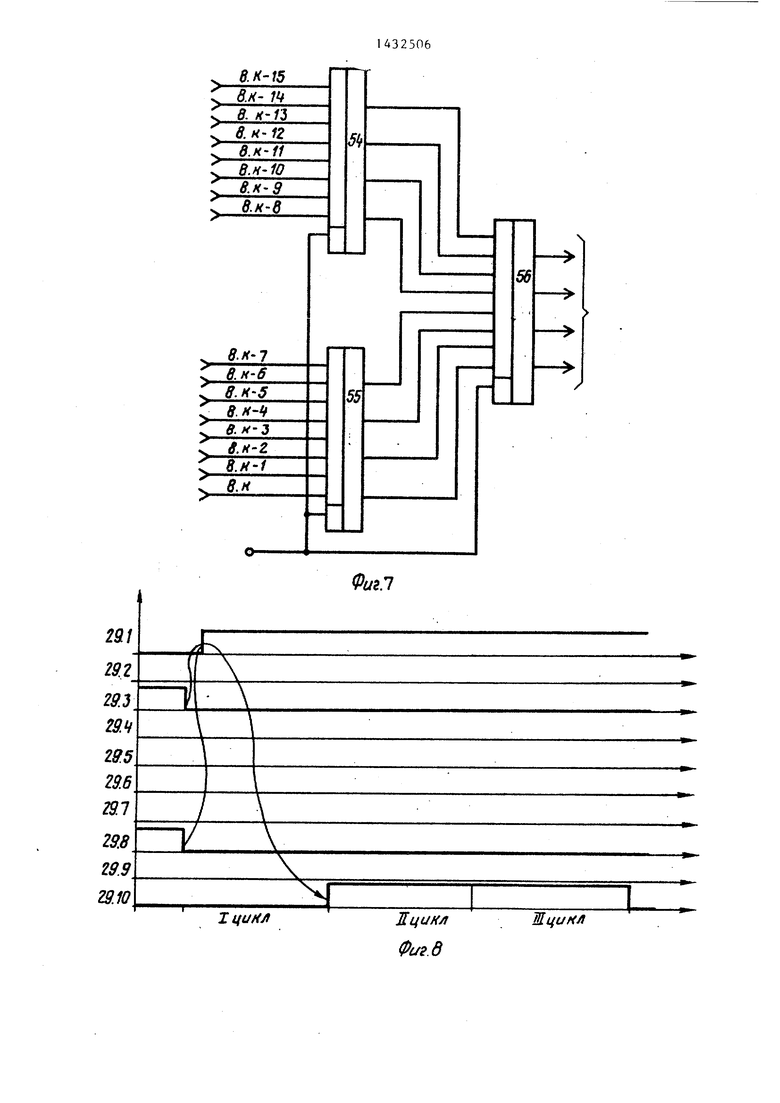

Табличный преобразователь 26 (фиг.7) содержит элементы 54-56 па

мяти, причем входы разрядов преобразователя 26 соединены соответственно с адресными входами элементов 54.и 55 памяти, выходы которых соединены

0

5

5

0

5

0

5

0

5

с адресными входами элемента 56 памяти, выход которого является выходом преобразователя 26. Сумматоры 13,14,23,24 и 17,20 вьтолняют соответственно коррекцию +10 и +6.

Операция умножения производится следующим образом.

В умножителе 4(5) на пересечении шин одной цифры множителя с одной цифрой множимого установлены четыре элемента памяти ППЗУ (постоянное программируемое запоминающее устройст- .во), которые предназначены для вьфа- ботки старшей и младшей компонент (остатков и переносов) шестн дцати- ричного и десятичного произведения. Кодировка элементов памяти производится аналогично прототипу.

Старшая компонента (фиг.6) для десятичного умножения вырабатывается посредством элемента 50.1 памяти, а младшая - посредством элемента 50.2 памяти для двоичного умножения, соответственно элементы 51.1 и 51.2 памяти. В режиме выполнения операций десятичное умножение или деление, преобразование десятичное или двоичное, выдача кодов (фиг.6) производится активизацией десятичной части мат-- рицы посредством логической 1 на входе 29.1, которая одновременно блокирует двоичную часть матрицы. Если же в устройстве инициализировано двоичное умножение или деление, на входе 29.f устанавливается уровень логического О, при котором активизируется двоичная часть матрицы, отключаются все виды коррекции, и в блоке 6 генерации задается разрешение для извлечения предсказуемых цифр частного из области двоичного генератора. На базе компонент произведения, получаемых на выходе умножителя 4,: устройство для умножения посредством блоков 9,11.,13,15,17 и 10,12j14,16 вычисляет соответственно начальные промежуточное произведения, полученные от умножителей старшей и младшей цифр множителя регистра 1 на полный набор множимого, установленного в регистре 2 (фиг.1).

Благодаря тому,что для операции умножения и преобразования на входе 29.2 .установлен уровень логического О, сумматоры-вычитатели 21 и 22 настраиваются на режим сложения, мультиплексоры 18 и 19 соответственно - для пропуска компонент от регистров 16 и 25. .

В итоге результаты промежуточных ;произведений складываются в суммато- ре вычитателе 21, а затем результат через блоки 23,25,19 и 20, поступив на один вход сумматора 22, складывается полным: промежуточным произведением предьщущего цикла, подведенным к другому входу сумматора от блока 3 через коммутатор 8. Полное проме- |жуточное произведение, соответствующее данному циклу, вычисленное в сум |маторе 22, корректируясь в сумматоре |24 по разрешению 29.10, запоминается IB блоке 3.

I Преобразование двоичного числа в десятичное (ПДВ) выполняется также от руки, при этом используется де- сятичное множительное устройство. Во время первого цикла десятичный эквивалент первой старшей шестнадцатиричной умножается- на десятичное число 16, а затем к получен- |ному произведению десятично прибавляется десятичный эквивалент очередной старшей шестнадцатиричной циф- |ры4 На втором цикле преобразования I результат первого цикл-а умножается на число 16, и к нему прибавляется |десятичный эквивалент последующей iшестнадцатиричной цифры преобразуемого числа и т.д.

Для наглядности работы устройства ;В режиме ПВД рассмотрим работу на конкретном примере, при котором ис- ;ходное шестнадцатиричное число пред- |стаБлено одним словом: 35 10 Е7 D9. В исходный момент преобразуемое число по разрешению 29. заносится в блок 3. По разрешениям 29. и 29.2 О устройство настраивается на режим десятичного умножения. По разрешению 29.10 коммутатором 7 устанавливается десятичное число 16, а коммутатором 8 по разрешению 29. десятичный эквивалент первой старшей группы цифры заносится в регистр 2,

Последовательность вьтолнения этого примера по времени и по блокам следующая.

устройства Р2

Р1 1вхСМ21

0000003 16

666669 I цикл

1-я старшая

цифра РЗ

по блокам 4,9, 11,13,15,17

ПвхСМ21 0000018 - по блокам 4,10,

12,14,16,18

ВЫХ.СМ21 66666АЕ

Вых.23 0000048

Р25 0000048

Одновременно с приемом Р25 по разрешению шины 29.5 блок 3 вьшолняет левый сдвиг на позицию одной цифры, по 29.9-1 на выход коммутатора 8 выводится очередной десятичный эквивалент шестнадцатиричной цифры.

66666АЕ 0000005 вследствие коррекции сумматором 20 старшая цифра после левого сдвига

ВЫХСМ22 66666ВЗ ВЫХ.Ш24 0000053

по разрешениям 29.10 и 29.8 Р2 - СМ 24

Для краткости в последующих циклах коррекции +6 и +10 не указываются.

II

Р2 Р1

цикл 53 16

1вхСм21 ПвхСМ21

53 318

Р25

1вхСМ22 ПвхСМ22

848 848001

сдвиг и вьздача десятичного эквивалента разрешения 29., 29.9-1.

СМ 24

849 разрешения29.10 и 29.8

Р2

СМ 24

Р2

Р1

ИГ цикл 849 16

1вхСМ21 ПвхСм21

849 5094.

Р25

13584

сдвиг и вьщача десятичного эквивалента разрешений 29. и 29. 1вхСм22 13584 - от Р25 через

блоки 19 и 20

ПвхСМ2200 - через коммутатор 8

СМ24 13584 - по разрешениям

29.10 и 29.8 Р2 «- СМ 24

Р2 PI

7

IV цикл 00013584 16

13584 8i5g4

217344

0217344 сдвиг и вьщача десятичного эквивалента по разрешениям 29. и 29.

от Р25 через блоки 19 и 20

ПвхСМ22 СМ24

ooogogi 4

217358

Р2 Р1

V цикл 217538 16

1вхСМ21 ПвхСМ21

217358 1304148

3477728 22 3477728 22 0000007

3477735- активизация29., 29..сдвиг влево на 4 разряда. Выдача десятичного эквивалента, от регистра 25 через блоки 19 и 20 десятичный эквивалент цифры 7

по разрешениям 29.10 и 29.8 Р2 СМ24

Р2 Р1

VI цикл 3477735 16

1вхСМ21 3477735 ПвхШ21 20866410

55643760 22 55643760 активизация

29,,

29.,сдвиг

влево, выдача

десятичного

эквивалента

цифры

от Р25 через

блоки 19 и 20

8 ПВХСМ22 00000013 СМ24

55643773 десятичныйэквивалент 1Шфры Д через коммутатор 8 по разрешениям 29. 10 и 28.8 Р2 - СМ24

10

Р2 Р1

VII цикл 55643773 16

5

0

5

0

5

0

5

0

5

1вхСМ21 ПвхСМ21

55643773 333862638

Р25

890300368 1ВХСМ22 890300368

l25CM22 ogoggggo9

СМ24

активизация 29.,сдвиг влево, вьздача десятичного эквивалента от Р25 через блоки 19 и 20

десятичный эквивалент цифры 9

890300377 - по разрешениям 29.10 РЗ - СМ24

Окончанием седьмого цикла заверша- с-тся преобразование одного слова двоичного числа 3510Е709 в десятичное число 890300377.

Преобразование десятичного целого числа в двоичное (ПДЕС) в данном устройстве выполняется путем деления на число 16 и выделением остатка. Деление на 16 при этом заменено умножением на 0.0625, причем каяадый цикл ПДЕС выполняется в течение двух неполных т-актов работы устройства, настроенного на режим десятичного умножения. При выполнении этой операции было использовано известное положение: остаток по модулю 16 для сколь угодно большого десятичного числа равен остатку по модулю 16 от четырех младших цифр этого числа.

Рассмотрим пример ПДЕС для десятичного числа 1055170817.

В исходный момент по разрешениям 29. и 29. десятичное число 1055170817 по входу 28 устанавливается в блок 3 и одновременно в регистр Р2, а вход 29. посредством коммутатора 7 устанавливает десятичную константу 25 в Р1, затем возбуждаются входы, на которых 29.1г1; 29. 29.3-0.

91

Вход 29. активизирует десятичную матрицу в умножителе 4, включает все виды коррекции +6 и +10 в блоках 17, 20 и 13, 14, 24.

Вход 29. настраивает сумматор- рьтитатель 21 на режим сложения и обеспечивает прохождение к его второ biy входу компоненты сложения от ре- ристра 16.

I Так же как и. при вычислениях при- ttepa ПДВ коррекции +6 и +10 не бу- рем указывать.

Временная последовательность действий устройства при вьтолненин это- го примера ПДЕС состоит в следующем.

I щЛсл l-bifi Бл26 (0817 mod

такт Р2 1055170817 Р125.

1вхСМ21

ПвхСМ21

Бл23

2110341634

5275854085 26379270425

по блокам 4, 9,11, 13,15, 17

по блокам 6, 10,12, 14,16, 18

по раз- решениям

29.4Н, 29, Р2 - Вл23

10

Вл 23

II цикл

Бл26(8176) mod 16-

Р265948176

Р125

1ВХСИ21 ПвхСМ21

131896352 329740880

1648704400 Р2 1648704400 Р125

по разрешениям29.4г1, 29. Р2 - Бл23

1вхСМ21 ПВХСМ21

3297408800 8243522000

0

Бл23

4121761.0000 по разрешениям29.6 .и 29. передачи со сдвигом вправо на позицию - два байта Р2 -Вл23, БпЗ Вл23.

III цикл

1-ый Бл26( 1761) mod такт Р2 4121761 Р225

1вхСМ21 8243522 ПвхСМ21 20608805.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Устройство для контроля умножения по модулю три | 1982 |

|

SU1072049A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для деления чисел | 1987 |

|

SU1441388A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления десятичных чисел | 1989 |

|

SU1688239A1 |

| Устройство для деления | 1986 |

|

SU1478212A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЦВМ для быстрого умножения, деления и преобразования. Цель изобретения - расширение функциональных возможностей устройства за счет выполнения операций деления и преобразования. Поставленная цель достигается тем, что устройство для умножения, содержащее регистры 1,2 первого и второго сомножителей, матричные умножители 4,5, регистры 9,10,15,16, 25 задержки, сумматоры 11,12, корректирующие сумматоры 13,14,17,20,23,24, сумматоры-вычитатели 21,22, содержит блок 3 коммутации, блок 6 генерации, коммутаторы 7,8, мультиплексоры 18, 19, табличный преобразователь 26 десятичного кода в шестнадцатиричный код с соответствующими связями. 2з.п. ф-лы, 11 ил., 2 табл.I

по раз- решениям

103044025по разрешениям 29. и 29. Р2 «-БЛ23

2-ой Р2 такт Р1

103044025 25

1вхСМ21 ПвхСМ21

206088050 515220125

л 23

n

IV цикл

Bn26(7610)mod 1-ый P2 257610 такт PI 25

- no разрешениям 29. и 29. P2 - Бл 23

2-ой P2 6440250 такт PI 25

1вхСМ21 ПвхСМ21

12880500 32201250

ых.Бл23 16100.6250 по разрешениям 29.6с:1

и 29. передачи со сдвигом вправо на 16 разрядов, Р2 - Бл23, БЛЗ «- Бл23

V цикл 1-ый Бл26 (6100) mod 16 такт Р216100

Р125

4

1вхСМ21. ПвхСМ21

32200 80500

Бл23

40250 по разрешениям 29. 35 и 29. Р2 - Бл23

2-ой Р2 такт Р1

40250 25

805000 2012500

40

- по разрешениям 29. и 29. 45 передачи со сдвигом вправо на 16 разрядов Р2 - 50 Бл23, -Бл 23.

VI цикл

1-ыйБл26(1006) mod 16 такт Р2 1006 Р1 25

1вхСМ21 ПвхСМ21

2012 5030

ВыхБл23

12 25150

- по разреше- .ниям 29. и 29. Р2 - Бл23

2-ой Р2 такт Р1

25150 25

1вхСМ21 ПвхСМ21

50300 125750

Вых.Бл23

628750 по разрешениям 29. и 29.8г1 передачи со сдвигом вправо на 16 разрядов Р2 - Бл23, БлЗ - Бл23

VIIцикл

Бл26(0062) mod16 Е

Р262

Р125

1вхСМ21 ПвхСМ21

124 310

Вых.Бл23

1550 по разрешениям 29, и 29,8 Р2 -- Бл23 .

при 29. и 29. передачи

со сдвигом вправо на 16 разрядов Р2 - Бл23, БлЗ -- Бл23

VIII цикл Бл26(0003) mod

В итоге преобразования исходного десятиричного числа 1055170817 получим шестнадцатиричное число 101А4ЕЕЗ.

Деление двоичных и десятичных чисел в данном устройстве производится путем отыскания истинной цифры частного. Этот способ практически сводится к делению под углом. Известно, что при анализе определенной группы старших цифр делимого и делителя можно генерировать множество из ряда цифр, среди которых будет находится истинная цифра частного С;.

131432506

чевидно, что значение истинной циф- цифры делителя

но переписаны нераторов путе тирования инфо делимого. Масс тичных цифр ча адреса (делимо бцов (делителя шит) в адресах ного генератор зирующим входа (4-16) десятич соединены выхо торые по разре или 2 подвод делителя из ст или 28, 14 или или 17.

ры частного в обще.м случае зависит от значений всех цифр делителя и стар1иих цифр делимого по количеству, равному или большему на одну цифру от количестна цифр делителя, что Обусловлено соотношениями старших $начимых цифр делимого и делителя. I Для нормализованных двоичных и Десятичных чисел, выравненных по ле- ibiM г-раницам старших эначт-ьпс делимого и дешителя, можно построить Г|1атрицу, генерирующую ряд цифр, в интервале к)торых находится искомая, 1стинная цифра i-ro такта деления j 5 причем если анализировать две тарише цифры делимого и три старшие :фры делителя, разбив его на опре- еленные интервалы весов, можно пред казать значения двух предполагаемых фр частного С , 1 и С-.2, отличаютцих- я друг от друга на единицу, при этом щна из которых будет истинной цифро iiacTHorOo ,

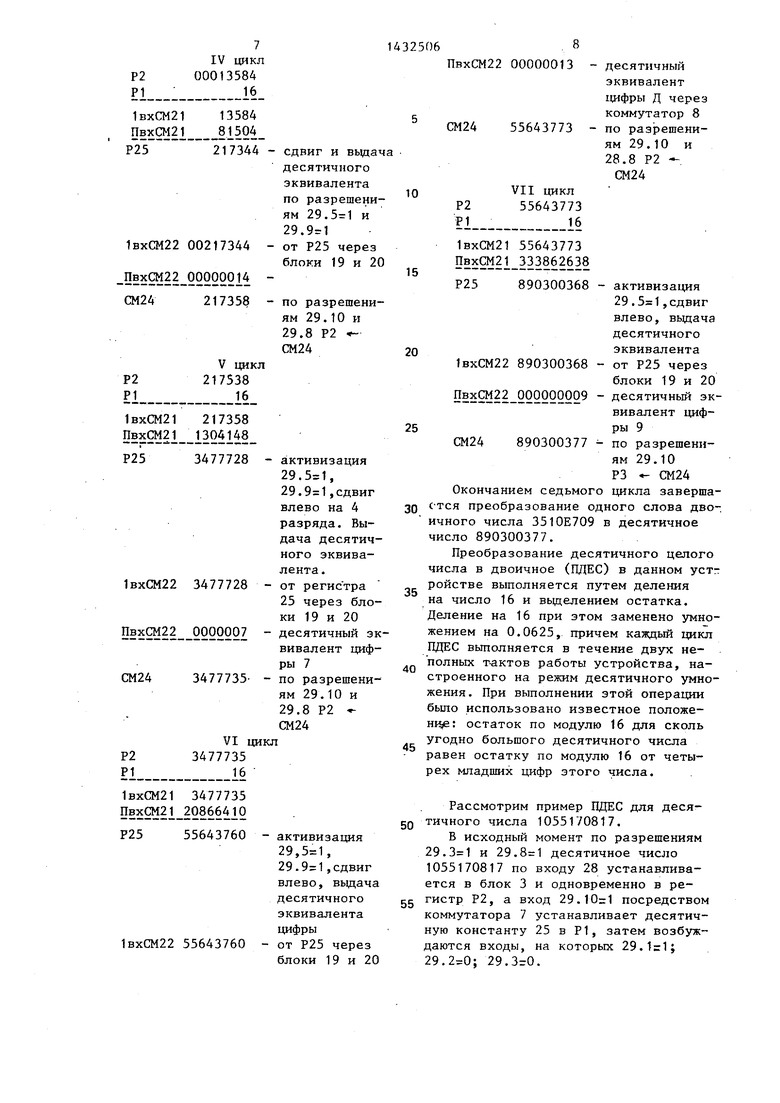

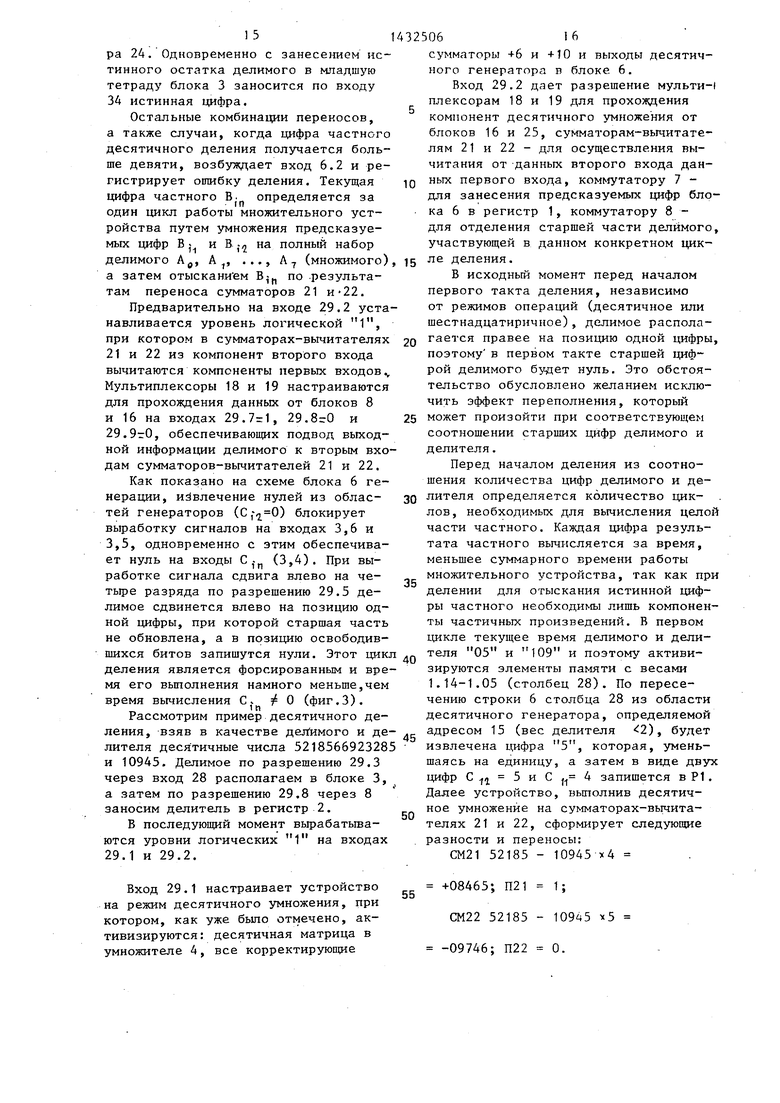

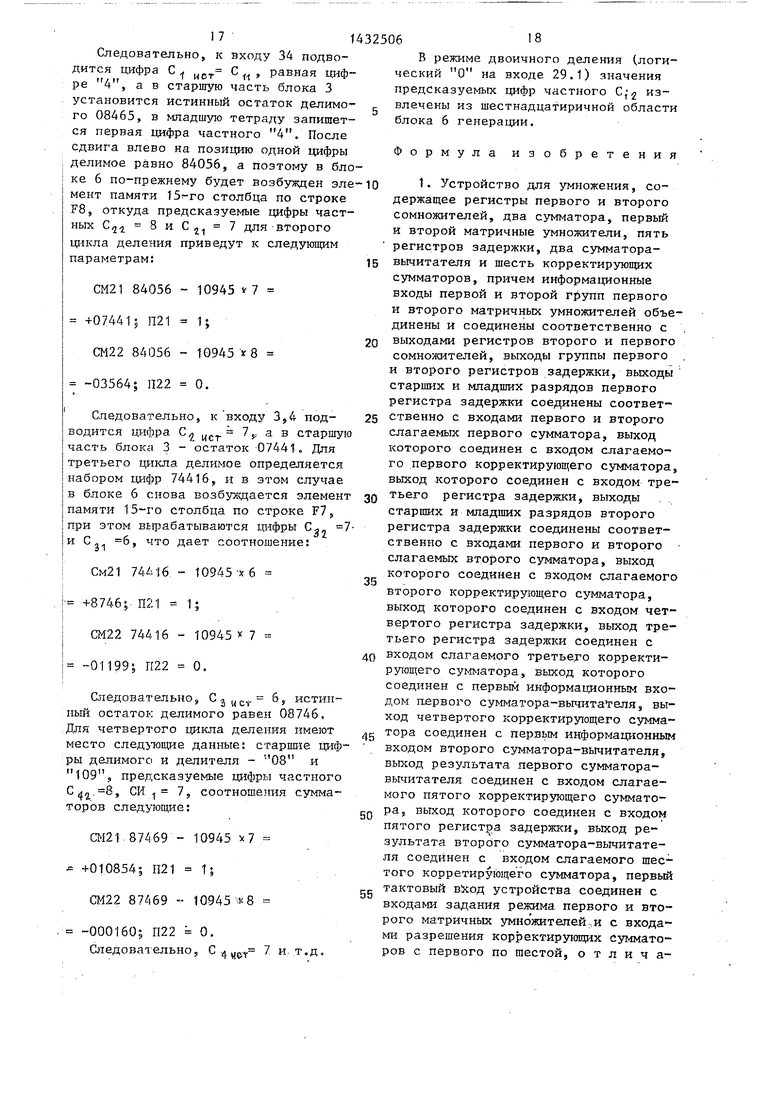

I Разбиением делителя на интервалы 5начений привело для десятичных делителей к 29 весам, а для двоичных - :с 46. Таблицы истинности для прошив- :си (прожига) элементов памяти блока j генерации составлены с избытком, f,e. по значениям старших цифр дели- його и делителя записана старшая предполагаемая цифра С - С В та.бл. 1 и 2 приведены фраг менты |габлиц истинности десятичного и шест адцатиричного генераторов для цифр частного С{,;.

Величины и количество весов делителя выбирались с таким расчетом, чтобы не было скачкообразного (больше чем на 1) изменения промежуто чных частных слеза направо и сверху вниз по горизонтальным и вертикальным строкам и столбцам таблиц истинности. Блок 6 генерации (фиг.2) состоит из двух групп элементов 31 и 32 памя fH, предназначенных соответственно для генерации избыточных 1щфр частных десятичных и шестнадцатиричных чисел.

При реализации генераторов по табл. 1 и 2 истинности с целью экономии оборудования исключены элементы памяти с весами 17-29 н 28-46 соответственно из десятичного и двоичного генераторов.

Значения цифр частного, охватывающие эти области по анализу старшей

2506

цифры делителя

0

5

0

п 5

5

0

5

14

2 или 2, зеркально переписаны в пустующие адреса генераторов путем искусственного инвертирования информации старшей цифры делимого. Массив предсказуемых десятичных цифр частного, охватываюпшй адреса (делимое) 06-30 с весами столбцов (делителя) 17-29 записан (прошит) в адресах от FO по СО десятичного генератора. При этом к активизирующим входам элементов памяти (4-16) десятичного генератора подсоединены выходы дешифратора 30, которые по разрешениям признаков 2 или 2 подводят соответственно веса делителя из столбцов 16 или 29, 15 или 28, 14 или 27, 13 или 26, ...,4 или 17.

Массив предсказуемых шестнадцатиричных цифр частного, охватывающий адреса делимого 01-30 с весами делителя в Ьтолбцах от 28 по 46 (табл.2), записан в адресах F1-CO двоичного генератора. К активизирующим входам элементов памяти (9-27) под управлением признака или 2 подсоединены выходы дешифратора 37, которые подводят веса делителя столбцов 9 или 28, 10 или 29, 11 или 30, ..., 27 или 26. Б конечном счете общее количество элементов памяти обоих генераторов получилось равным 16 + + 27 43., Из этих двух генераторов активизируется по одному элементу памяти и в итоге элементы ИЛИ 33 возбуждаются только по одному входу. Далее на выходах элементов И-ИЛИ 35 в зависимости от уровня входа 29.1 выводится информация от генераторов десятичных частньк (29.) либо шестнадцатиричных - (29.). Вьпсод 6.7 соответствует двум предсказуемым цифрам частного С,- и С j . Значение С- определяется по значениям переносов сумматоров 21 и 22, подведенных к входам 6.3 и 6.4 блока 6. Присвоение шинам С ; значений Сj либо

и

происходит в режиме деления

(29.27:1) по следующим функциям переносов:

а)П21 Л П22 - выполнить С.- -С,, в старшие разряды блока 3 занести

разность от корректирующего сумматора 23 как действительный остаток делимого;

б)П21 Л П22 - вьтолнить с,- - С.:; , в старшие разряды блока 3 занести разность от корректирующего суммато1 5

pa 24. Одновременно с занесением нс- тинного остатка делимого в младшую тетраду блока 3 заносится по входу 34 истинная цифра.

Остальные комбинации переносов, а также случаи, когда цифра частного десятичного деления получается больше девяти, возбуждает вход 6.2 и регистрирует ошибку деления. Текущая цифра частного В. определяется за один цикл работы множительного устройства путем умножения предсказуемых цифр В j и В j на полный набор делимого Ар, А , ..., А (множимого) а затем отыскани ем В по .результатам переноса сумматоров 21 и-22.

Предварительно на входе 29.2 устанавливается уровень логической 1, при котором в сумматорах-вычитателях 21 и 22 из компонент второго входа вычитаются компоненты первых входов. Мультиплексоры 18 и 19 настраиваются для прохождения данных от блоков 8 и 16 на входах 29.7г1, 29.8гО и 29.9гО, обеспечивающих подвод выходной информации делимого к вторым входам сумматоров-вычитателей 21 и 22.

Как показано на схеме блока 6 генерации, извлечение нулей из областей генераторов (С,) блокирует выработку сигналов на входах 3,6 и 3,5, одновременно с этим обеспечивает нуль на входы С- (3,4). При выработке сигнала сдвига влево на че- тьфе разряда по разрешению 29.5 делимое сдвинется влево на позицию одной цифры, при которой старшая часть не обновлена, а в позицию освободившихся битов запишутся нули. Этот цик деления является форсированным и время его выполнения намного меньше,чем время вычисления С. О (фиг.З).

Рассмотрим пример десятичного деления, взяв в качестве дел имого и делителя десятичные числа 521856692328 и 10945. Делимое по разрешению 29.3 через вход 28 располагаем в блоке 3, а затем по разрешению 29.8 через 8 заносим делитель в регистр 2.

В последующий момент вьфабатьша- ются уровни логических 1 на входах 29.1 и 29.2.

Вход 29.1 настраивает устройство на режим десятичного умножения, при котором, как уже было отмечено, активизируются: десятичная матрица в умножителе 4, все корректируюпрге

1432506

16

0

5

0

5

0

5

0

5

0

5

сумматоры и +10 и выходы десятичного генератора и блоке 6.

Вход 29.2 дает разрешение мульти-1 плексорам 18 и 19 для прохождения компонент десятичного умножения от блоков 16 и 25, сумматорам-вычитате- лям 21 и 22 - для осуществления вычитания от данных второго входа данных первого входа, коммутатору 7 - для занесения предсказуемых цифр блока 6 в регистр 1, коммутатору 8 - для отделения старшей части делимого, участвующей в данном конкретном цикле деления.

В исходный момент перед началом первого такта деления, независимо от режимов операций (десятичное или шестнадцатиричное), делимое располагается правее на позицию одной цифры, поэтому в первом такте старшей цифрой делимого будет нуль. Это обстоятельство обусловлено желанием исключить эффект переполнения, который может произойти при соответствующем соотношении старших цифр делимого и делителя.

Перед началом деления из соотношения количества цифр делимого и делителя определяется количество циклов, необходимых для вычисления целой части частного. Каждая цифра результата частного вычисляется за время, меньшее суммарного времени работы множительного устройства, так как при делении для отыскания истинной цифры частного необходимы лишь компоненты частичных произведений. В первом цикле текущее время делимого и делителя 05 и 109 и поэтому активизируются элементы памяти с весами 1.14-1.05 (столбец 28). По пересечению строки 6 столбца 28 из области десятичного генератора, определяемой адресом 15 (вес делителя 2), будет извлечена цифра 5, которая, уменьшаясь на единицу, а затем в виде двух цифр С . 5 и С j 4 запишется в Р1. Далее устройство, ньтолнив десятичное умножение на сумматорах-вьгчита- телях 21 и 22, сформирует следующие разности и переносы:

СМ21 52185 - 10945 х4

+08465; П21 1;

СМ22 52185 - 5 -09746; П22 0.

17

Следовательно, к входу

дится цифра С

ист 11 равная одфре

а в старшую часть блока 3

установится истинный остаток делимого 08465, в младшую тетраду запишется первая цифра частного 4. После сдвига влево на позицию одной цифры делимое равно 84056, а поэтому в блоке 6 по-прежнему будет возбужден элемент памяти 15-го столбца по строке РВ, откуда предсказуемые цифры частных С 8 и С j 7 для-второго щдкла деления приведут к следующим параметрам:

СМ21 84056 - 10945 v 7 +07441§ П21 1;

СМ22 84056 - 10945 8 -03564; П22 0.

Следовательно, к входу 3,4 подводится цифра С ист 7 f, а. 3 старшую часть блока 3 - остаток 07441 Для третьего цикла делимое определяется набором цифр 74416, и в этом случае в блоке 6 снова возбуждается элемент памяти 15-го столбца по строке F7, при этом вырабатываются цифры -1 и С,. 6, что дает соотношение:

См21 . - 10945 х 6 |- +8746; П21 1; I СМ22 74416 - 10945 - 1 ---- -01199 П22 0.

Следовательно, Cjyg 6, истинный остаток делимого равен 08746, Для четвертого цикла деления имеют место )Щие данные; старшие цифры делимого и делителя - 08 и 109., предсказуемые цифры частного С,8, СИ , 7, соотношения сумматоров следующие:

СМ21.87469 - 10945 7 - +010854; П21 1;

СМ22 87469 - 10945 8

-000160; П22 0.

Следовательно, С ц0т и-т,д.

В режиме двоичного деления (логический О на входе 29.1) значения предсказуемых цифр частного С- извлечены из шестнадцатиричной области блока 6 генера1 и.

Формула изобретения

выходами регистров второго и первого сомножителей, выходы группы первого . и второго регистров задержки, выходы старших и младших разрядов первого регистра задержки соединены соответственно с входами первого и второго слагаемых первого сумматора, выход которого соединен с входом слагаемого первого корректирующего сумматора, выход которого соединен с входом тре

тьего регистра задержки, выходы старших и младших разрядов второго регистра задержки соединены соответственно с входами первого и второго слагаемых второго сумматора, выход

которого соединен с входом слагаемого

второго корректирующего сумматора,

выход которого соединен с входом четвертого регистра задержки, выход третьего регистра задерлски соединен с

входом слагаемого третье,го корректирующего сумматора, выход которого соединен с первым информационным входом первого сумматора-вычита геля, выход четвертого корректирующего сз мматора соединен с первьм информационным входом второго сумматора-вычитателя, выход результата первого сумматора- вычитателя соединен с входом слагаемого пятого корректирующего сумматоpa, выход которого соединен с входом пятого регистра задержки, вькод результата второго сумматора-вычитателя соединен с входом слагаемого шестого корретирующего сумматора, первый

тактовый В5СОД устройства соединен с входами задания режима первого и второго матричных умно жителей.,и с входами разрешения корректирующих cyisoiaTo- ров с первого по шестой, о т л и ч а19

рения функциональных возможностей путем выполнения операций деления и преобразования, оно содержит два коммутатора, два мультиплексора, блок коммутации, блок генератдии и табличный преобразователь десятичного кода в шестнадцатиричный код, причем первый тактовый вход устройства соединен ю выход блока генерации соединены соот

С первым управляющим входом блока ге нepalaiи, второй управляюгций вход которого соединен с первым управляющим входом первого коммутатора, с управляющими входами первого и второго мультиплексоров, с управляющими входами первого и второго сз мматоров- вычитателей и с вторым тактовым входом устройства, тактовые входы с третьего по шестой устройства соединены соответственно с управляющими входами с первого по четвертый блока ком- мутации, первый и второй выходы которого соединены соответственно с первым и вторым информационнь1ми входами второго коммутатора, первый и второй управляющие входы которого являются соответственно седьмым и восьмым тактовыми входами устройства девятый тактовый вход которого соединен с третьим управляющим входом второго коммутатора и с вторым управляющим входом первого коммутатора, третий управляющий вход которого соединен с пятым управляющим входом блока коммутации и с десятым тактовым входом устройства, первый информационный вход которого соединен с первым информационным входом первого коммутатора, выход которого соединен с входом регистра первого сомножителя, выход пятого регистра задержки соединен с первым информационным входом второго мультиплексора, выход которого соединен с входом слагаемог четвертого корректирующего сумматора выход второго коммутатора является первым информационным выходом устройства, соединен с вторым информационным входом второго сумматора- вычитателя, с первым информационным входом первого мультиплексора, со входом регистра второго сомножителя и с входом табличного преобразователя десятичного кода в щестиадцатирич ный код, выход которого является вторым информационным выходом устройства, выход четвертого регистра задержки соединен с вторыми информационны

250620

ми входами второго мультиплексора и первого мультиплексора, выход которого соединен с вторым информа1лионным входом первого сумматора-вычитателя, второй информационный вход устройства , выход пятого корректирующего сумматора, выход шестого корректирующего сумматора и первый информационный

5

0

5

0

5

0

5

0

ветственно с информационными входами с первого по четвертый блока коммутации, шестой и седьмой зшравляющие - входы которого соединены соответственно с первым и вторым управляющими выходами блока генерации, второй информационный и третий управляющий выходы которого соединены соответственно с вторым информационным входом первого коммутатора и с сигнальным выходом устройства, выходы двух старших цифр второго коммутатора соединены соответственно с первым и вторым информационными входами блока генерации, третий, четвертый и пятьш информационные входы которого соединены соответственно с выходами переносов первого и второго сумматоров- вычитателей и с выходом трех старщих цифр регистра второго сомножителя,

элементов ИНВДИ первой группы, а также с первыми входами первой и второй групп пе;рвого элемента ., выход которого является третьим управ- лягапщм выходом блока генерации, второй и пятый информационные входы которого соединены с входами разрядов дешифратора цифр, третий и четвертый и|пформа1 ;ионные и второй управляющий в|ходы блока генерации соединены соот в|етственно с входами первого и второго разрядов и первым входом разре- wemin дешифратора управления, второй вкод разрешения которого соединен с и нверсными вькодами элементов H-IiOH п|ервой группы, прямой выход первого эремента И-И.ПИ которой соединен с первыми входами первой, второй и третьей групп второго элемента И-ИЛИ, вторые входы которых соединены соответственно с прямыми выходами элементов И-ИЛИ с второго по четвертый п|ервой группы, прямой выход третье- гр элемента И-ИШ которой соединен с| первьпм входом первой группы треть- еро элемента И-РиП второй вход пер- в1ой группы которого объединен с первым входом второй группы третьего з|лемента И-ИЛИ к соединен с прямым в|ыходом второго элемента И-ИЛИ пер- Цой группы, прямой выход четвертого элемента И-ИЛИ которой соединен с вторым входом второй группы третьего элемента и с первым входом элемента ИСКЛЮ ШОЩЕЕ ИЛИ, второй Еход которого соединен с И шерсиым 1ЫХОДОМ третьего элемента Й-ИЛИ первой группы и с первым входом третьей группы третьего элемента И-ИЛИ, Е|торой и третий входы третьей х руппы Которой соединены соответственно с Инверсными Выходами второго и чет- i epToro элементов И-ИЛЙ первой группы, прямые выходы элементов И-ИЖ которой соединены с первьми входами itepBbix групп соответствующих элементов И-ИЛИ второй группы, выходы которых являются первым информационным выходом блокд, генерации, первые входы вторых: групп элементов второй группы соединены соответственно с выходами второго и третьего элементов И-ИЛИ,- с. выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ к с инверсным вых.одом чет уертого элемента И-ИЛИ первой группы «ервый выход дешифратора управления является первым упраззляющим выходом блока генерации, и соединен с вторымр

5

0

5

0

5

0

5

0

5

входами вторых групп.элементов И-ИЛИ второй.группы, второй выход дешифратора управления является вторым управляющим выходом блока генерации и соединен с вторыми входами первых групп элементов И-ШШ второй группы, третий и четвертьй выходы дешифратог ра управления соединены соответственно с входами третьей и четвертой групп первого элемента И-ШШ, вторые входы первой и второй групп которого соединены с выходом первого элемента ИЛИ первой группы, выходы второго и третьего элементов ИЛИ которой соединены соответственно с третьими входами первой и второй групп первого элемента И-ИЛИ, прямые выходы элементов И-ИЛИ первой rpynnHj выходы второго и третьего элементов И-ИЛИ, выход элемента ИСКЛЮЧАЮИЩЕ ИЛИ и инверсный выход четвертого элемента И-ИЛИ первой группы обраэзпот второй информационный выход блока генерации.

коммутации, третий управляющий вхоД которого соединен с первыми входами четвёртых групп элементов И-ИЛИ группы второй вход четвертой группы i-ro (,...,К-4, К - разрядность информации) элемента И-ИЛИ группы соединен с выходом (i+4)-ro триггера группы, вторые входы четвертых групп элементов И-1иМ с (К-3),-го до К-го груп-ю информационного входа блока коммутапы соединены соответственно с входами

разрядов четвертого информационного входа блока коммутации, четвертый управляющий вход которого соединен с первыми входами пятых групп элементов И-ИЛИ с семнадцатого по К-й группы, вторые входы пятых групп которых соединены соответственно с входами разрядов с первого по (К-1б)-й второго

ции,

- .eiri-or eooM

Nf tf tef eobtftot

«-«4 чф r- 009 Ot

r t .oaoxO4ffi

1 C4r4f 4 rf A er f C09t(V«

г чп- - гШ О«г сояв о« -f4fif4i -9 n.mtn ar eO9 at9t

1Л л r

- «4 - cj n

О - -М Ч -

o - ---« 4rt

-Ф1Л«О О 40 «0

% - iniriin t tvaooo K Й It e « к Fo ее

о о - - « ч « « « . - -« «в ГЪ OB «6 ООО - - Ч Л«Ш- - - Ш 1Л« Л в вГ.1

- -««OMMrt MtnintfliftiOveOr ЭОО - - -М«МММ«П Л- - «- О Л в в

эооо«-«- «чмм« «

о о о

о о о о в о

о - - Ь о о о

C4r4l4P I 1 nr Tvt

- 4t «j4rt i« n-

- -М СЧСЧ V « С4 «ч Ы « «

о о о о о

о О о о

о о е о

о о о о

о о о о о о о - - С4(Ч «ч СЧМЛ

о оо оо о о «- - - , - - еч сч еч ч гчсч

оо-оооооо

о ооооооо

оооо-ооооо

5

сч ш

о о

Sin о

о

S г

-cjm-tf nioi eowo ооооооово- -

at OK

в1 Ot Ot

ич ш ш

-«

т -я

сч гч сч сч м еч . «п 1 п

N « я «ч г П «П

ем, {Ч сч t4rt п

- Г4 г. -N «ч

гч г Г4

(

-c4rt- nvoi eo

«

fe

Ч

4,rj

J

l

ЛТП

ч

««

4S

N|

VJ

,4J

5{ g

I

ll

e.

в. н- /3

в.к-11

В. к-10

в. к-9

С в.н-6

в.к-Ч

a.

1/

ТциН/1

Фин.

г

Жцинл Фиг. 6

Жцинй

Z9.1

29М 29.5 W.6 19.1

т

f o/ti/ve/ft/e omopoCf

tfi/фрЫ

Фиг.10

Г

xFTl

ГУ.

Фи.11

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-10-23—Публикация

1986-11-14—Подача