1

Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах программного управления, в вычислительных машинах и цифровых измерительных приборах.

Известно отсчетное устройство, содержащее генератор опроса, логические элементы, усилители, дешифратор.

Недостатком его является то, что оно может быть использовано только для стробоскопического питания цифровых индикаторов.

Наиболее близким техническим решением к изобретению является отсчетное устройство, содержаш,ее многоразрядный реверсивный двоично-десятичный счетчик, тактовый генератор, выход которого соединен с входом тактового распределителя, выход которого соединен с входами первого, коммутатора, выходы которого соединены соответственно с первой группой входов блока цифровых индикаторов, вторая группа входов которого соединена с выходами второго коммутатора, входы которого соединены с выходами дешифратора.

Такое устройство имеет ограниченные функциональные возможности, так как используемая в нем аппаратура предназначена только для стробоскопической индикации.

Целью изобретения является расширение

2

функциональных возможностей устройства.

Цель достигается тем, что в устройство введены переключатель ввода, шифратор, блок реверсивных двоичных счетчиков, десятичный сумматор, триггер запоминания переноса, триггер .переключения , триггер запоминания ввода, элемент И, блок элементов И и блок кольцевых регистров, шины сдвига которых соединены с выходом тактового генератора и со счетным входом триггера запоминания переноса, вход управления и выход которого соединены соответственно с выходом и входом переноса десятичного сумматора. Выходы блока кольцевых регистров

соединены с первыми входами блока элементов И, выходы которых, а также выходы шифратора соединены с соответствующими входами слагаемых сумматора, выходы которого соединены с входами управления блока кольцевых регистров, а также с входами деШИфратора, выходы тактового распределителя соединены с входами блока переключателей ввода k-и (где k, ..., п) выход тактового распределителя соединен с первым входом

элемента И, а (/г+О-й выход с входами установки в «О триггера переключения режимов и триггера запоминания команды «Ввод. С вторым входом элемента И соединен ед 1ничный выход триггера запоминания команды «Ввод, выходы реверсивных двоичных

счетчиков и выход блока переключателей ввода соединены с разрядным входом шифратора, вход .управления которого, а также вторые входы блока элементов И соединены с выходом триггера переключения режимов, вход установки в «1 которого соединен с выходом элемента И.

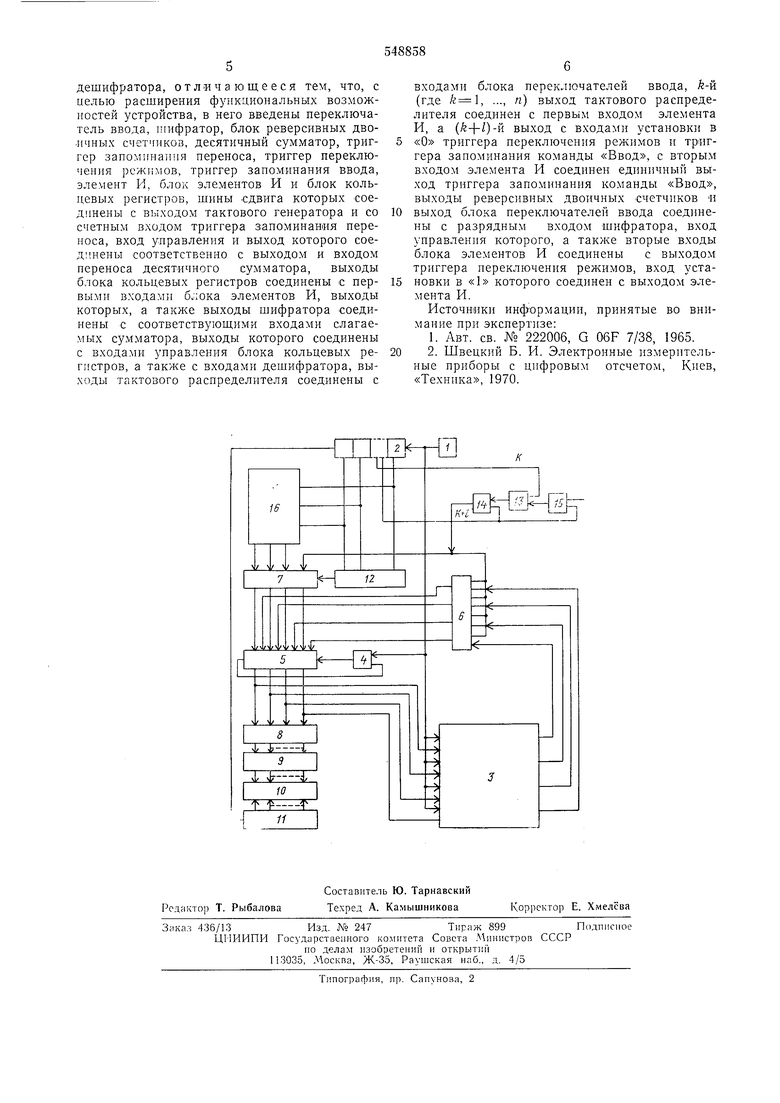

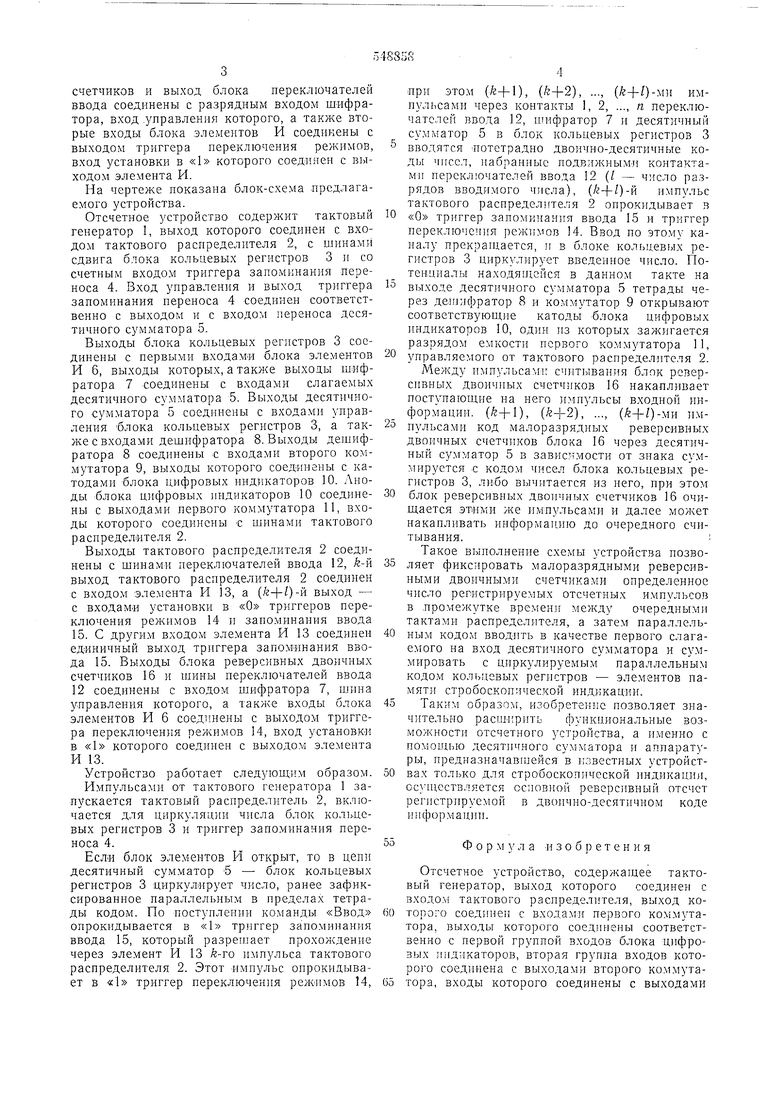

На чертеже показана блок-схема предлагаемого устройства.

Отсчетное устройство содержнт тактовый генератор 1, выход которого соединен с входом тактового распределителя 2, с шинами сдвига блока кольцевых регистров 3 и со счетным входом триггера запоминания переноса 4. Вход управления и выход триггера запоминания переноса 4 соединен соответственно с выходом и с входом переноса десятичного сумматора 5.

Выходы блока кольцевых регистров 3 соединены с первыми входами блока элементов И 6, выходы которых, а также выходы шифратора 7 соединены с входами слагаемых десятичного сумматора 5. Выходы десятичного сумматора 5 соединены с входами управления блока кольцевых регистров 3, а также с входами дешифратора 8. Выходы дешифратора 8 соединены с входами второго коммутатора 9, выходы которого соединены с катодами блока цифровых индикаторов 10. Лноды блока цифровых иидикаторов 10 соединены с выходами первого коммутатора 11, входы которого соединены -с шинами тактового распределителя 2.

Выходы тактового распределителя 2 соединены с шинамн переключателей ввода 12, k-vi выход тактового распределителя 2 соединен с входом элемента И 13, а (/г+О-й выход - с входами установки в «О триггеров переключения режимов 14 и запоминания ввода 15. С другим входом элемента И 13 соединен единичный выход триггера запоминания ввода 15. Выходы блока реверсивных двоичных счетчиков 16 и шины иереключателей ввода 12 соединены с входом шифратора 7, шина управления которого, а также входы блока элементов И 6 соединены с выходом триггера переключения режимов 14, вход установки в «1 которого соединен с выходом элемента И 13.

Устройство работает следуюшим образом.

Имнульсамн от тактового генератора 1 запускается тактовый распределитель 2, включается для циркуляции числа блок кольцевых регистров 3 и триггер запоминання переноса 4.

Если блок элементов И открыт, то в цепи десятичный сумматор 6 - блок кольцевых регистров 3 циркулирует число, ранее зафиксированное параллельным в пределах тетрады кодом. По иоступлеинн команды «Ввод опрокидывается в «1 триггер запоминания ввода 15, который разрешает прохождение через элемент И 13 k-ro импульса тактового распределителя 2. Этот имиульс опрокидывает в «1 триггер переключения режимов 14,

при этом (fe+1), (/г+2), ..., (/г+/)-ми имиульса МИ через контакты , 2, ..., п переключателей ввода 12, шифратор 7 и десятичный сумматор 5 в блок кольцевых регистров 3 вводятся иотетрадио двоично-десятичные коды чисел, набранные подвил ными контактами переключателей ввода 12 (/ - число разрядов вводимого числа), (/г-|-/)-й импульс тактового распределителя 2 опрокидывает в

«О триггер запоминания ввода 15 и триггер переключепш режимов 14. Ввод по этому каиалу прекращается, и в блоке кольцевых регистров 3 циркулирует введенное число. Потеициалы находящейся в данном такте на

выходе десятичного сумматора 5 тетрады через дешифратор 8 и коммутатор 9 открывают соответствующие катоды блока цифровых индикаторов 10, один нз которых зажигается разрядом емкости первого коммутатора 11,

управляемого от тактового распределителя 2. Между импульсами считывания блок реверсивных двоичных счетчиков 16 накапливает поступающие на него импульсы входной информации. (+1), (й-1-2), ..., )-y. имиульсами код малоразрядных реверсивных двоичных счетчнков блока 16 через десятичный сумматор 5 в зависимости от знака су.ммируется с кодом чисел блока кольцевых регистров 3, либо вычитается из него, при этом

блок реверсивных двончных счетчиков 16 очищается этими же импульсами и далее может накапливать информацию до очередного считывания.: Такое выполнение схе.мы устройства позволяет фиксировать малоразряднымн реверсивными двоичными счетчиками оиределенное число регистрируемых отсчетных импульсов в промежутке времени между очередными тактами распределителя, а затем параллельным кодом вводить в качестве первого слагаемого на вход десятичного сумматора и суммировать с циркулируемым параллельным кодом кольцевых регистров - элементов иамяти стробоскопической индикации.

Таким образом, изобретеиие позволяет значительно pacHJHpHTb функциональные возможностн отсчетного устройства, а именно с помощью десятичного сумматора и аппаратуры, предназначавшейся в известных устройствах только для стробоскопической индикация, осуществляется о сновной реверсивный отсчет регистрируемой в двоично-десятичном коде информации.

Ф о р м } л а изобретения

Отсчетное устройство, содержащее тактовый генератор, выход которого соединен с входом тактового распределителя, выход которого соединен с входами первого коммутатора, выходы которого соединены соответственно с первой группой входов блока цифровых иидикаторов, вторая группа входов которого соединена с выходами второго коммутатора, входы которого соединены с выходами

| название | год | авторы | номер документа |

|---|---|---|---|

| Отсчетное устройство | 1975 |

|

SU614435A1 |

| Отсчетное устройство | 1976 |

|

SU661548A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Отсчетное устройство | 1976 |

|

SU734676A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

Авторы

Даты

1977-02-28—Публикация

1974-05-31—Подача