Предлагаемое устройство относится к области контрольно-измерительной техники п может быть использовано для контроля и статистического анализа параметров двоичных каналов и каналов передачи данных.

Принцип построения приборов тестового контроля, к которым относится предлагаемое устройство анализа, заключается в следующем. Устройство псевдослучайных тестовых последовательностей помещают на приемном конце исследуемого канала. На передающем конце работает датчик испытательного теста. Датчик и устройство анализа теста содержат сфазированные по циклу рекурре1ггиого кода кольцевые регистры с логической обратной связью, с помощью которых вырабатывается и анализнруется тест.

Известны устройства для анализа псевдослучайных тестовых последовательностей, содержащие кольцевой регистр рекуррентного кода, полусумматоры, делители частоты, триггеры, логические схемы «И, «ИЛИ. Однако эти устройства не обеспечивают эффективного анализа псевдослучайных тестовых последовательностей.

В предлагаемом устройстве с целью повыщения эффективности работы при одновременном упрощении конструкции, используются сигналы, характеризующие состояние канала связи в течение длительности каждого информационного импульса. Подобные сигиалы формируются устройствами оценки качества сигнала (устройствами формироваиия сигналов стирания). В предлагаемом устройстве сигналы качества используются для разрешения или запрещения подачи на вход соответствующего счетчика импульсов сбоев.

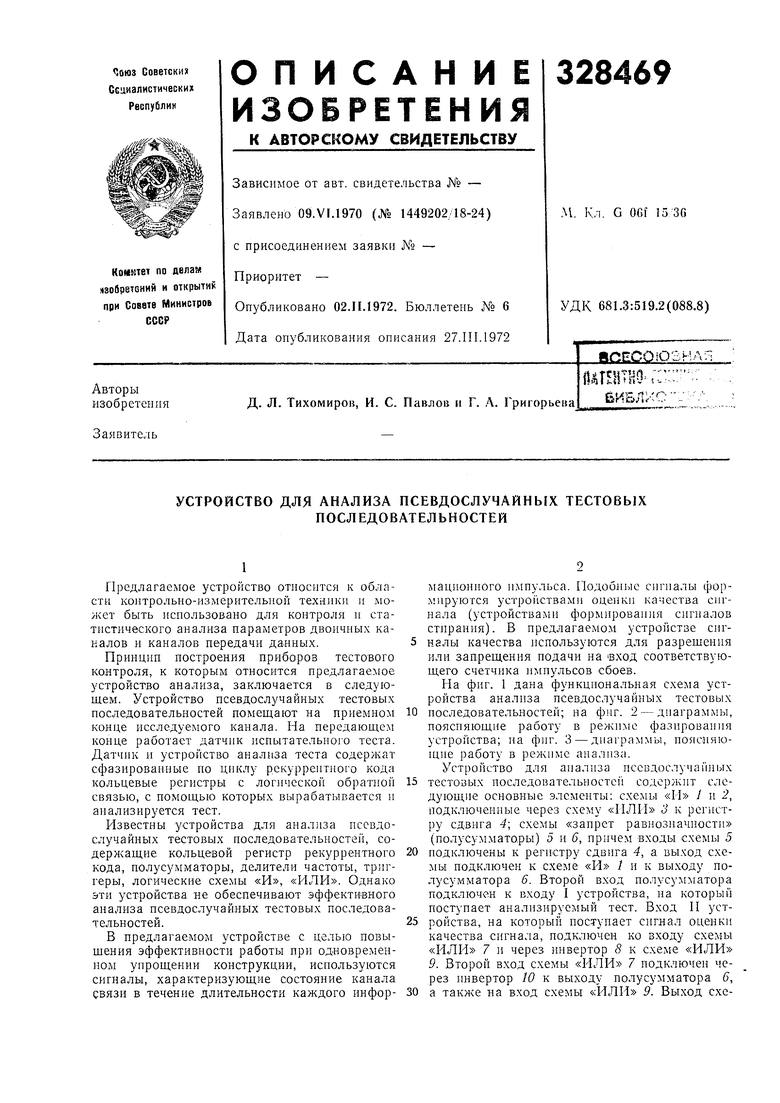

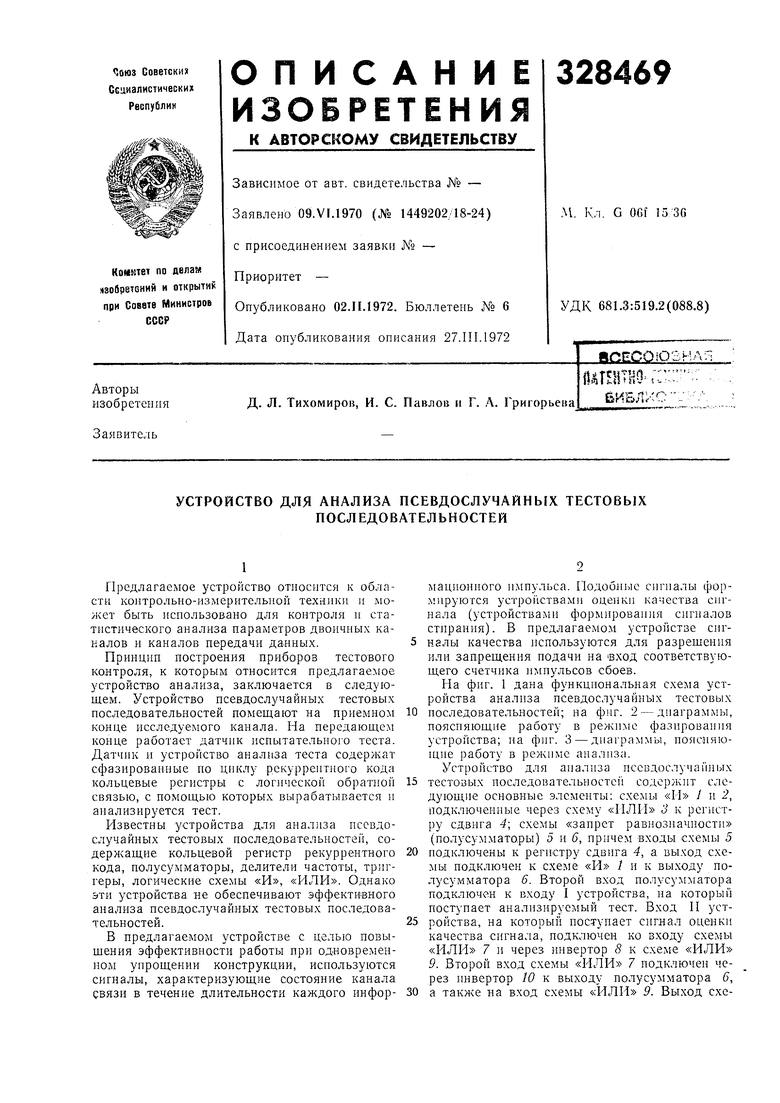

На фиг. 1 дана функциональная схема устройства анализа псевдослучайных тестовых

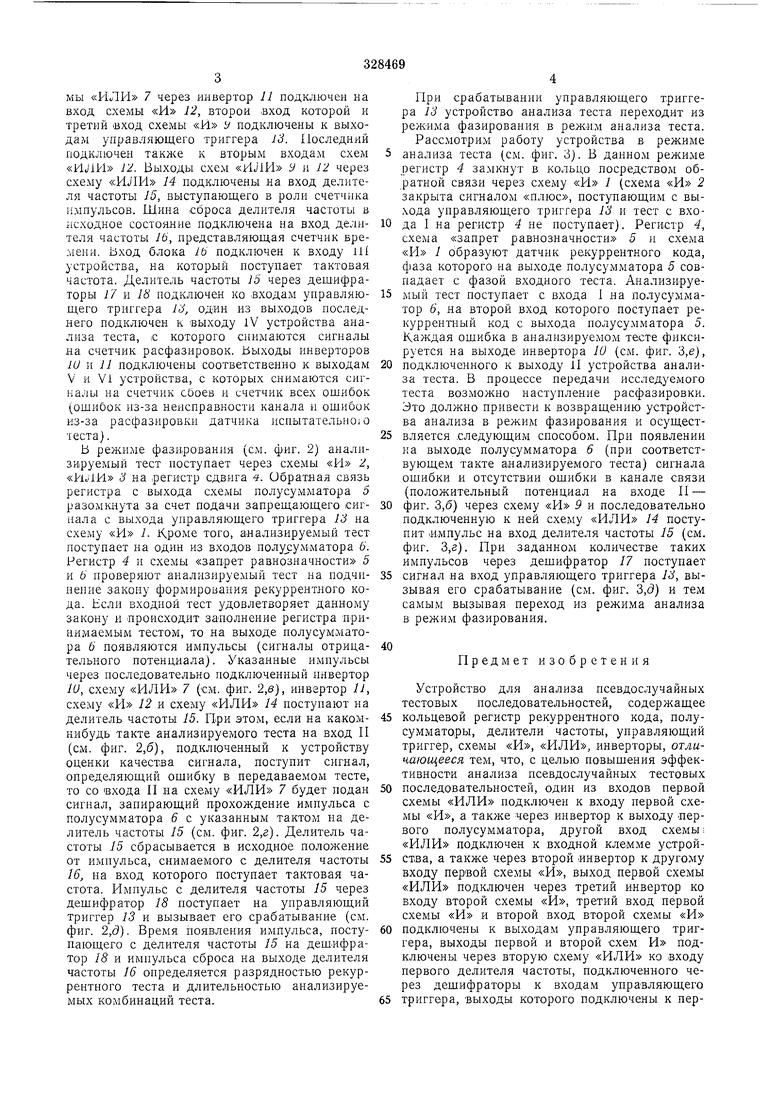

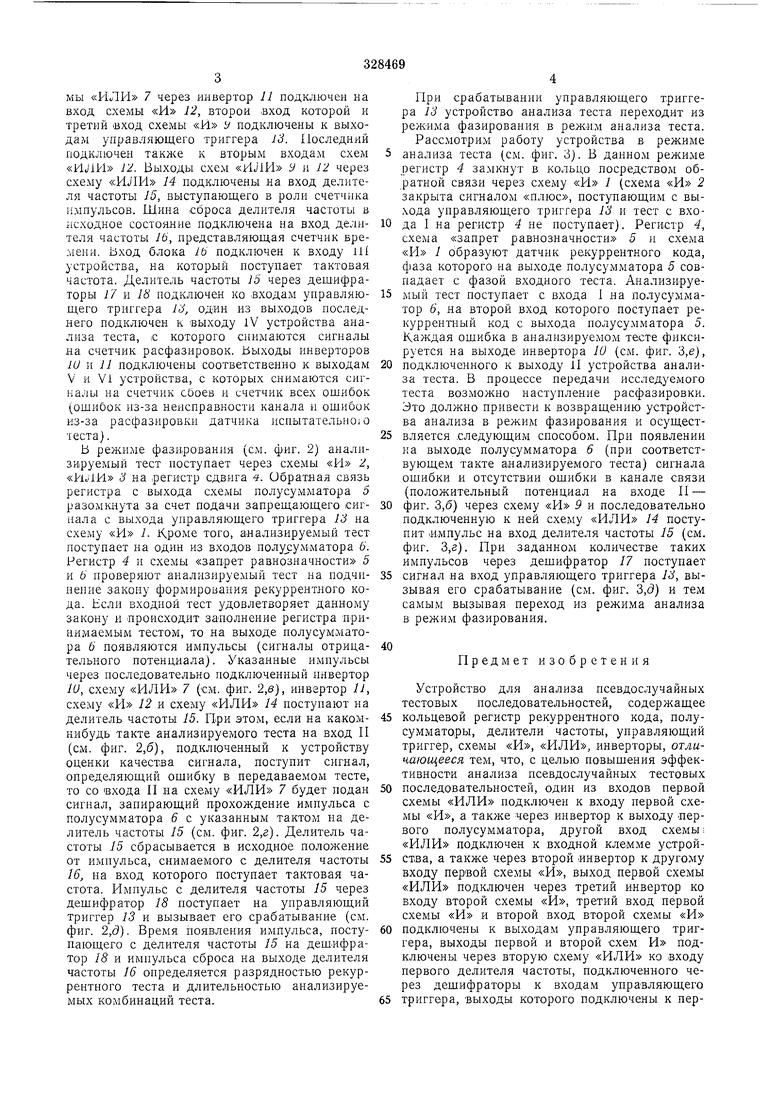

последовательностей; на фиг. 2 - диаграммы,

поясняющие работу в режиме фазирования

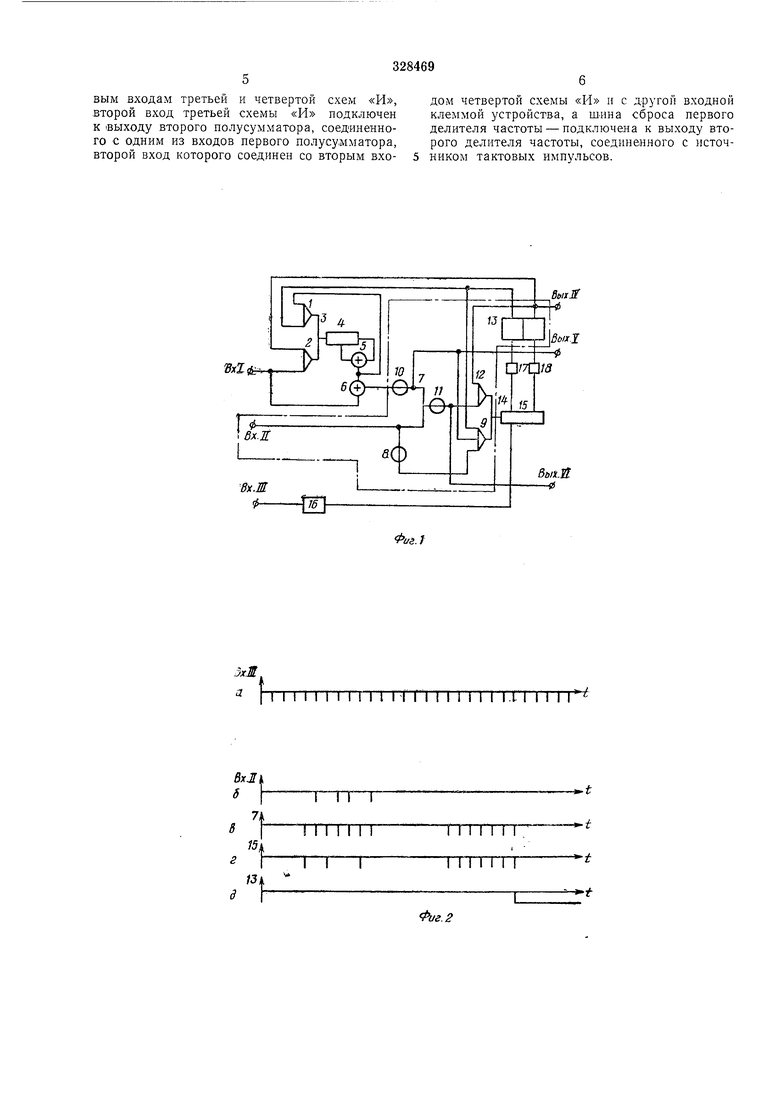

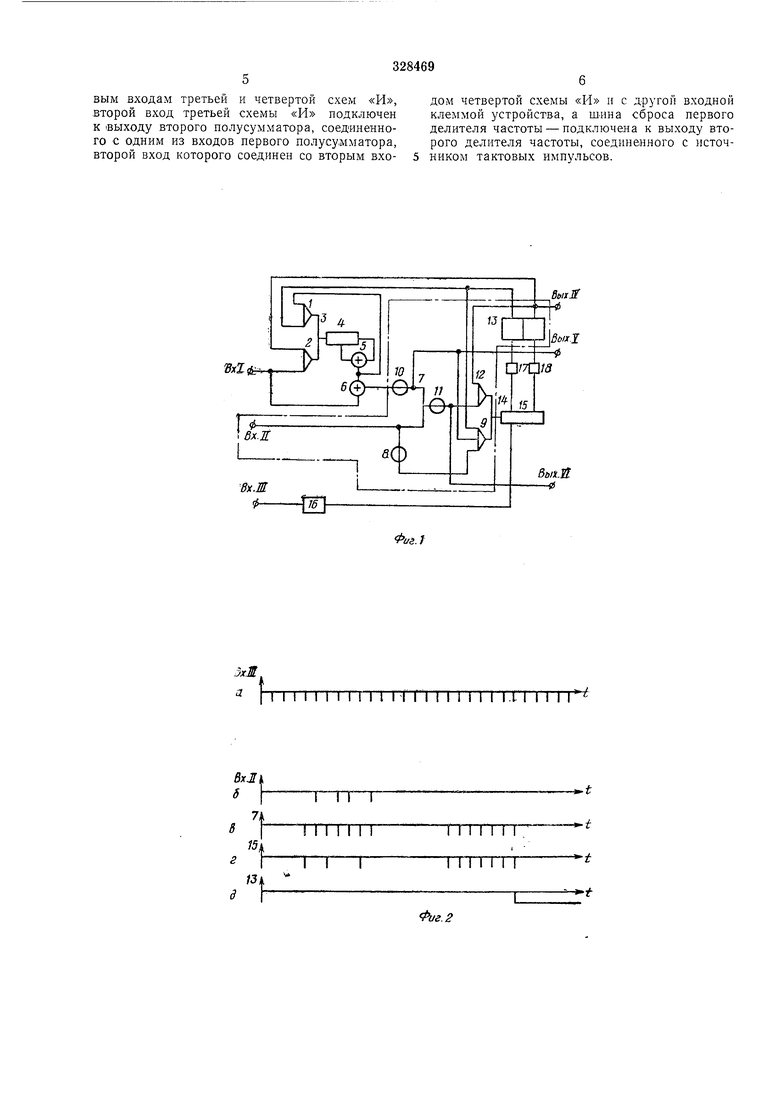

устройства; на фиг. 3 - диаграммы, иоясняющие работу в режиме анализа.

Устройство для анализа псевдослучайных

тестовых последовательностей содержит следующие основные элементы: схемы «II У и 2, подключенные через схему «НЛП 3 к регистру сдвига 4; с.хемы «заирет равнозначности (полусумматоры) 5 и 6, причем входы схемы 5

подключены к регистру сдвига 4, а выход с.хемы подключен к схеме «И / и к вы.ходу полусумматора 6. Второй вход полусумматора подключен к входу I устройства, на который поступает анализируемый тест. Вход II устройства, на который ноступает сигнал оценки качества сигнала, подключен ко входу схемы «ИЛИ 7 и через инвертор 8 к схеме «ИЛИ 9. Второй в.чод схемы «ИЛИ 7 подключен через инвертор W к выходу полусумматора 6,

мы «ИЛИ 7 через инвертор 11 подключен на вход схемы «И 12, второй вход которой и третий йход схемы «И У подключены к выходам управляющего триггера 13. Последний подключен такл.е к вторым входам схедМ «ИЛИ 12. Выходы схем «ИЛИ У и 12 через схему «ИЛИ 14 подключены на вход делителя частоты 15, выступающего в роли счетчика импульсов. Шина сброса делителя частоты в исходное состояние подключена на вход делителя частоты 16, представляющая счетчик времепи. Вход блока 1Ь подключен к входу ill устройства, на который поступает тактовая частота. Делитель частоты 15 через дешифраторы 17 и 18 подключен ко .входам управляющего триггера 13, один из выходов последнего подключен к выходу IV устройства анализа теста, ic которого снимаются сигналы на счетчик расфазировок. Выходы инверторов Ш и 11 подключены соответственно к выходам V и Vi устройства, с которых снимаются сигналы на счетчик сбоев и счетчик всех ошибок (ошибок из-за неисправности канала и ошибок из-за расфазировки датчика испытательною теста).

В рен,име фазирования (см. фиг. 2) анализи|руемый тест ноступает через схемы «И 2, «ИЛИ 3 на регистр сдвига 4. Обратная связь регистра с выхода схемы полусумматора 5 разом1шута за счет подачи запрещающего сигнала с выхода управляющего триггера 13 на схему «И 1. Кроме того, анализируемый тест поступает на один из входов полусумматора 6. Регистр 4 и схемы «запрет равнозначности 5 и Ь проверяют анализируемый тест на подчинение закону формирования рекуррентного кода. Бели входпой тест удовлетворяет данному закону и происходит заполнение регистра нринимаемым тестом, то на выходе полусумлитора 6 появляются импульсы (сигналы отрицательного потенциала). Указанные имнульсы через последовательно подключенный инвертор 10, схему «ИЛИ 7 (см. фиг. 2,е), инвертор И, схему «И 12 и схему «ИЛИ 14 постунают на делитель частоты 15. При этом, если на какомнибудь такте анализируемого теста на вход II (см. фиг. 2,6), подключенный к устройству оценки качества сигнала, поступит сигнал, определяющий ошибку в передаваемом тесте, то со входа П на схему «ИЛИ 7 будет подан сигнал, запирающий прохождение импульса с полусумматора 6 с указанным тактом на делитель частоты 15 (см. фиг. 2,г). Делитель частоты 15 сбрасывается в исходное положение от импульса, снимаемого с делителя частоты 16, на вход которого поступает тактовая частота. Импульс с делителя частоты 15 через дешифратор 18 поступает на унравляющнй триггер 13 и вызывает его срабатывание (см. фиг. 1,д). Время ноявления импульса, поступающего с делителя частоты 15 на дешифратор 18 и импульса сброса на выходе делителя частоты 16 онределяется разрядностью рекуррентного теста и длительностью анализируемых комбинаций теста.

При срабатывании управляющего триггера 13 устройство анализа теста переходит из режима фазирования в режим анализа теста.

Рассмотрим работу устройства в режиме анализа теста (см. фиг. 3). Б данном режиме регистр 4 за.мкнут в кольцо посредством обратной связи через схему «И 1 (схема «И 2 закрыта сигналом «плюс, поступающим с выхода управляющего триггера 13 и тест с входа I на регистр 4 не ноступает). Perncip 4, схема «запрет равнозначности 5 и схема «И I образуют датчик рекуррентного кода, фаза которого на выходе полусумматора 5 совпадает с фазой входного теста. Анализируемый тест поступает с входа I на полусумматор 6, на второй вход которого поступает рекуррентный код с выхода нолусумматора 5. Каждая ошибка в анализируемом тесте фиксируется на выходе инвертора 10 (см. фиг. 3,е), подключенного к выходу П устройства анализа теста. В процессе передачи исследз емого теста возможно настунление расфазировки. Это должно привести к возвращению устройства анализа в режим фазирования и осуществляется следующим способом. При появлении на выходе полусумматора 6 (при соответствующем такте анализируемого теста) сигнала ошибки и отсутствии ошибки в канале связи {положительный потенциал на входе П - фиг. 3,6) через схему «И 9 и последовательно подключенную к ней схему «ИЛИ 14 поступит (Импульс на вход делителя частоты 15 (см. фиг. 3,г). При заданном количестве таких импульсов через дешифратор 17 поступает сигнал на вход управляющего триггера 13, вызывая его срабатывание (см. фиг. 3,(3) и тем самым вызывая переход из режима анализа в режим фазирования.

Предмет изобретения

Устройство для анализа псевдослучайных тестовых носледовательностей, содержащее кольцевой регистр рекуррентного кода, полусумматоры, делители частоты, управляющий триггер, схемы «И, «ИЛИ, инверторы, отличающееся тем, что, с целью повышения эффективности анализа псевдослучайных тестовых последовательностей, один из входов первой схемы «ИЛИ подключен к входу нервой схемы «И, а также через инвертор к выходу первого полусумматора, другой вход схемы; «ИЛИ подключен к входной клемме устройства, а также через второй инвертор к другому входу первой схемы «И, выход первой схемы «ИЛИ подключен через третий инвертор ко входу второй схемы «И, третий вход первой схемы «И и второй вход второй схемы «И подключены к выходам управляющего триггера, выходы первой и второй схем И подключены через вторую схему «ИЛИ ко входу первого делителя частоты, подключенного через дешифраторы к входам управляющего триггера, выходы которого подключены к первым входам третьей и четвертой схем «И, второй вход третьей схемы «И подключен к выходу второго полусумматора, соединенного с одним из входов первого полусумматора, второи вход которого соединен со вторым вхо- 5

дом четвертой схемы «И и с другой входной клеммой устройства, а ш.ина сброса первого делителя частоты - подключена к выходу второго делителя частоты, соединенного с источником тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор последовательности ошибок | 1982 |

|

SU1077044A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Генератор псевдослучайных последовательностей | 1979 |

|

SU877533A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ ИНФОРМАЦИОННЫХ СВОЙСТВ ТЕСТА | 1991 |

|

RU2068580C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ КОМБИНИРОВАННОГО ПРИМЕНЕНИЯ ДВОЙСТВЕННОГО БАЗИСА ПОЛЯ GF(2) И ВЫДЕЛЕНИЯ "СКОЛЬЗЯЩЕГО ОКНА" С ОШИБКАМИ | 2014 |

|

RU2580806C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

arisfe

JXjl

I I I I I 1 т I 1 I trl I и I 1 I M 111 I I I I

1Ц д I

ВхЖ

° I I I I I 1 1 I 1 I И 1 I I 1 1 1 1 I I I I ГI 1 1 I г:

Даты

1972-01-01—Публикация