Р1зобретекие относится к области вычислительной техники и предназначено для преобразования двоичных кодов.

Известно устройство для потенцирования логарифмов по основанию два в двоичной системе счисления, содержащее регистр сдвига, регистр характеристик, реверсивный счетчик, схемы сравнения и логическое обрамление.

Цель изобретения - расширение функциональных возможностей устройства и обеспечение выполнения операций как потенцирования, так и логарифмирования.

Цель достигается тем, что в предлагаемом устройстве первые входы второй и третьей схем «И соединены с выходом генератора тактовых импульсов, выход первого триггера соединен со вторым входом второй схемы «И, выход второго триггера соединен со вторым входом третьей схемы «И, выход второй схемы «И соединен с первым входом схемы «ИЛИ, выход третьей схемы «И соединен со вторым входом схемы «ИЛИ и со входом обратного счета реверсивного счетчика, а выход сдвигающего регистра соединен со входом второго триггера.

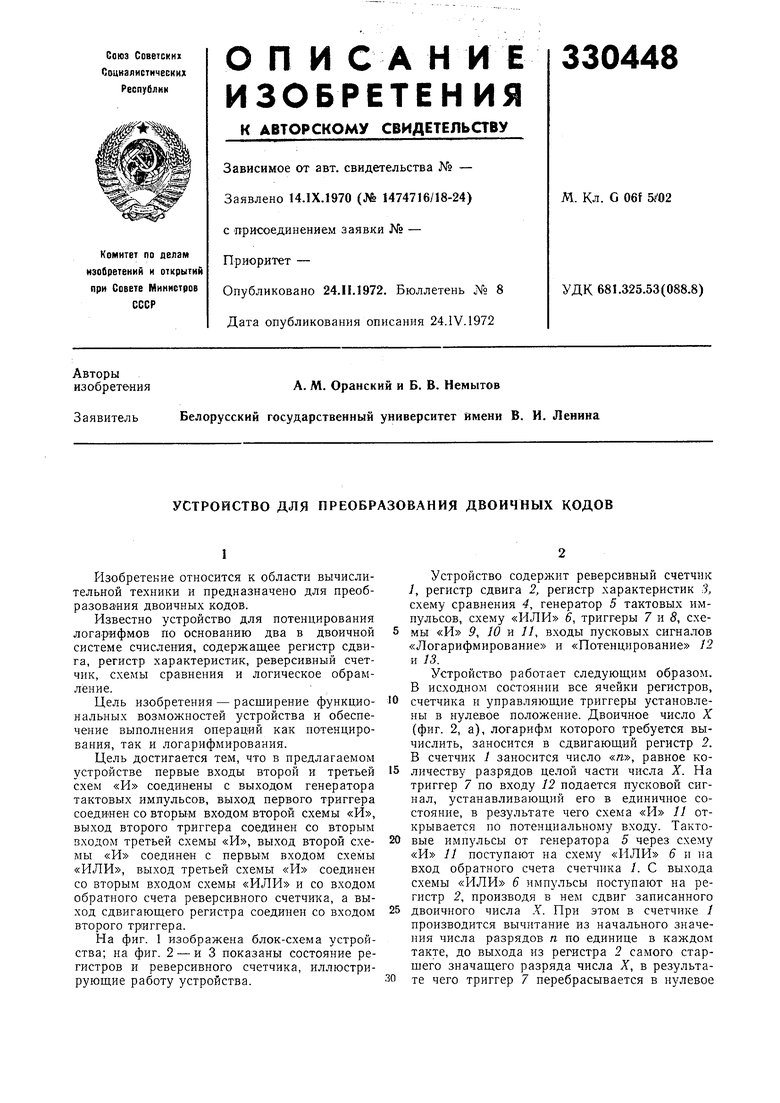

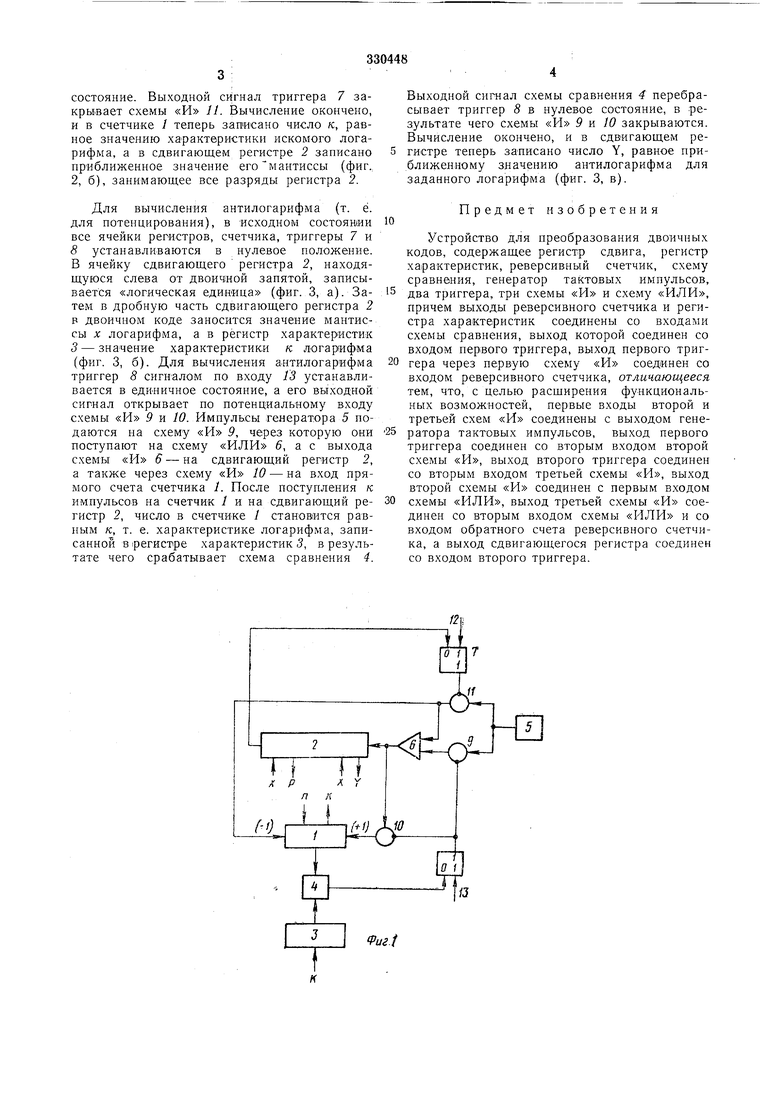

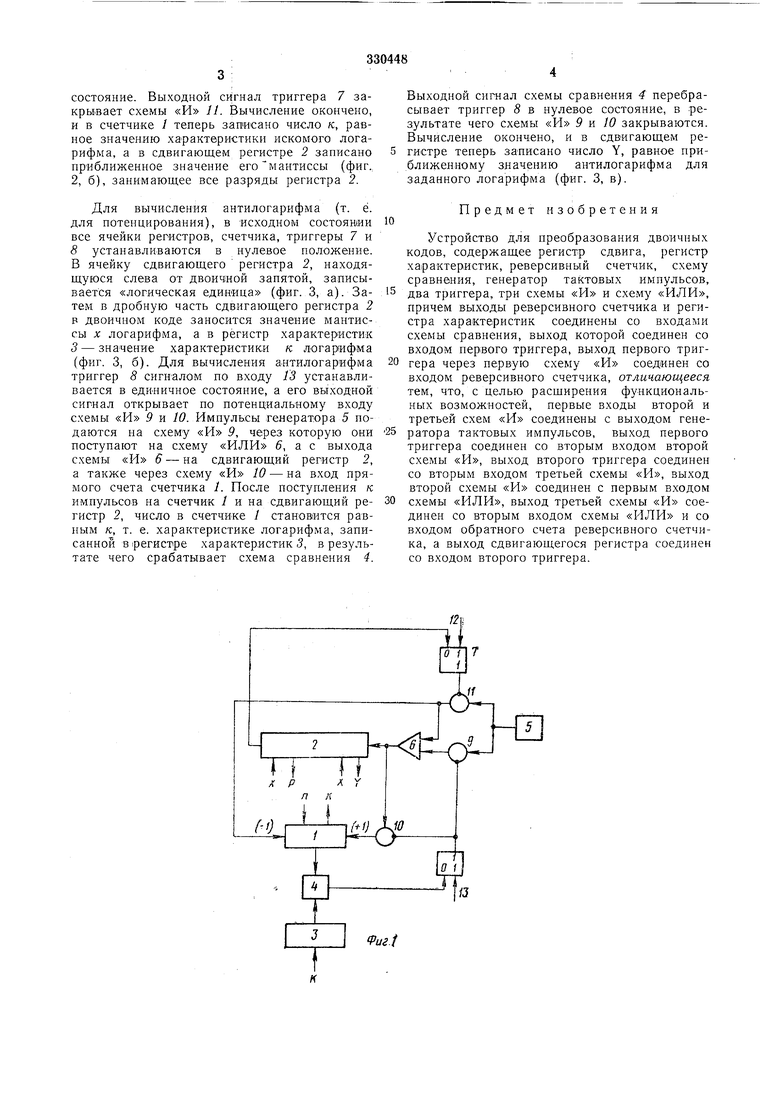

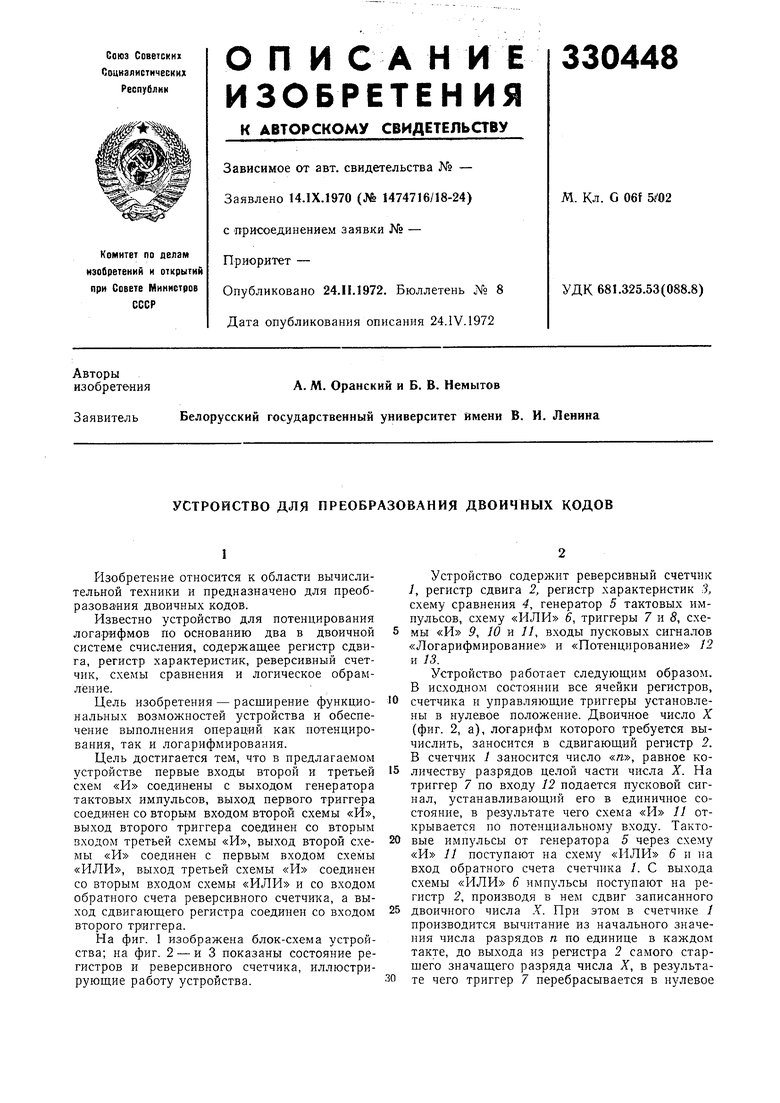

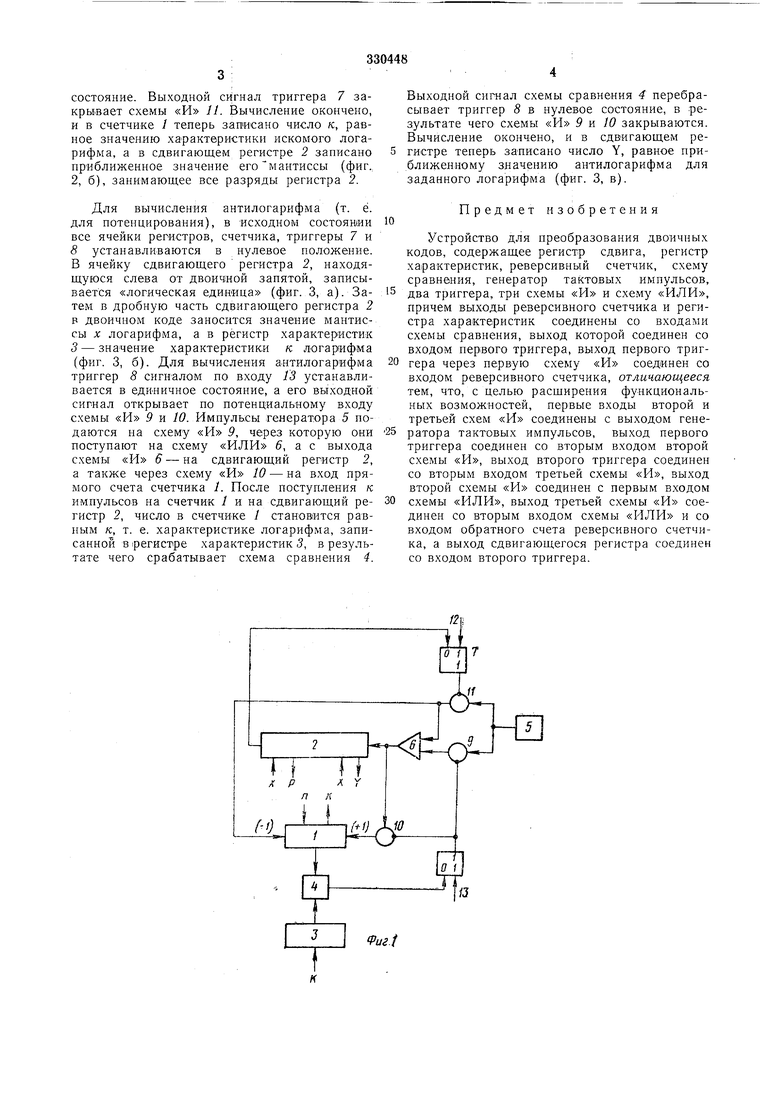

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - и 3 показаны состояние регистров и реверсивного счетчика, иллюстрирующие работу устройства.

Устройство содержит реверсивный счетчик 1, регистр сдвига 2, регистр характеристик 3, схему сравнения 4, генератор 5 тактовых импульсов, схему «ИЛИ 6, триггеры 7 и 8, схемы «И 9, 10 и 11, входы пусковых сигналов «Логарифмирование и «Потенцирование 12 и 13.

Устройство работает следующим образом. В исходном состоянии все ячейки регистров,

счетчика и управляющие триггеры установлены в нулевое положение. Двоичное число X (фиг. 2, а), логарифм которого требуется вычислить, заносится в сдвигающий регистр 2. В счетчик 1 заносится число «п, равное количеству разрядов целой части числа X. На триггер 7 по входу 12 подается пусковой сигнал, устанавливающий его в единичное состояние, в результате чего схема «И // открывается по потенциальному входу. Тактовые импульсы от генератора 5 через схему «И 11 поступают на схему «ИЛИ 6 и на вход обратного счета счетчика /. С выхода схемы «ИЛИ 6 импульсы поступают на регистр 2, производя в нем сдвиг записанного

двоичного числа X. При этом в счетчике / производится вычитание из начального значения числа разрядов п по единице в каждом такте, до выхода из регистра 2 самого старшего значащего разряда числа X, в результате чего триггер 7 перебрасывается в нулевое состояние. Выходной сигнал триггера 7 закрывает схемы «И 11. Вычисление окончено, и в счетчике / теперь загрисано число к, равное значению характеристики искомого логарифма, а в сдвигающем регистре 2 записано приближенное значение его мантиссы (фиг, 2, б), занимающее все разряды регистра 2. Для вычисления антилогарифма (т. ё. для потенцирования), в исходном состоянии все ячейки регистров, счетчика, триггеры 7 и 8 устанавливаются в нулевое положение. В ячейку сдвигающего регистра 2, находящуюся слева от двоичиой занятой, записывается «логическая единица (фиг. 3, а). Затем в дробную часть сдвигающего регистра 2 р двоичном коде заносится значение мантиссы X логарифма, а в регистр характеристик 3 - значение характеристики к логарифма (фиг. 3, б). Для вычисления антилогарифма триггер 8 сигналом по входу 13 устанавливается в единичное состояние, а его выходной сигнал открывает по потенциальному входу схемы «И 9 и 10. Импульсы генератора 5 подаются па схему «И 9, через которую они поступают на схему «ИЛИ (5, а с выхода схемы «И 6 - на сдвигающий регистр 2, а также через схему «И 10 - на вход прямого счета счетчика 1. После поступления к импульсов на счетчик и на сдвигающий ре гистр 2, число в счетчике / становится равным к, т. е. характеристике логарифма, записанной в |регистре характеристик 5, в результате чего срабатывает схема сравнения 4. Выходной сигнал схемы сравнения 4 перебрасывает триггер 8 в нулевое состояние, в результате чего схемы «И 9 к 10 закрываются. Вычисление окончено, и в сдвигающем регистре теперь записано число Y, равное приближенному значению антилогарифма для заданного логарифма (фиг. 3, в). Предмет изобретения Устройство для преобразования двоичных кодов, содержащее регистр сдвига, регистр характеристик, реверсивный счетчик, схему сравнения, генератор тактовых импульсов, два триггера, три схемы «И и схему «ИЛИ, причем выходы реверсивного счетчика и регистра характеристик соединены со входами схемы сравнения, выход которой соединен со входом первого триггера, выход первого триггера через первую схему «И соединен со входом реверсивного счетчика, отличающееся тем, что, с целью расщирения функциональных возможностей, первые входы второй и третьей схем «И соединены с выходом генератора тактовых и.мпульсов, выход первого триггера соединен со вторым входом второй схемы «И, выход второго триггера соединен со вторым входом третьей схемы «И, выход второй схемы «И соединен с первым входом схемы «ИЛИ, выход третьей схемы «И соединен со вторым входом схемы «ИЛИ и со входом обратного счета реверсивного счетчика, а выход сдвигающегося регистра соединен со входом второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПОТЕНЦИРОВАНИЯ ЛОГАРИФМОВ ПО ОСНОВАНИЮ ДВА | 1971 |

|

SU304574A1 |

| Устройство для преобразования двоичных чисел | 1973 |

|

SU446054A1 |

| Устройство для потенцирования | 1976 |

|

SU633017A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Устройство для вычисления логарифмов | 1972 |

|

SU479110A1 |

| Устройство для вычисления логарифмов чисел | 1981 |

|

SU972504A1 |

| Устройство для вычисления логарифмов | 1987 |

|

SU1434429A1 |

| Устройство для потенцирования логарифмов по основанию два | 1982 |

|

SU1020819A2 |

| Устройство для логарифмирования двоичных чисел | 1977 |

|

SU696445A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 2016 |

|

RU2633095C1 |

Т ГТ

л р - г

л к

I)

Даты

1972-01-01—Публикация