Изобретение относится к вычислительной технике, в частности к специализированным устройствам, и предназначено для преобразования двоичных чисел по логарифмической зависимости. Устройство может быть применено для нахождения логарифмов по основанию два чисел, представленных двоичным кодом.

Известно устройство для логарифмирования двоичных чисел [АС 696445 СССР, 1979], содержащее сдвигающие регистры, реверсивный счетчик, сумматоры, схему управления и логические элементы. Его недостатком является представимость результата в коде, отличном от двоичного.

Наиболее близким техническим решением к заявляемому изобретению является цифровое устройство для логарифмирования двоичных чисел [448459 СССР, 1975]. Оно содержит регистр, сдвигающий регистр, схему управления, триггер, элемент И и ИЛИ, два сумматора и запоминающий блок, причем выход сдвигающего регистра соединен с входом первого сумматора, выход этого сумматора соединен с входом сдвигающего регистра, другие выходы первого сумматора соединены с входом элемента ИЛИ, с входом элемента И и первым входом схемы управления; выход схемы элемента ИЛИ соединен с вторым выходом схемы управления и другие входом элемента И; выход элемента И соединен с третьим входом схемы управления, выходы которой соединены соответственно с входами управления триггера, запоминающего блока, обоих сумматоров и регистров, а выход запоминающего блока соединен с входом регистра, выход которого подключен к входу второго сумматора.

Недостатком этого устройства являются излишние аппаратные затраты на его реализацию.

Задачей изобретения является разработка цифрового устройства для логарифмирования двоичных чисел.

Техническим результатом настоящего изобретения является сокращение аппаратных затрат и упрощение схемы управления цифрового устройства для логарифмирования двоичных чисел.

Технический результат достигается тем, что в цифровом устройстве для логарифмирования двоичных чисел, содержащем два сумматора, запоминающий блок, регистр, сдвигающий регистр, триггер, элемент ИЛИ, схему управления, выход которой соединен с управляющим входом регистра и сдвигающего регистра, выход которого соединен с входом первого сумматора, выход этого сумматора соединен с входом сдвигающего регистра, другие выходы сумматора соединены с входом элемента ИЛИ и первым входом схемы управления; выход элемента ИЛИ соединен с вторым входом схемы управления, выходы которой соединены соответственно с входами управления триггера, запоминающего блока, обоих сумматоров, а выход запоминающего блока соединен с входом регистра, выход которого подключен к входу второго сумматора, сокращены аппаратные затраты за счет исключения элемента И и третьего входа схемы управления.

Исключение элемента И с его связями с другими блоками устройства к упрощению схемы управления за счет устранения ее третьего входа позволили избежать лишних аппаратных затрат и упростить конструкцию всего устройства.

Это является новым техническим решением, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное цифровое устройство для логарифмирования двоичных чисел промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

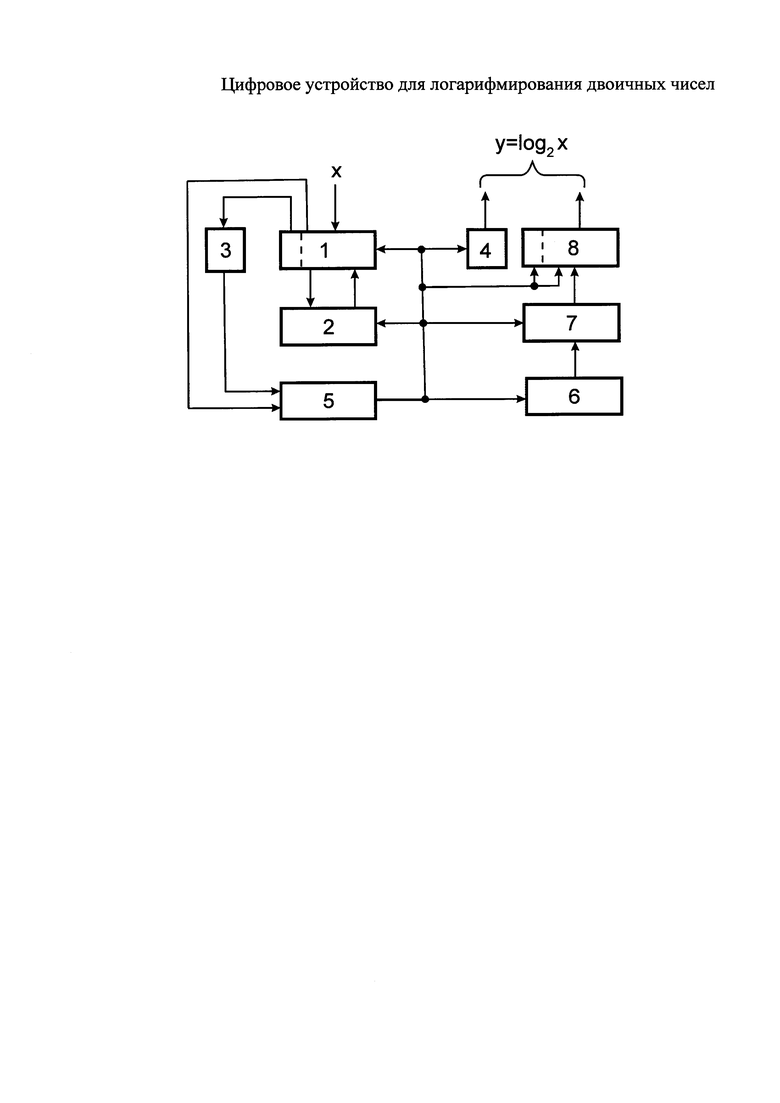

На фигуре показана блок-схема предлагаемого устройства.

Сумматор 1 соединен со сдвигающим регистром 2, выход которого подключен к входу сумматора 1, своими выходами сумматор 1 связан с входом элемента ИЛИ 3 и входом схемы 5 управления, выход элемента ИЛИ 3 соединен с вторым входом схемы 5 управления. Выход запоминающего блока 6 связан с входом регистра 7, выход которого соединен с входом второго сумматора 8. Выход схемы 5 управления подключен к входам сдвигающего регистра 2, регистра 7, запоминающего блока 6, триггера 4 сумматора 1 и второго сумматора 8.

Числа в устройстве представляются в форме с фиксированной запятой, обмен информацией между отдельными блоками осуществляется параллельным кодом.

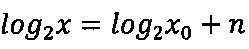

Известно, что двоичное число x в нормализованной форме имеет вид

где x0 - мантисса нормализованного числа (при этом 0,5≤х0<1). Логарифмирование дает

Отсюда видно, что логарифм числа x равен сумме логарифма мантиссы этого числа х0 и значения показателя степени у двойки, численно равного количеству сдвигов числа х при его нормализации, т.е. при приведении его к виду (1).

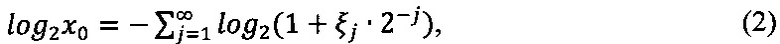

Можно выбрать такую последовательность значений логарифмов, что

где

Алгоритм определения необходимой последовательности находится потенцированием уравнения

находится потенцированием уравнения

Подбор значений  производится с помощью сумматора 1 и сдвигающего регистра 2 последовательным образованием произведений х0(1+2-1)…x0(1+2-n) и анализом значений старшего знакового разрядов сумматора 1 с помощью схемы управления 5.

производится с помощью сумматора 1 и сдвигающего регистра 2 последовательным образованием произведений х0(1+2-1)…x0(1+2-n) и анализом значений старшего знакового разрядов сумматора 1 с помощью схемы управления 5.

Устройство работает в два этапа: этап нормализации числа х, т.е. приведения его к виду (1), и этап определения значений xj по уравнению (3).

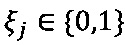

При этом справедливо

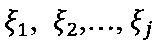

в случае xk<1 в уравнении (4) сомножитель (1+2-k) сохраняется, а из запоминающего блока 6 в сумматор 8 заносится константа

Если же xk≥1, то обращение к запоминающему блоку 6 для извлечения константы αk не происходит, а в уравнении (3) сомножитель (1+2-k) заменяется на следующий очередной (1+2-(k+1)).

В исходном состоянии ячейки сумматоров и регистров находятся в нулевом положении. В сумматор 1 заносится двоичное число jc. Элемент ИЛИ 3 анализирует состояние разрядов сумматора 1, отведенных для записи целой части числа и находящихся слева от двоичной запятой. В зависимости от значения целой части числа х элемент ИЛИ 3 воздействует на вход схемы 5 управления, с выхода которой поступает соответствующий сигнал на вход триггера 4 и устанавливает его либо в минус (целая часть числа х=0), либо в плюс (целая часть числа х>0).

Операция нормализации числа x осуществляется следующим образом.

Необходимость нормализации и направление сдвига числа х в сумматоре 1 определяется схемой 5 управления и элементом ИЛИ 3. Если целая часть числа х≠0, то как минимум на один или несколько входов элемента ИЛИ 3, у которой количество входов соответствует количеству ячеек сумматора 1, отведенных для целой части числа х, поступает сигнал, соответствующий единичному состоянию одной или нескольких ячеек сумматора 1. Выходной сигнал элемента ИЛИ 3 поддается на вход схемы управления 5, с ее выхода поступают импульсы, производящие сдвиг числа х в сумматоре 1 вправо до тех пор, пока старший значащий разряд числа х займет первую справа от запятой ячейку сумматора 1. Выход этого разряда сумматора 1 соединен с входом схемы 5 управления и при появлении единицы в этом разряде схема 5 управления прекращает подачу импульсов сдвига.

Если целая часть числа х равна нулю, возможны два случая в зависимости от значения (1 или 0) старшего разряда дробной части числа. Когда этот разряд равен единице, с выхода этой ячейки сигнал поступает на вход схемы 5 управления как запрещающий для импульсов сдвига. Операция нормализации не производится, так как число x уже представлено в нормализованной форме.

Во втором случае с этого разряда сумматора 1 (находящегося в нулевом состоянии) сигнал запрета на вход схемы 5 управления не поступает и с ее выхода на вход сумматора 1 подаются импульсы, производящие сдвиг числа х влево до появления единицы в ячейке сумматора 1, отведенной для старшего разряда дробной части числа x. При появлении единицы в этом разряде на вход схемы 5 управления поступает сигнал запрета, соответствующий окончанию процесса нормализации числа.

Количество сдвигов при нормализации числа х подсчитывается старшими разрядами второго сумматора 8, находящимися слева от двоичной запятой. Разряды второго сумматора 8, находящиеся справа от запятой, предназначены для фиксирования значения мантиссы логарифма числа х. На этом заканчивается первый этап работы устройства.

Второй этап работы устройства состоит из ряда последовательных шагов, каждый из которых обеспечивает постепенное наращивание членов произведения в уравнении (3). Первый шаг: мантисса нормализованного числа x из сумматора 1 переписывается в сдвигающий регистр 2 с сохранением содержимого сумматора. Содержимое регистра 2 сдвигается вправо на один разряд и подсуммируется к содержимому сумматора 1.

x1-х0+х0⋅2-1=x0(1+2-1)

При х1<1, что анализируется элементом ИЛИ 3, из запоминающего блока 6 производится выборка первой константы α1=log2(1+2-1), значение которой заносится в регистр 7 и передается во второй сумматор 8 в прямом коде, если число х, логарифм которого определяется, меньше единицы, как в дополнительном коде при х≥1. Преобразование в дополнительный код производится в регистре 7. Если результат суммирования х1≥1, то выборки первой константы α1 из запоминающего блока 6 не происходит.

Направление второго шага определяется значением х1, которое анализируется элементом ИЛИ 3. Если х1<1, то содержимое сумматора 1, равное х0(1+2-1), передается в сдвигающий регистр 2 и сдвигается вправо на два разряда. После этого содержимое сдвигающего регистра 2, равное х0(1+2-1)⋅2-2, передается на сумматор 1 для подсуммирования. В результате в сумматоре 1 оказывается число х2=х0(1+2-1)(1+2-2).

Если содержимое сумматора 1 после первого шага х1 оказывается больше или равно единице, то в уравнении (3) член (1+2-1) должен быть заменен следующим за ним членом х0(1+2-2). Для этого содержимое регистра 2х0⋅2-1 сдвигается вправо на один разряд и полученное значение х0⋅2-2вычитается из содержимого сумматора 1 х2=х0(1+2-1)-х0⋅2-2=х0(1+2-2).

Третий шаг по аналогии с вторым шагом начинается с анализа результата, полученного на втором шаге. Если х2<1, следует выборка из запоминающего блока 6 очередной константы α2=log2(1+2-2) и передача ее во второй сумматор 8, а содержимое сумматора 1 вводится в сдвигающий регистр 2 и сдвигается на три разряда вправо с последующим подсуммированием с содержимым сумматора для получения следующего значения xj

х3=x0(1+2-1)(1+2-2)(1+2-3) или х3=x0(1+2-2)(1+2-3).

Если в результате второго шага получено х2≥1, ранее хранившееся в сдвигающем регистре 2 число х0(1+2-1)2-2 (при х1<1) или х02-2 (при x1≥1) сдвигается вправо еще на один разряд и подсуммируется к содержимому сумматора 1

х3=x0(1+2-1)(1+2-2)-х0(1+2-1)2-3=х0(1+2-1)(1+2-3)

или

х3=х0(1+2-2)-х02-3=х0(1+2-3).

Последующие шаги происходят аналогично описанным и начинаются с анализа содержимого сумматора 1, полученного при предыдущем шаге.

После выполнения всех шагов вычисления во втором сумматоре 8 фиксируется значение .

.

Полное значение log2x выдается с триггера 4 (знак), целая и дробная части логарифма выдается со второго сумматора 8.

Таким образом, исключение элемента И (наличествующего у прототипа) и упрощение схемы 5 управления сократили аппаратные затраты и упростили конструкцию цифрового устройства для логарифмирования двоичных чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Устройство для логарифмирования чисел | 1980 |

|

SU926655A1 |

| Устройство для вычисления логарифмов двоичных чисел | 1981 |

|

SU1023324A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Устройство для логарифмирования двоичных чисел | 1978 |

|

SU767755A1 |

| Устройство для логарифмирования | 1981 |

|

SU962926A1 |

Изобретение относится к вычислительной технике и предназначено для преобразования двоичных чисел по логарифмической зависимости. Технический результат заключается в сокращении аппаратных затрат и упрощении схемы управления. Устройство содержит два сумматора, регистр и сдвигающий регистр, триггер, элемент ИЛИ, схему управления, запоминающий блок, содержащий константы типа log2(l+2-i) и связанный через регистр с сумматором. Кроме того, схема управления связана со всеми блоками устройства. 1 ил.

Цифровое устройство для логарифмирования двоичных чисел, содержащее два сумматора, запоминающий блок, регистр, сдвигающий регистр, триггер, элемент ИЛИ, схему управления, выход которой соединен с управляющим входом регистра и сдвигающего регистра, выход которого соединен с входом первого сумматора, выход этого сумматора соединен с входом сдвигающего регистра, другие выходы сумматора соединены с входом элемента ИЛИ и первым входом схемы управления; выход элемента ИЛИ соединен с вторым входом схемы управления, выходы которой соединены соответственно с входами управления триггера, запоминающего блока, обоих сумматоров, а выход запоминающего блока соединен с входом регистра, выход которого подключен к входу второго сумматора.

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Цифровое логарифмирующее устройство | 1980 |

|

SU918946A1 |

| Устройство для вычисления логарифмов двоичных чисел | 1981 |

|

SU1023324A1 |

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2017-10-11—Публикация

2016-07-05—Подача