Изобретение относится к цифровой вычислительной технике и может быть использовано в разли гных автоматических и телемеханических устройствах.

Известно устройство, содержащее счетчик характеристики, дешифратор характеристики, первый и второй дешифраторы, счетчик мантиссы, причем выход переноса счетчика мантиссы соединен с входом счетчика характеристики , выходы которого соединены с входами дешифратора характеристики, выходы которого соединены с первой группой входов первого дешифратора, выходы счетчика мантиссы соединены с информационными входами второго дешифратора, входная шина устройства соединена с входом делителя частоты, выходы которого соединены с второй группой входов первого дешифратора, выходы которого соединены с входами элемента ИЛИ-НЕ, выход которого соединен с управлякидим входом второго дешифратора и первым входом элемента И-НЕ, второй и третий входы которого соединенны соответственно с первым и вторым входами второго дешифратора ,

Основными недостатками устройства являются сложность его реализации.

возможно вычисление логарифмов чисел, представленных только унитарным ко дом низкая точность вычислений чисел меньше 16.

Наиболее близким к изобретению по технической сущности является цифровое устройство для вычисления логарифмов чисел, содержащее элемент И, первый вход которого является такти10РУ1МДИМ, а выход соединен со счетным входом вычитающего счетчика и со сдвигающим входом регистра сдвига, управляющие входы которых соединены с источником управляющего сигнала,

15 восьмой выход регистра сдвига соединен с входом элемента НЕ, с первого по пятый входы регистра сдвига соединены с первым по пятый входами источника зходной информации 2.

20

Основным недостатком этого устройства является невозможность вычисления антилогарифмов чисел.

Цель изобретение - расшир ение класса решаемых задач за счет дополнительного вычисления антилогарифмов чисел.

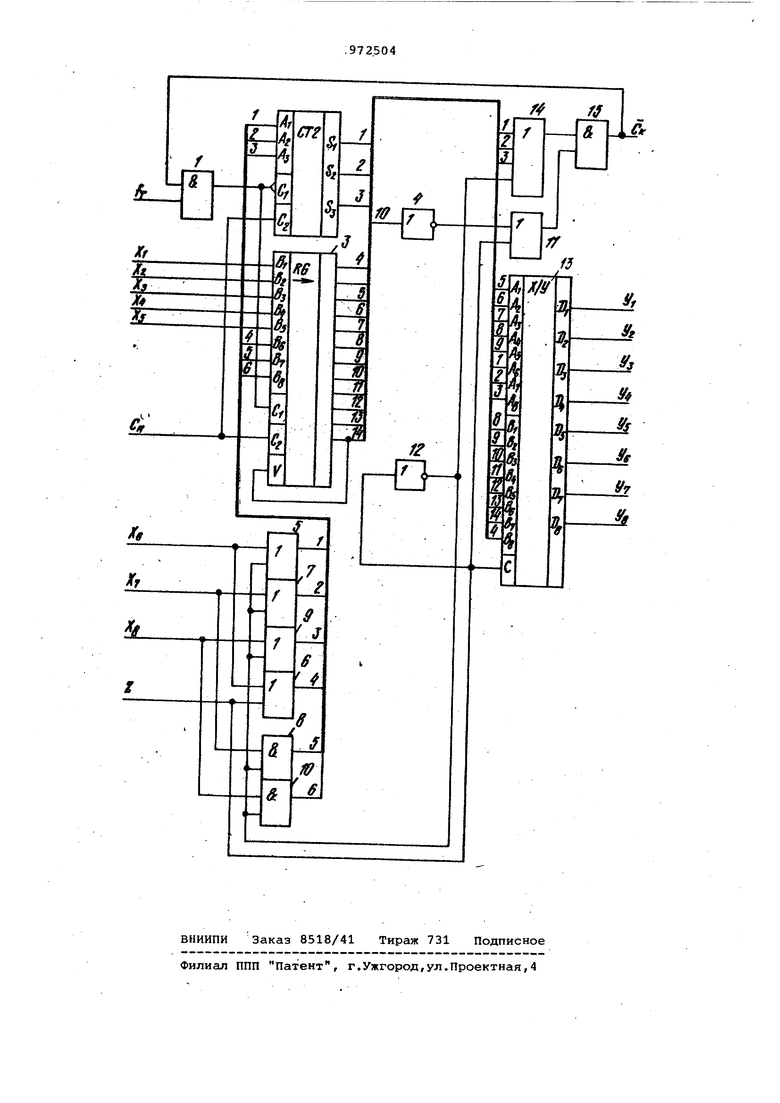

Поставленная цель достигается тем, что в устройстве содержащее первый элемент И, вычитающий счетчик, регистр сдвига и первый элемент НЕ, вход которого соединен с выходом восьмого разряда регистра сдвига, информационные входы разрядов с пер- вого по пятый которого соединены с входами -cooTBeTCTBeHHO с первого по пятый разрядов ар-гумента устройства, вход тактовой частоты которого соеди нен с первым входом первого элемен-. та И, выход которого соеданен со счетным входсм вычитающего счетчика iH входом сдвига регистра сдвига, управляющие входы которых соединены с входом синхронизации устройства, введены второй элемент НЕ, шесть элементов ИЛИ, три элемента И и коммутатор, управляющий вход которого соединен о первыми входами первого-и второго : элементов ИЛИ, входом задания режима: устройства и через второй элемент НЕ с первыми входами третьего, четвертс го, пятого и шестого элементов ИЛИ и второго и третьего элементов И, выходы третьего, четвертого .и пятого элементов ИЛИ соединены соответственно с первым, вторым и третьим информационными входами вычитающего счетчика, первый, второй и третий выхода которого соединены с входами с второго, по четвертый шестого элемента ИЛИ и соответственно с входами разрядов шестого, седьмого и восьмого первой группы коммутатора, входы разрядов с первого по пятый первой группы коммутатора соединены соответственно с выходами разрядов с третьего по седьмой регистра сдвига, выход первого разряда и выходы разрядов jc шеотого по двенадцатый которого соединены соответгственно с входом восьмого i разряда и.с входами разрядов с первого по седьмой второй группы коммутатора, выходы которого являются выходами устройства, второй вход и выход первого элемента ИЛИ соединены соответственно с выходом первого элемента НЕ и первым входом четвертого элемента И, второй вход и выход которого соединены соответственно с выходом шестого элемента ИЛИ и вторым , входом первого элемента И, выходел второго элемента ИЛИ, второго и третьего элементов исоединены соответственно с информационными входами разрядов с шестого по восьмой регистра сдвига, вход последовательного ввода которого соединен с выходом двенадцатогоразряда регистра сдвига вторые входы второго и третьего эле- ментов ИЛИ соединены с входом шестого разряда аргумента устройства, вход седьмого разряда аргумента которого соединен с вторыми входами четверто- го элемента ИЛИ и Ьторого элемента И вторые входы пятого элемента ИЖ и третьего элемента И соединены с входом восьмого разряда аргумента устройства. На чертеже представлена блок-схема устройства. Устройство содержит элемент И 1, итающий счетчик 2, регистр 3 сдв; элемент НЕ 4, элементы ИЛИ 5-7, мент И 8, элемент ИЛИ 9, элемент элемент ИЛИ 11, элемент НЕ 12, мутатор 13, элемент ИЛИ 14 и элет И 15, На вход устройства подеиотся такующий сигнал от генератора тактищего сигноша, сигнал от датчика ровой информации и сигнал задания има.работы. В зависимости от значения сигналеора режима работы 2, задаваемого зада1рщем устройстве (Z или T.-U выходе устройства сигналы 5 -Ур еняются по уравнениям Y,, .0з-ь2. D ; Y,, . + Z.Dg; ,i-Z-D,o ; Y, Z-S.Z.D. e f-f ,,tZ.D, ; .Z-0, r выходной сигнал устрог--прямое и инверсное значение сигнала выбора режима работы; D,,,0,-D - значения выходного сиг 1 П нала регистра сдвига; -значения выходного сит нала вычитающего счетчика. Сигналы, поступающие на вход выающего счетчика 2, зависят от знг, ия сигнала Z и определяются уравияг иA,, ;(2) . Сигналы, поступающие на вход ретра 3 сдвига, зависят от значения нала Z и определяются уравнениямЕ В, Х, , ,, . В, BJ Z.Xв. С выхода элемента И 15 снимается нал об окончании работы устройстна

(), который определяется уравнением

C ()(S.S..S.Z) , (4)

Все описанные алгоритмы реализуются в устройстве за счет выполнения 5 внутренних связей между eiro элементами.

Устройство для вычисления логарифмов чисел работает следующим образом.10

Для осуществления логарифмирования сигнал выбора режима устанавливается равным нулю (). При этом управлякяцим сигналом производится запись числа X в регистр 3 сдвига 15 и установки вычитакнцего счетчика 2 . в единичное положение путем предварительной установки на его информационных входах логических единиц в cooт ветствии с уравнением (2),20

Если соблюдается соотношение , то с восьмого выхода регистра 3 сдвига поступает сигнал и сигнал в соответствии с уравнением (4). В результате импульсы тактовой 25 частоты f проходят на регистр 3 сдвига и вычитающий счетчик 2 и тем сагллм производится сдвиг содержимого регистра .3.сдвига в сторбну старших разрядов и уменьшение содержимого вы- JQ читающего счетчика 2. Сдвиг осущесть вляется до тех пор, пока на восьмом выходе регистра 3 сдвига не появится сигнал логической единицы, которым совместно с сигналом производите , ся блокировка прохожденияимпульсов . тактовой частоты на регистр 3 сдвига и вычитающий счетчик 2. При вычисление логарифма числа X заканчивагется. Значение характеристики лога рифма числа X берется с выхода вычи- тающего счетчика 2 и передается коммутатором устройства на входы с шестого по восьмой устройства, а значение мантиссы - с третьего по восьмой выходов регистра 3 сдвига передается 45 на выходы с первого .по пятый устройства,

Если исходное число X содержит логическую единицу в старшем разряде, JQ т.е. , то при йаписи его в регистр 3 сдвига на выходе элемента И .. 15 сформируется сигнал и процесс вычисления тем сгцным окончится. С выходов У -yg- снимается значение ман- j, тиссы и с - значение характеристики логарифма по основанию исходного числа X.

В предлагаемом устройстве х актеристика двоичного логарифма определяется номером старшего разряда чис- ла, имеющим значение логической единицы при представлении числа в двоичном нормальном коде. Например, двоичный нормальный код числа 15 имеет вид 00001111.45

Номер старшего разряда, име о1цего значение логической единицы рассматриваемого числа, равен трем, что . ответствует действительности (loglS 3,907). Значение мантиссы опредетяется путем линейной аппроксимации. Максимальное приращение мантиссы равно единице при изменении входного числа X от 2Р до ; где Р - значение характеристики.

Следовательно, коэффициент накло,на аппроксимирующей линии равен

-2f а значение мантиссы равно

(Х-2).

где m - значение мантиссы;

К - коэффициент наклона аппроксимирующей линии, X - входное число/ Р - характеристика числа.

Значение (Х-2Р} является исходным числом без единицы в старшем зряде а значение m - форма представления значения {Х-2 ) в двоичном нормаль ном коде с фиксированной -запятой после старшего разряда.

Значение мантиссы логарифма числа 15 будет в двоичном коде 0,111, или в десятичном 0,875, т.е. двоичный логарифм числа 15 равен

109,,875.

Таким образом, для определения значения двоичного логарифма числа, представленного в двоичном коде, достаточно определить порядковый номер единицы в старшем значащем разряде, что является характеристикой лог рифма, а в качестве мантиссы Дерется исходное число за вычетом значения старшего знач;апего разряда,т.е. значение двоичного логарифма определяется по формуле „ ,р

У.1.-4.Р

2Р где , Х./2Р.

Для осуществления антилогарифмирования сигнал выбора режима равен единице (). На входы подается значение характеристики исходного числа, а на выходы . - значение мантиссы.

При формировании управляющего сигнала Су(1 производится занесение рактеристики в вычитающий счетчик 2 и мантиссы X -X в младшие пять разрядов регистра сдвига 3 ().

Если значение характеристики р .0, то с выхода элемента И 15 поступает сигнал логической единицы на вход элемента и 1. В результате импульсы тактовой частоты f- цроходят на регистр 3 сдвига и вычитающий счетчик 2 и тем самым производится сдвиг содержимого регистра 3 сдвига в сторону старших разрядов и уменьшение содержимого вычитающего счетчийа 2. Сдвиг осуществляется до тех пор, noKa содержимое счетчика не стане равным нулю. На выходе элемента ИЛИ 14 сформируется сигнал логического нуля который, пройдя через элемент И 15, блокирует прохождение импульсов тактовой частоты fyy, на регистр 3 сдвига и вычитающий счетчик 2. На выходе ; элемента И 15 формируется сигнал 0 0 окончания вычисления антилогарифма. С выходов , 0 регистра 3 i .сдвига, поступает значение антилога-, рифма числа X через коммутатор 13 нА вход устройства. , Значение антилогарифма числа X определяется путем линейной аппроксимйции функции , где X можно пред- i ставить в следующем виде: ,Уи, где Р - характеристика числа, .iri - мантисса. Ири изменении X от Р до (Р+1 приращение функции равно , а коэффициент наклона аппроксимирующей линии ч. и .. - .1. ..:} V {р4-1)-р Аппроксимирующая функция для каж-, дого значения характеристики имеет вид У 2Р-1-Сх-Р).()2 2и+Х-Р: Учитывая, что ( является мантиссой числа X, то для вычисления антилогарифма.по основанию два числа X достаточно значение мантиссы увеличить на единицу и полученный результат увеличить в 2Р, для чего необходимо при представлении значения (.1+Х+р) в двоичном нормальном коде, сдвинуть его на Р разрядов в сторону старших разрядов. Допустим, ,875 или его двоичный эквивалент ).1,11100 . Значение мантиссы ,11100. 1+ХР И-М 1+0,11100 1,11100, (1+Х-Р) 00001111, или . Абсолютная ошибка вычисления логарифма равна , . х-2 о u, log,,X - - -Р. 2У Максимальная ошибка при Х-вйГ 0,08607, что соответствует младшему разряду при восьмиразрядной сетке входного числа,а относительная приведенная погрешность равна ) 1% Абсолютная ошибка вычисления антилогарифма равна , t,(l+X-P). Максимальная абсолютная ошибка пр п , 52 88 . Таким дбразом, максимальная ошибка при значении мантиссы ,5288 равнаДуцаха 0 0861« 2 Р, т.е. меняется от 0,172 до 11,02 при изменении характеристики от 1 до 7, а относительная приведенная погрешность d СО,07-4,. В общем случае, предлагаемое устройство можно реализовать любой 5азрядности. При этом должны соблюдаться следующие условия: 5 1 0-92. 0 2 -S-1; 2; 3, ... , где S - число разрядов вычитающего счетчика; п - число разрядов входной информации ; D - число разрядов регистра сдви га.. Наибольший коэффициент использования элементов устройства будет при , где , 2, 3 ..., т.е, при , 4, 8, 16 и т.д. Учитывая, что при п 16, имеем , , т.е. резкое увеличение аппаратурных затрат, а также, то, что вычисления производятся с точностью до единицы младшего разряда при восьмиразрядной сетке входной информации. Целесообразно предлагаемое устройство выполнять восьмиразрядным, вариант которого представлен на чертеже. Простота и компактность данного устройства позволит использовать его в малогабаритных измерительных цифровых приборах, информационно-измерительных системах и в устройствах управления. Многофункциональность устройства способствует сокращению нот- : менклатуры разрабатываемых и выпускаемых изделий за счет незначительных аппаратурных затрат. Устройство дJЯ вычисления логарифмов и антилогарифмов чисел реализоваг но на интегральных микросхемах серии К155, При типовой частоте время вычисления не более 7 мкс. Формула изобретения Устройство для вычисления логарифмов чисел, содержащее первый элемент И, вычитающий счетчик, регистр сдвига и первый элемент НЕ, вход которого соединен с выходом восьмого разряда регистра сдвига, информационные входы разрядов с первого по пятый которого соединены с входами соответст венно с первого по пятый разрядов аргу-Т мента устройства, вход тактовой частоты которого соединен с первым входом первого элемента И, выход которого соединен со счетным входом вычитающего счетчика и входом сдвига регистра сдвига, управляющие входы которых соединены с входом синхронизации устройства, отличающееся тем,что, с целью расширения класса решаемых задач за счет дополнительного вычисления антилогарифмов чисел в него введены второй элемент НЕ, шесть элементов ИЛИ, три элемента И и коммутатор, управл,яю1ций вход которого соединен с первыми входами первого и второго элементов ИЛИ, входом задания режима устройства и через второй элемент НЕ с первыми входами третьего, четвертого, пятого и шестого элементов ИЛИ и второго и третьего элементов И, выходы третьего , четве }того и пятого элементов ИЛИ соединены соответственно с первым, вторым и третьим информационными входами вычитающего счетчика, первый, второй и третий выходы которого соединены с входами с второго по четвертый шестого элемент ИЛИ и соответственно с входами разрядов шестого, седьмого и восьмого первой группы коммутатора, входы разрядов с первого по пятый первой группы коммутатора соединены соответственно с вйходс1ми разрядов с третьего по седьмой регист ра сдвига,выход первого разряда и вы;ходы разрядов с шестогопо двенадцатый которого соединены соответственно с входом восьмого разряда и с входами разрядов с первого по седьмой второй группы коммутатора, выходы которого 1ЯВЛЯЮТСЯ выходами устройства, второй вход и выход первого элемента ИЛИ соединены соответственно с выходом первого элемента НЕ и первым входом четвертого элемента И, второй вход и выход которого соединены соответсз венно с выходом шестого элемента ЙЛЯ и вторым входом первого.элемента И, выходы второго элемента 1ШИ, второго и третьего элементов И соединены cof ответственно с информационными входами разрядов с шестого по восьмой регистра сдвига, вход последовательного ввода которого соединен с выходом двенадцатого разряда регистра сдвига, вторые входа второго и третьего элементов ИЛИ соединены с входом шестого разряда аргумента устройства,вход седьмого разряда аргумента которого соединен с вторыми входами четвертого элемента ИЛИ и второго элемента И, вторые входы пятого элемента ИЛИ и третьего элемента И coe данeны с входом восьмого разряда аргумента устройства. ; Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство COClP 605211, кл. G Об F 7/556, 1979. 2.Авторское свидетельство СССР по заявке № 2817788/18-24, кл. G 06 F 7/556, 17.07.79 (прототий),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмов | 1987 |

|

SU1434429A1 |

| Устройство для вычисления логарифма числа | 1985 |

|

SU1295390A1 |

| Цифровое устройство для вычисления логарифма числа | 1979 |

|

SU1003082A1 |

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ КОДОВ | 1972 |

|

SU330448A1 |

| Устройство для вычисления функций | 1985 |

|

SU1287150A1 |

| УСТРОЙСТВО для ПОТЕНЦИРОВАНИЯ ЛОГАРИФМОВ ПО ОСНОВАНИЮ ДВА | 1971 |

|

SU304574A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Устройство для вычисления логарифмической функции | 1980 |

|

SU930314A1 |

Авторы

Даты

1982-11-07—Публикация

1981-02-03—Подача