Изобретение относится к области вычислительной техники.

Известны устройства для контроля преобразователей напряжение - код, содержащие источник контрольного напряжения, схему выбора контрольного разряда с триггерами первого и второго контрольного разрядов, двумя схемами «И и двумя схемами неравнозначности и схему разрешения считывания со схемой «ИЛИ, схемой совпадения и выходным триггером, а также схему сравнения.

Цель изобретения - сокращение времени систематического контроля.

Цель достигается тем, что в предлагаемом устройстве одни из входов обеих схем «И и схем неравнозначности соединены с выходом схемы сравнения, входы которой подключены к выходам источника контрольного напряжения, присоединенного входами к выходам триггеров первого и второго контрольного разрядов, а входы последних соединены соответственно с выходом первой схемы «Pi и первой схемы неравнозначности, первые входы которых присоединены к выходу источника тактовых импульсов; второй выход триггера первого контрольного разряда соединен через вторую схему «И с одним из входов схемы «ИЛИ, а второй выход триггера второго контрольного разряда подключен через вторую схему неравнозначности к другому

входу схемы «ИЛИ, выход которой присоединен ко входу выходного триггера через первый вход схемы совпадения, а второй вход последней присоединен ко второму выходу

источника тактовых импульсов.

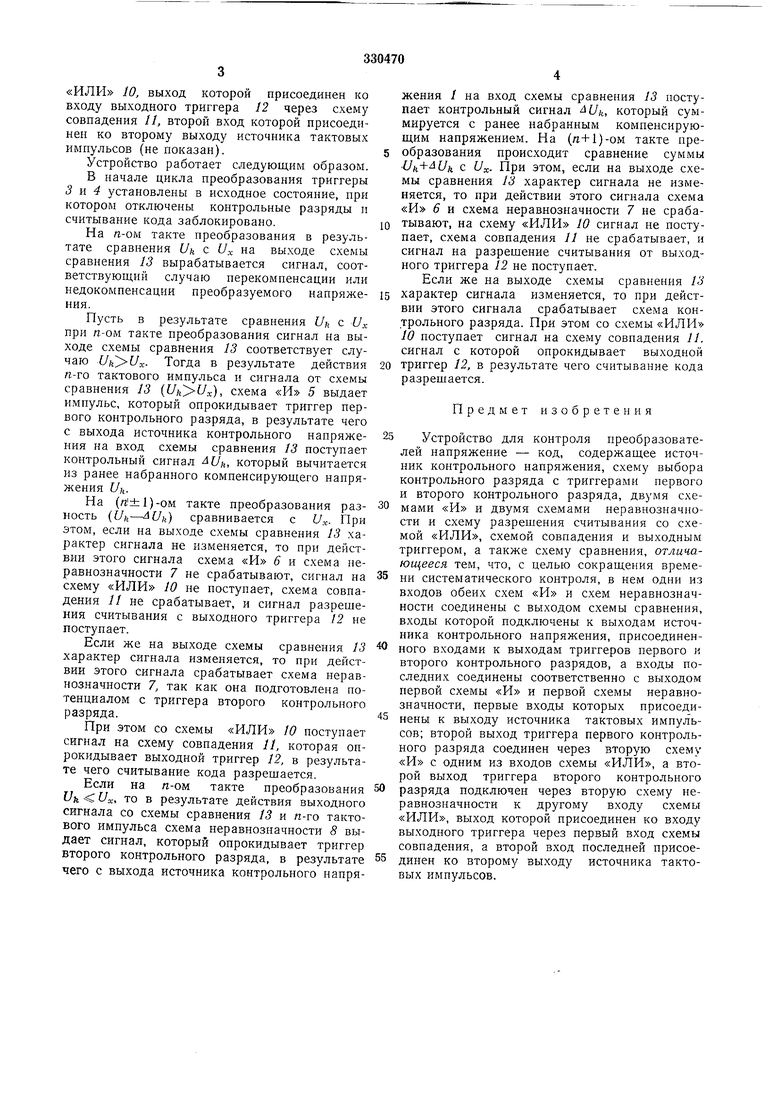

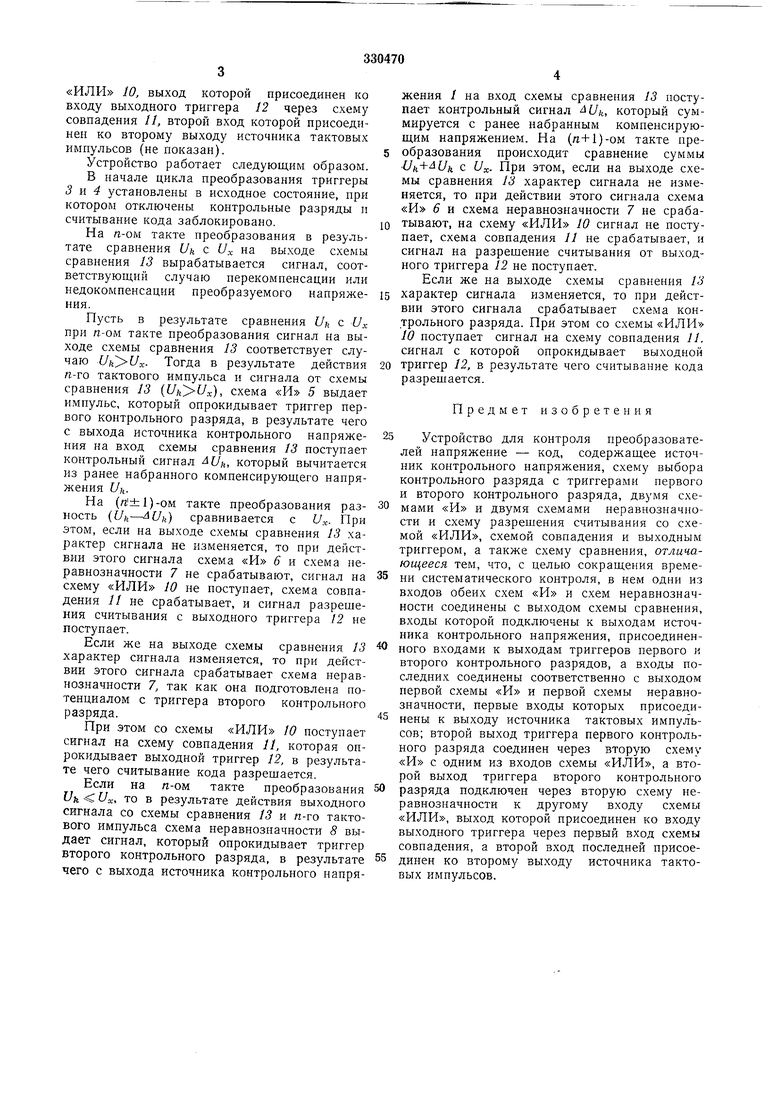

Блок-схема устройства приведена на чертеже.

Устройство содержит соединенные между собой источник /, контрольного напряжения.

0 схему 2 выбора контрольного разряда с триггерами первого 3 и второго 4 контрольного разрядов, двумя схемами «И 5 и 5, двумя схемами неравнозначности 7 и S и схему 9 разрешения считывания со схемой «1-1ЛИ

10, схемой совпадения 7/ и выходным триггером 12, а также схему, сравнения 13, в.ходы которой подключены к выходам источника контрольного напряжения, присоединенного входами к выходам триггеров первого 3 и вто0рого 4 контрольного разрядов. Входы последних соединены соответственно с выходом схемы «И 5 и схемы неравнозначности 8, первые входы которых присоединены к выходу источника тактовых импульсов.

Кроме того, второй выход триггера 3 первого контрольного разряда соединен через схему «И 6 с одним из входов схемы «ИЛИ 10, а второй выход триггера второго контрольного разряда 4 подключен через схему неравнозначности 7 к другому входу схемь

«ИЛИ 10, выход которой присоединен ко входу выходного триггера 12 через схему совпадения //, второй вход которой присоединен ко второму выходу источника тактовых импульсов (не показан).

Устройство работает следующим образом.

В начале цикла преобразования триггеры 3 и 4 установлены в исходное состояние, при котором отключены контрольные разряды и считывание кода заблокировано.

На «-ОМ такте преобразования в результате сравнения Uh с U на выходе схемы сравнения 13 вырабатывается сигнал, соответствующий случаю перекомпенсации или недокомпенсации преобразуемого напряжения.

Пусть в результате сравнения U с Их при «-ОМ такте преобразования сигнал на выходе схемы сравнения 13 соответствует случаю . Тогда в результате действия п-го тактового импульса и сигнала от схемы сравнения 13 (), схема «И 5 выдает импульс, который опрокидывает триггер первого контрольного разряда, в результате чего с выхода источника контрольного напряжения на вход схемы сравнения 13 поступает контрольный сигнал Uh, который вычитается из ранее набранного компенсирующего напряжения L/h.

На (rt±l)-oM такте преобразования разность (t/fe- f/fe) сравнивается с Ux. При этом, если на выходе схемы сравнения 13 характер сигнала не изменяется, то при действии этого сигнала схема «И 6 и схема неравнозначности 7 не срабатывают, сигнал на схему «ИЛИ 10 не поступает, схема совпадения И не срабатывает, и сигнал разрешения считывания с выходного триггера 12 не поступает.

Если же на выходе схемы сравнения 13 характер сигнала изменяется, то при действии этого сигнала срабатывает схема неравнозначности 7, так как она подготовлена потенциалом с триггера второго контрольного разряда.

При этом со схемы «ИЛИ 10 поступает сигнал на схему совпадения //, которая опрокидывает выходной триггер 12, в результате чего считывание кода разрешается.

Если на л-ом такте преобразования Vk Ux, то в результате действия выходного сигнала со схемы сравнения 13 и п-го тактового импульса схема неравнозначности 8 выдает сигнал, который опрокидывает триггер второго контрольного разряда, в результате чего с выхода источника контрольного напряжения / на вход схемы сравнения 13 поступает контрольный сигнал Uk, который суммируется с ранее набранным компенсирующим напряжением. На (л-Ь1)-ом такте преобразования происходит сравнение суммы с Uy. При этом, если на выходе схемы сравнения 13 характер сигнала не изменяется, то при действии этого сигнала схема «И 6 и схема неравнозначности 7 не срабатывают, на схему «ИЛИ 10 сигнал не поступает, схема совпадения 11 не срабатывает, и сигнал на разрешение считывания от выходного триггера 12 не поступает.

Если же на выходе схемы сравнения 13

характер сигнала изменяется, то при действии этого сигнала срабатывает схема контрольного разряда. При этом со схемы «ИЛИ 10 поступает сигнал на схему совпадения 11. сигнал с которой опрокидывает выходной

триггер 12, в результате чего считывание кода разрешается.

Предмет изобретения

Устройство для контроля преобразователей напряжение - код, содержащее источник контрольного напряжения, схему выбора контрольного разряда с триггерами первого и второго контрольного разряда, двумя схемами «И и двумя схемами неравнозначности и схему разрешения считывания со схемой «ИЛИ, схемой совпадения и выходным триггером, а также схему сравнения, отличающееся тем, что, с целью сокращения времеИИ систематического контроля, в нем одни из входов обеих схем «И и схем неравнозначности соединены с выходом схемы сравнения, входы которой подключены к выходам источника контрольного напряжения, присоединенного входами к выходам триггеров первого и второго контрольного разрядов, а входы последних соединены соответственно с выходом первой схемы «И и первой схемы неравнозначности, первые входы которых присоедииены к выходу источника тактовых импульсов; второй выход триггера первого контрольного разряда соединен через вторую схему «И с одним из входов схемы «ИЛИ, а второй выход триггера второго контрольного

разряда подключен через вторую схему неравнозначности к другому входу схемы «ИЛИ, выход которой присоединен ко входу выходного триггера через первый вход схемы совпадения, а второй вход последней присоединен ко второму выходу источника тактовых импульсов.

0m исгпочника щактоУых импульсоб

Л ijcmpoucmSy

Даты

1972-01-01—Публикация