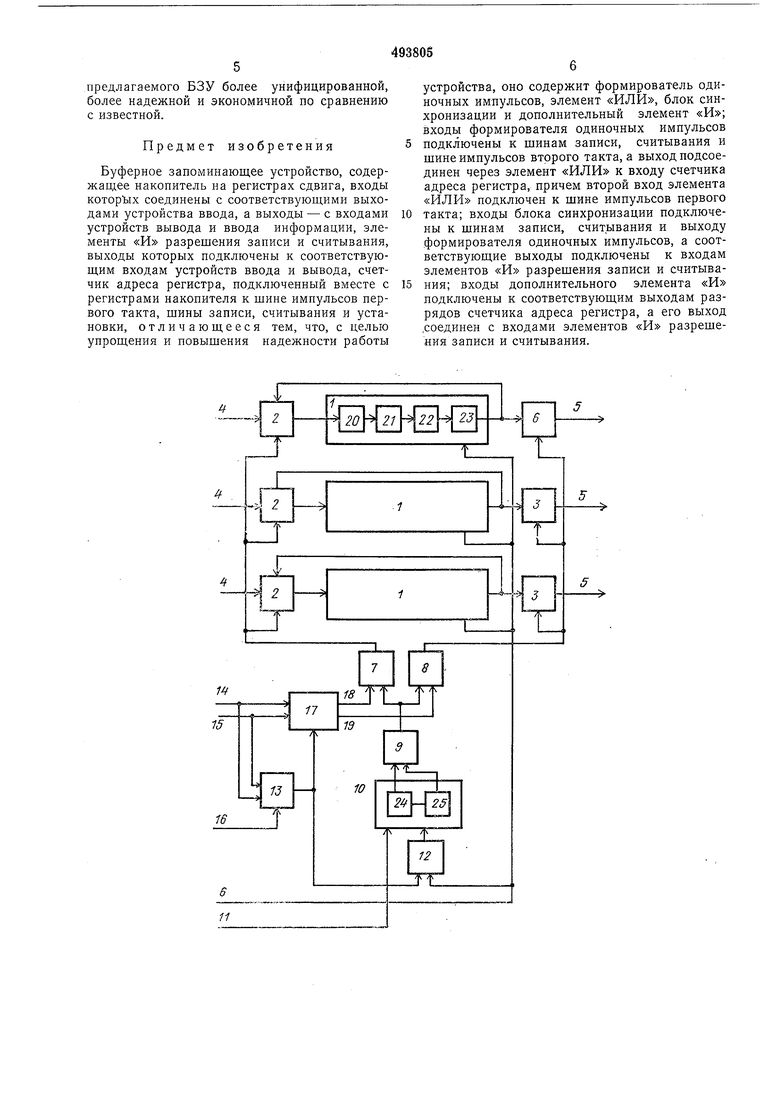

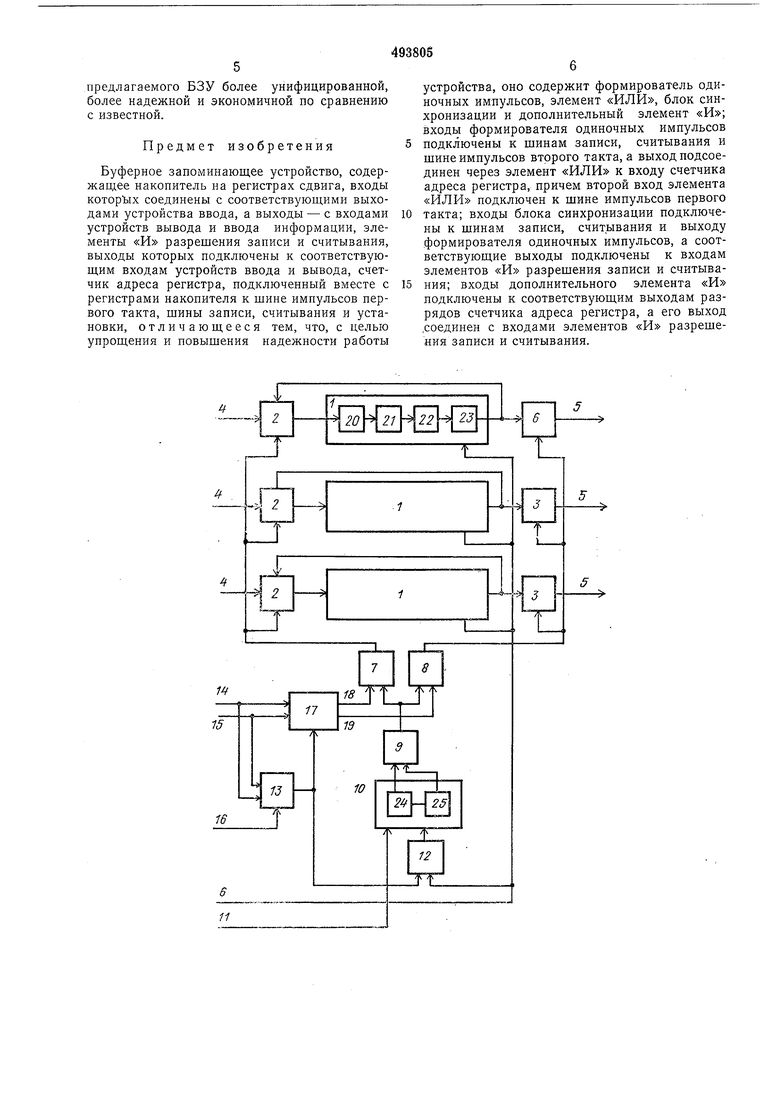

ны 5 вывода. Тактовые входы регистров 1 подключены к шине 6 импульсов первого такта.

Выход элемента «PI 7 разрешения записи подсоединен к входам устройства 2 ввода, а выход элемента «И 8 разрешения считывания - к входам устройства 3 вывода. При этом входы элементов «И 7 и 8 соединены с выходом дополнительного элемента «И 9, входы элемента «И 9 - с соответствующими выходами разрядов счетчика 10 адреса регистра, к которым также подключена шина 11 . установки. Вход счетчика связан с выходом элемента «ИЛИ 12, вход элемента «ИЛИ - с шиной 6 импульсов первого такта и выходом формирователя 13 одиночных импульсов. Входы формирователя соединены с шинами записи 14, считывания 15 и шиной 16 импульсов второго такта. Шины 14, 15 и выход формирователя 13 подключены также к входам блока 17 синхронизации, выход 18 записи- к входу элемента «И 7, выход 19 считывания - к входу элемента «И 8.

Каждый регистр 1 состоит из разрядов 20- 23, а счетчик 10 - из разрядов 24 и 25.

При работе ЗУ в буферном режиме процессы записи и считывания информации обычно чередуются. Для простоты рассмотрим процессы, происходяш,ие при записи информации 1010 лишь в один регистр сдвига (разряд). Работа остальных регистров аналогична.

Когда счетчик 10 занял исходное положение, сигналом «О по шине 11 выходы разрядов 24, 25 счетчика устанавливаются в состояние «О. С приходом тактового импульса по шине 6 оба разряда 24 и 25 переходят в состояние «1, регистрируемое элементом «И 9, на выходе которого появляется сигнал. Если счетчик работает только от импульсов первого такта по шине 6, то элемент «И 9 срабатывает через каждые четыре импульса, отмечая нулевое фазовое состояние счетчика. С приходом информации «1 по шине 4 она поступает на вход устройства 2 ввода. Одновременно по шине 14 записи приходит сигнал записи, он воздействует на формирователь 13 одиночных импульсов, который вырабатывает один импульс, синхронизированный с импульсами второго такта по шине 16.

Этот импульс, пройдя элемент «ИЛИ 12, поступает на вход счетчика 10, изменяя его фазовое состояние, по отношению к «нулевому. Теперь оба разряда 24, 25 переходят в «единичное состояние через три импульса первого такта (четвертый импульс - это импульс формирователя). При переходе разрядов 24, 25 в состояние «Ь срабатывает элемент «И 9 и сигнал с его выхода поступает на входы элементов «И 7 и 8. На другие входы этих схем подаются сигналы из блока 17 синхронизации. Сигнал записи, поступивший на вход блока 17 по шине 14, синхронизируется сигналом формирователя так, что на выходе 18 этого блока появляется сигнал записи лишь по окончании импульса с формирователя. При совпадении сигналов на входе элемента «И 7 разрешения записи он срабатывает и на вход устройства 2 ввода проходит сигнал, разрешающий запись информации «1 в первый разряд (20) регистра 1.

После заполнения регистра, ввиду того, что емкость данного накопителя равна числу состояний счетчика адресов, счетчик снова находится в «нулевом фазовом состоянии и

10 можно начать процесс считывания информации.

С приходом каждого сигнала считывания по шине 15 срабатывает формирователь и импульс с его выхода изменяет шаг за шагом

15 фазовое состояние счетчика. С каждым сигналом считывания срабатывают элемент «И 9 и блок синхронизации, причем сигнал считывания, синхронизированный сигналом формирователя (по заднему фронту), появляется на

20 выходе 19 блока 17.

При совпадении сигналов на элементе «И 8 на его выходе образуется сигнал разрешения считывания, под воздействием которого открывается устройство 3 вывода. Информация, которая в этот момент находилась в последнем разряде (23) регистра, появляется на выходных шинах 5. Во время считывания информация выходит из накопителя в том же порядке, в каком она записывалась (буферный режим работы ЗУ). Длительность выходных сигналов равна или периоду повторения импульсов первого такта или времени между задним фронтом импульса второго такта и задним фронтом рядом стоящего импульса

5 первого такта. Как и во всех циклических ЗУ, в предлагаемом БЗУ минимальное время записи и считывания информации в регистре сдвига. Длительность входных сигналов записи и считывания и информационных сигналов

0 должна быть равна Г+Дтсинхр., где Т - период обращения информации в регистре; Атсинхр. - задержка сигналов записи и считывания в блоке синхронизации. Блок синхронизации легко выполнить, например на двух / - /(-триггерах. На входы / и R одного из них подаются сигналы записи, на входы / и / другого - сигналы считывания, на тактовые входы обоих триггеров - сигналы с выхода формирователя, а па входы

0 К - уровни «О. При таком построении схемы синхронизации единичные сигналы записи и считывания на выходах Q триггеров появляются по окончании импульса с формирователя и оканчиваются с окончанием сигналов записи

5 и считывания. Формирователь представляет собой обычную схему на двух / - /(-(или другого типа) триггерах.

Наличие в БЗУ формирователя одиночных импульсов, элементов «И 9 и «ИЛИ 12, позволившее реализовать фазовый признак для записи и считывания информации в регистр сдвига, дает возможность сократить количество необходимого оборудования для управления накопителем на регистрах и сделать его независимым от емкости БЗУ, сделать схему

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления накопителем на запоминающих элементах с неразрушающим считыванием информации | 1976 |

|

SU643973A1 |

| Буферное запоминающее устройство | 1981 |

|

SU993333A1 |

| Запоминающее устройство | 1979 |

|

SU851491A1 |

| Буферное запоминающее устройство | 1977 |

|

SU720507A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для воспроизведения цифровой информации | 1984 |

|

SU1167645A1 |

| Запоминающее устройство для телеграфного аппарата | 1982 |

|

SU1200343A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для отображения информации | 1978 |

|

SU736144A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

Авторы

Даты

1975-11-30—Публикация

1974-03-27—Подача