ON VI VI 00 СП VI

Изобретение относится к импульсной технике и может быть использовано в измерительных системах и системах автоматизированного управления.

Целью изорбетения является расширение диапазона преобразуемых частот при сохранении точности преобразования.

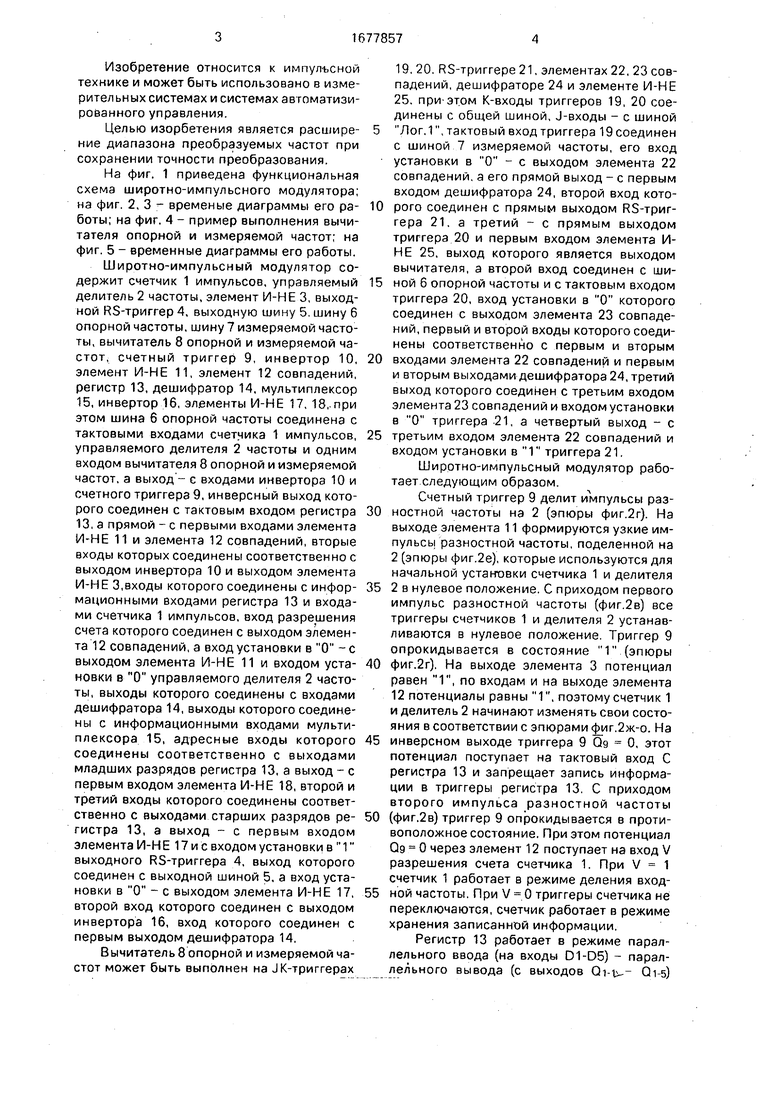

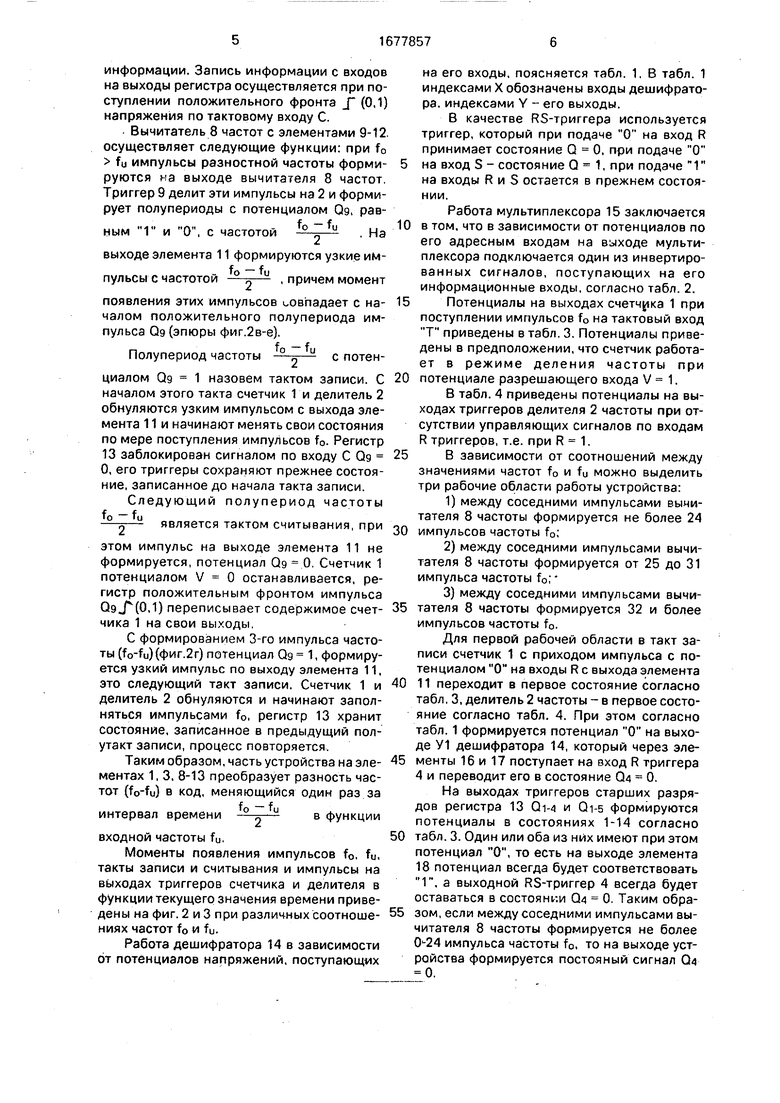

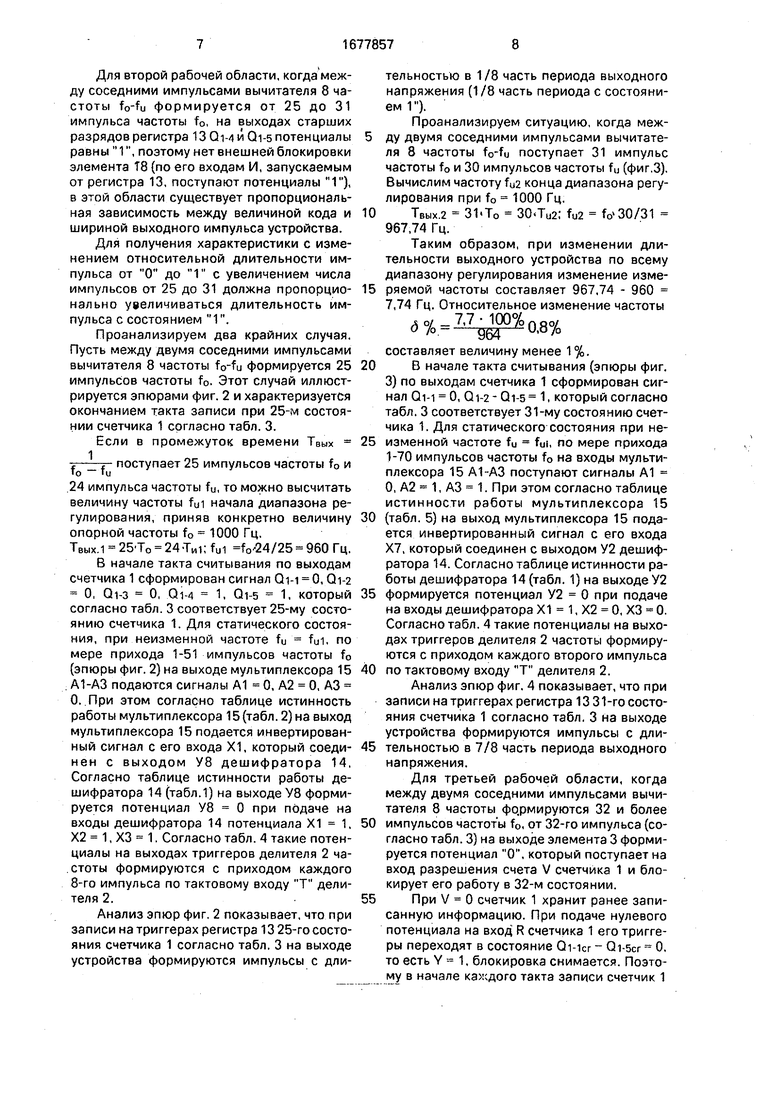

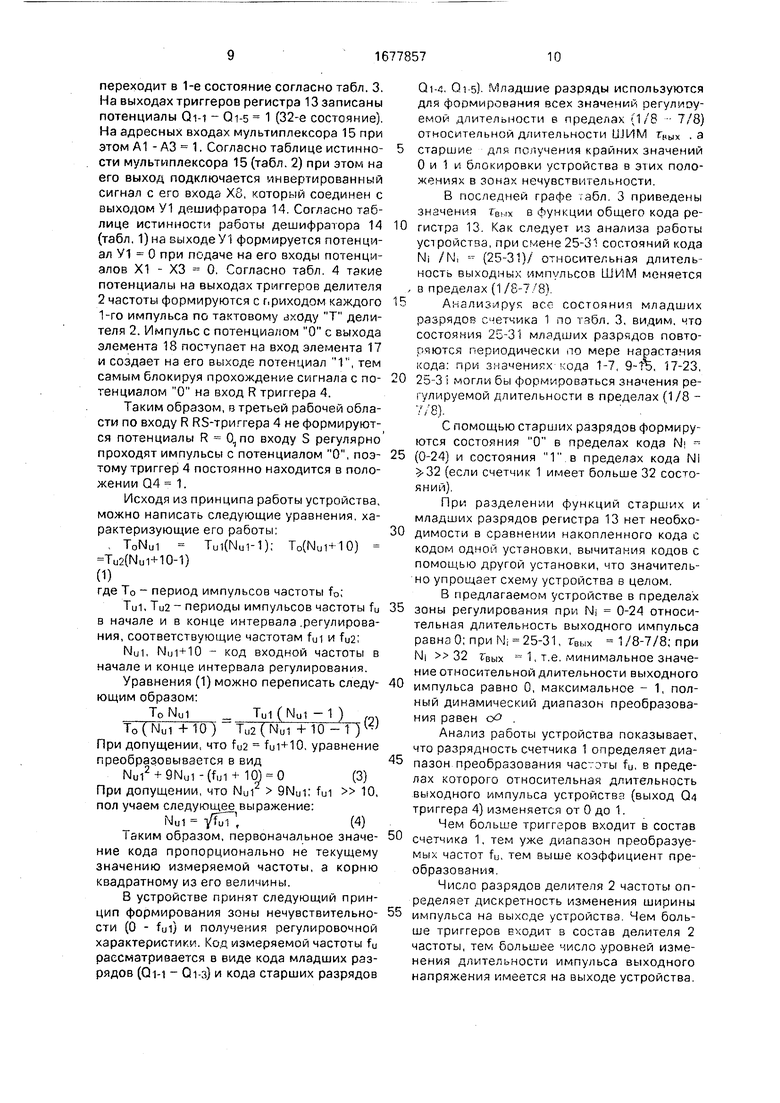

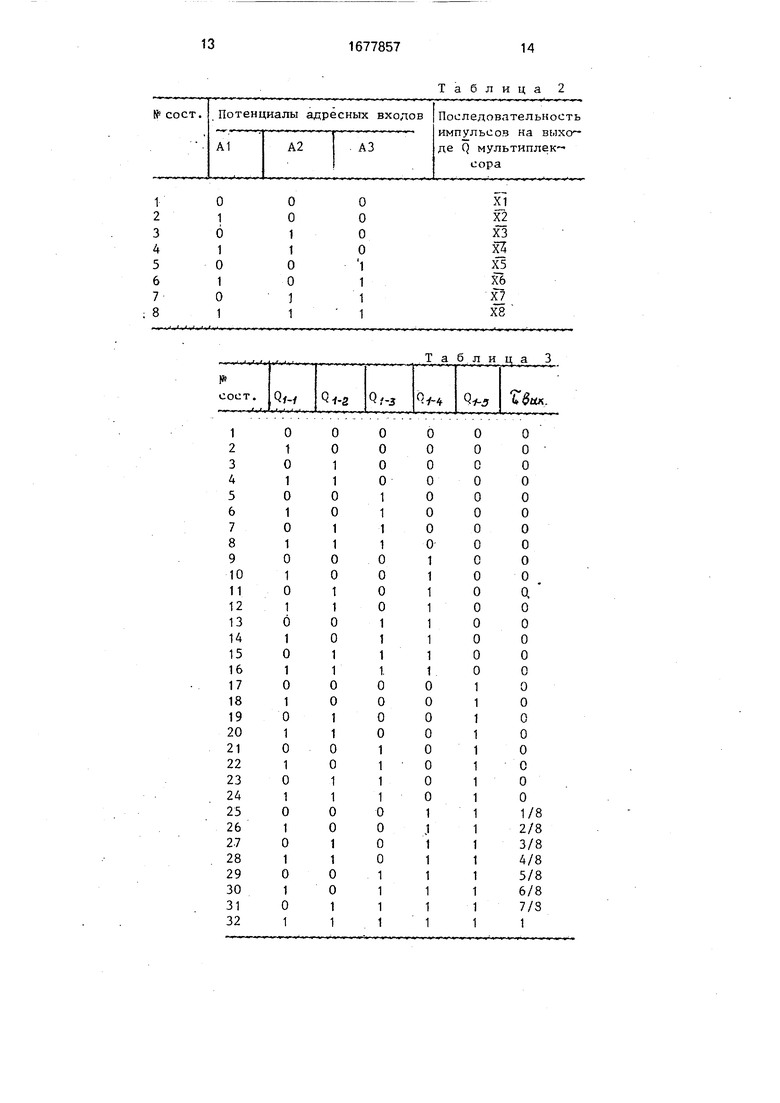

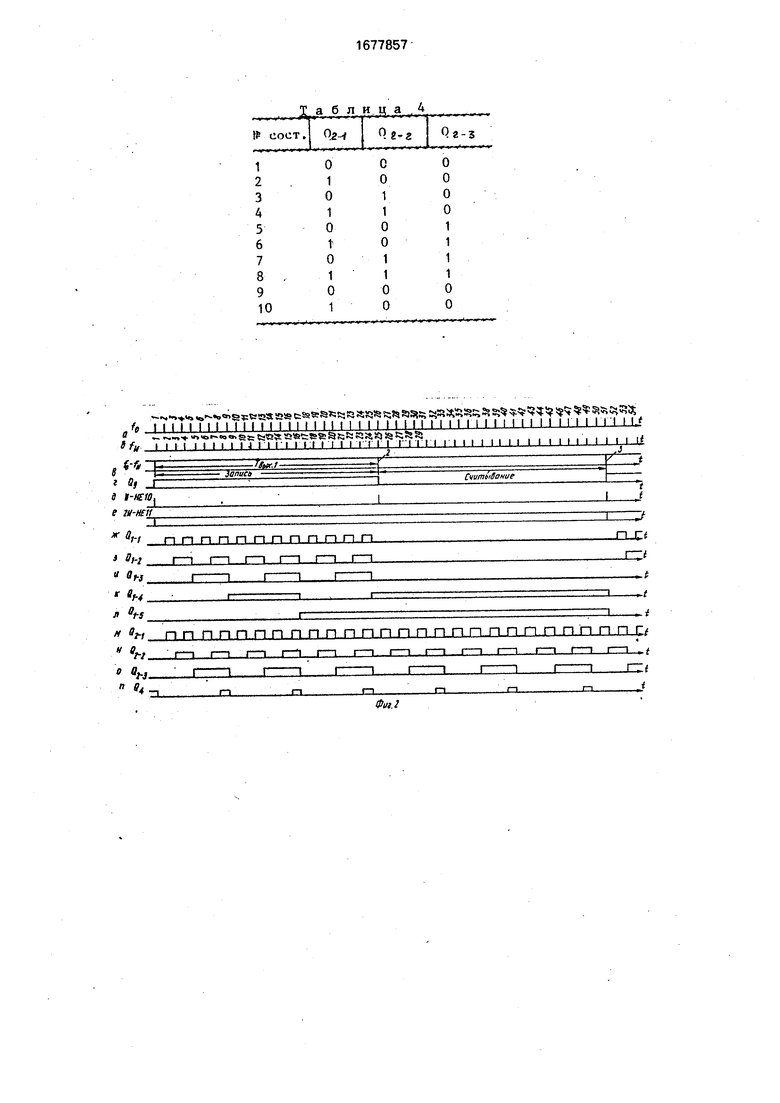

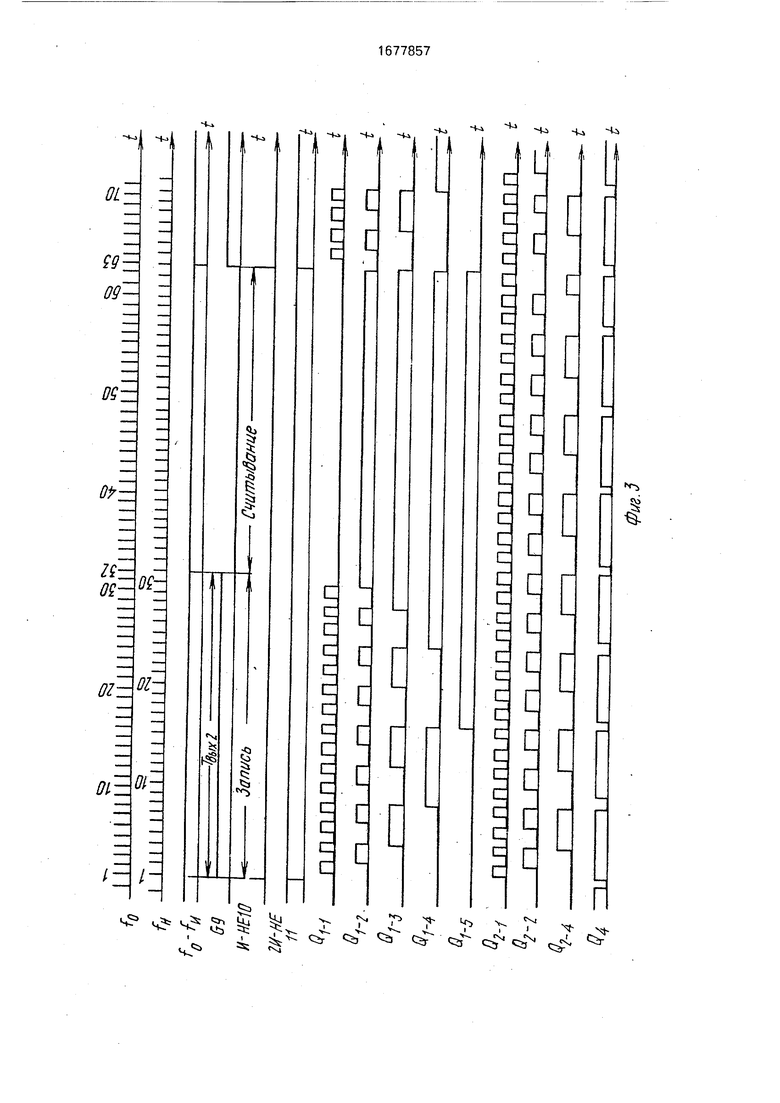

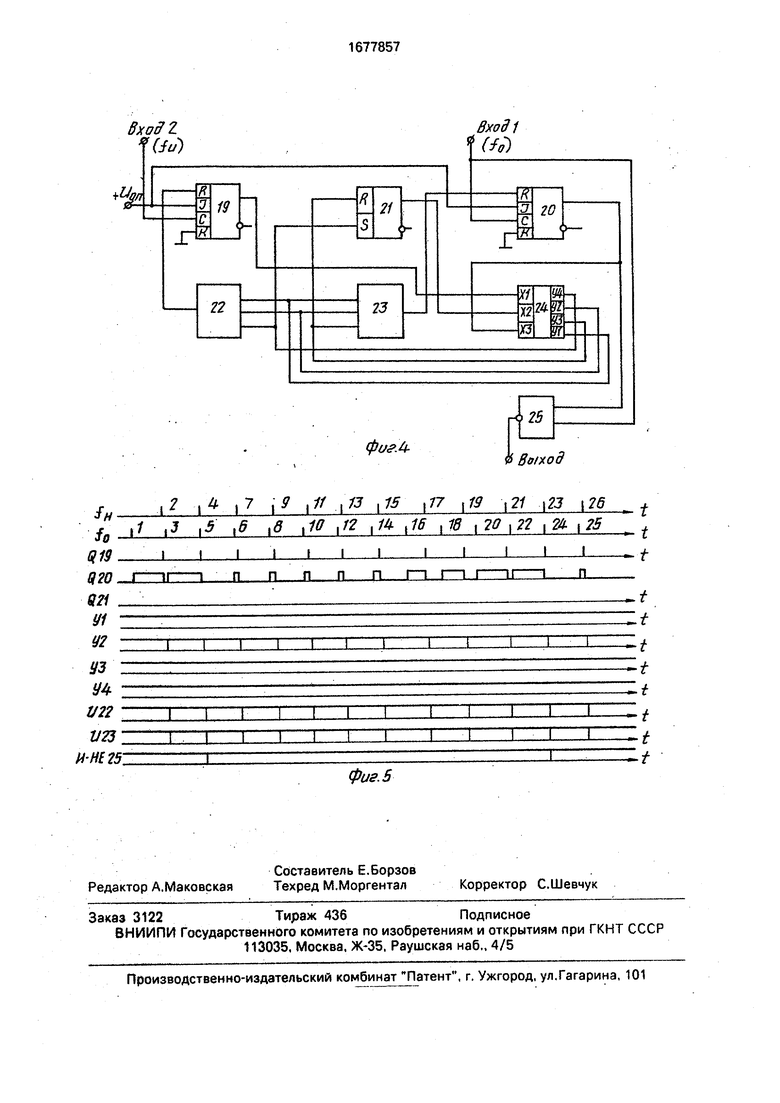

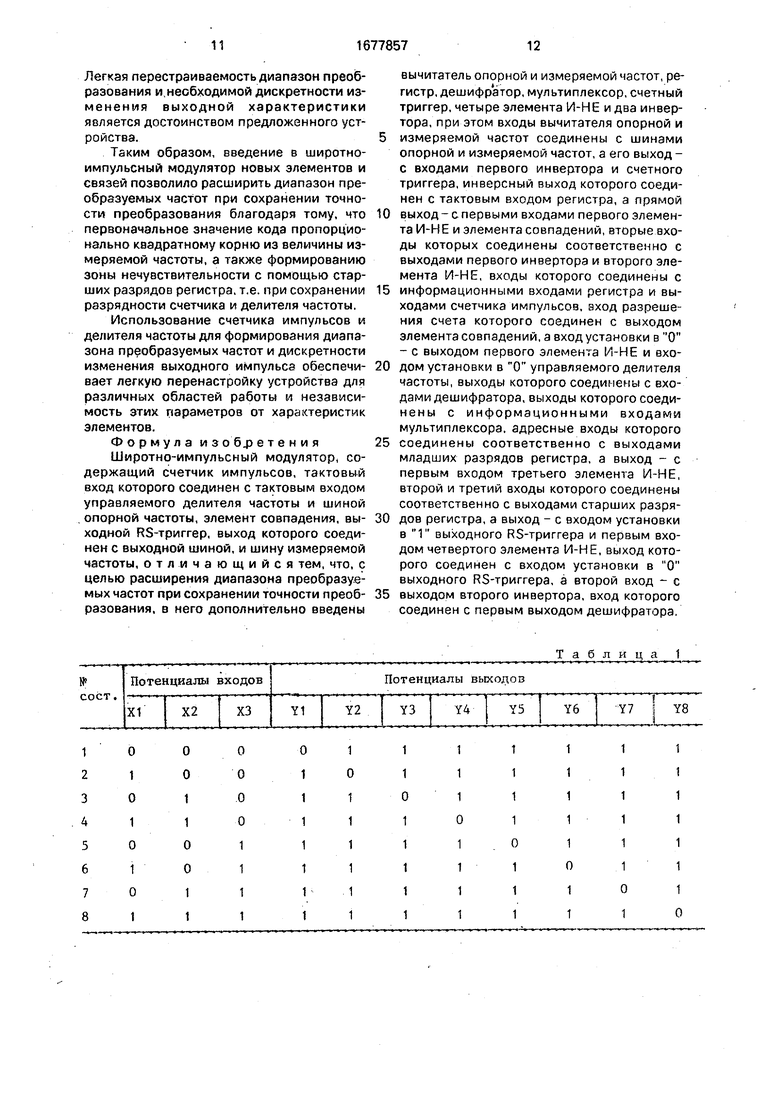

На фиг. 1 приведена функциональная схема широтно-импульсного модулятора; на фиг. 2, 3 - временые диаграммы его работы; на фиг. 4 - пример выполнения вычи- тателя опорной и измеряемой частот; на фиг. 5 - временные диаграммы его работы.

Широтно-импульсный модулятор содержит счетчик 1 импульсов, управляемый делитель 2 частоты, элемент И-НЕ 3, выходной RS-триггер 4, выходную шину 5. шину 6 опорной частоты, шину 7 измеряемой частоты, вычитатель 8 опорной и измеряемой частот, счетный триггер 9, инвертор 10, элемент И-НЕ 11, элемент 12 совпадений, регистр 13, дешифратор 14, мультиплексор 15, инвертор 16, элементы И-НЕ 17, 18, при этом шина б опорной частоты соединена с тактовыми входами счетчика 1 импульсов, управляемого делителя 2 частоты и одним входом вычитателя 8 опорной и измеряемой частот, а выход - с входами инвертора 10 и счетного триггера 9, инверсный выход которого соединен с тактовым входом регистра 13, а прямой - с первыми входами элемента И-НЕ 11 и элемента 12 совпадений, вторые входы которых соединены соответственно с выходом инвертора 10 и выходом элемента И-НЕ 3,входы которого соединены с информационными входами регистра 13 и входами счетчика 1 импульсов, вход разрешения счета которого соединен с выходом элемента 12 совпадений, а вход установки в О -с выходом элемента И-НЕ 11 и входом установки в О управляемого делителя 2 частоты, выходы которого соединены с входами дешифратора 14, выходы которого соединены с информационными входами мультиплексора 15, адресные входы которого соединены соответственно с выходами младших разрядов регистра 13, а выход - с первым входом элемента И-НЕ 18, второй и третий входы которого соединены соответственно с выходами старших разрядов регистра 13, а выход - с первым входом элемента И-НЕ 17 и с входом установки в 1 выходного RS-триггера 4, выход которого соединен с выходной шиной 5, а вход установки в О - с выходом элемента И-НЕ 17, второй вход которого соединен с выходом инвертора 16, вход которого соединен с первым выходом дешифратора 14,

Вычитатель 8 опорной и измеряемой частот может быть выполнен на JK-триггерах

19, 20. RS-триггере 21, элементах 22, 23 совпадений, дешифраторе 24 и элементе И-НЕ 25. при этом К-входы триггеров 19, 20 соединены с общей шиной, J-входы - с шиной

Лог. 1, тактовый вход триггера 19 соединен с шиной 7 измеряемой частоты, его вход установки в О - с выходом элемента 22 совпадений, а его прямой выход - с первым входом дешифратора 24, второй вход кото0 рого соединен с прямым выходом RS-триггера 21, а третий - с прямым выходом триггера 20 и первым входом элемента И- НЕ 25, выход которого является выходом вычитателя, а второй вход соединен с ши5 ной 6 опорной частоты и с тактовым входом триггера 20, вход установки в О которого соединен с выходом элемента 23 совпадений, первый и второй входы которого соединены соответственно с первым и вторым

0 входами элемента 22 совпадений и первым и вторым выходами дешифратора 24, третий выход которого соединен с третьим входом элемента 23 совпадений и входом установки в О триггера 21, а четвертый выход - с

5 третьим входом элемента 22 совпадений и входом установки в 1 триггера 21.

Широтно-импульсный модулятор работает следующим образом.

Счетный триггер 9 делит импульсы раз0 ностной частоты на 2 (эпюры фиг.2г). На выходе элемента 11 формируются узкие импульсы разностной частоты, поделенной на 2 (эпюры фиг.2е), которые используются для начальной установки счетчика 1 и делителя

5 2 в нулевое положение. С приходом первого импульс разностной частоты (фиг.2в) все триггеры счетчиков 1 и делителя 2 устанавливаются в нулевое положение. Триггер 9 опрокидывается в состояние 1 (эпюры

0 фиг.2г). На выходе элемента 3 потенциал равен 1, по входам и на выходе элемента 12 потенциалы равны 1, поэтому счетчик 1 и делитель 2 начинают изменять свои состояния в соответствии с эпюрами фиг.2ж-о. На

5 инверсном выходе триггера 9 Qg О, этот потенциал поступает на тактовый вход С регистра 13 и запрещает запись информации в триггеры регистра 13. С приходом второго импульса разностной частоты

0 (фиг.2в) триггер 9 опрокидывается в противоположное состояние. При этом потенциал Qg 0 через элемент 12 поступает на вход V разрешения счета счетчика 1. При V 1 счетчик 1 работает в режиме деления вход5 ной частоты. При V 0 триггеры счетчика не переключаются, счетчик работает в режиме хранения записанной информации.

Регистр 13 работает в режиме параллельного ввода (на входы D1-D5) - параллельного вывода (с выходов QI-IV- 61-5)

информации. Запись информации с входов на выходы регистра осуществляется при поступлении положительного фронта J (0,1) напряжения по тактовому входу С.

Вычитатель 8 частот с элементами 9-12. осуществляет следующие функции: при f0 fu импульсы разностной частоты форми- руются на выходе вычитателя 8 частот. Триггер 9 делит эти импульсы на 2 и формирует полупериоды с потенциалом Qg, равным 1 и О, с частотой

fo-fu

выходе элемента 11 формируются узкие имfo -fu пульсы с частотой причем момент

появления этих импульсов совпадает с на- чалом положительного полупериода импульса Qg (эпюры фиг.2в-е).

Полупериод частоты с потенциалом Qg 1 назовем тактом записи. С началом этого такта счетчик 1 и делитель 2 обнуляются узким импульсом с выхода элемента 11 и начинают менять свои состояния по мере поступления импульсов fo. Регистр 13 заблокирован сигналом по входу С Qg О, его триггеры сохраняют прежнее состояние, записанное до начала такта записи.

Следующий полупериод частоты

Ј t

-2-х-- является тактом считывания, при

этом импульс на выходе элемента 11 не формируется, потенциал Qg 0. Счетчик 1 потенциалом V 0 останавливается, регистр положительным фронтом импульса 0-9 ,1) переписывает содержимое счет- чика 1 на свои выходы.

С формированием 3-го импульса частоты (fo-fu)(фиг.2г) потенциал Qg 1, формируется узкий импульс по выходу элемента 11, это следующий такт записи. Счетчик 1 и делитель 2 обнуляются и начинают заполняться импульсами f0, регистр 13 хранит состояние, записанное в предыдущий полутакт записи, процесс повторяется.

Таким образом, часть устройства на эле- ментах 1, 3. 8-13 преобразует разность частот (fo-fu) в код, меняющийся один раз за

fo-fu

интервал времени в функции

входной частоты fu.

Моменты появления импульсов f0, fu, такты записи и считывания и импульсы на выходах триггеров счетчика и делителя в функции текущего значения времени приведены на фиг. 2 и 3 при различных соотноше- ниях частот f0 и fu.

Работа дешифратора 14 в зависимости от потенциалов напряжений, поступающих

5

10

15 2025

OQ

35

40 45

50

55

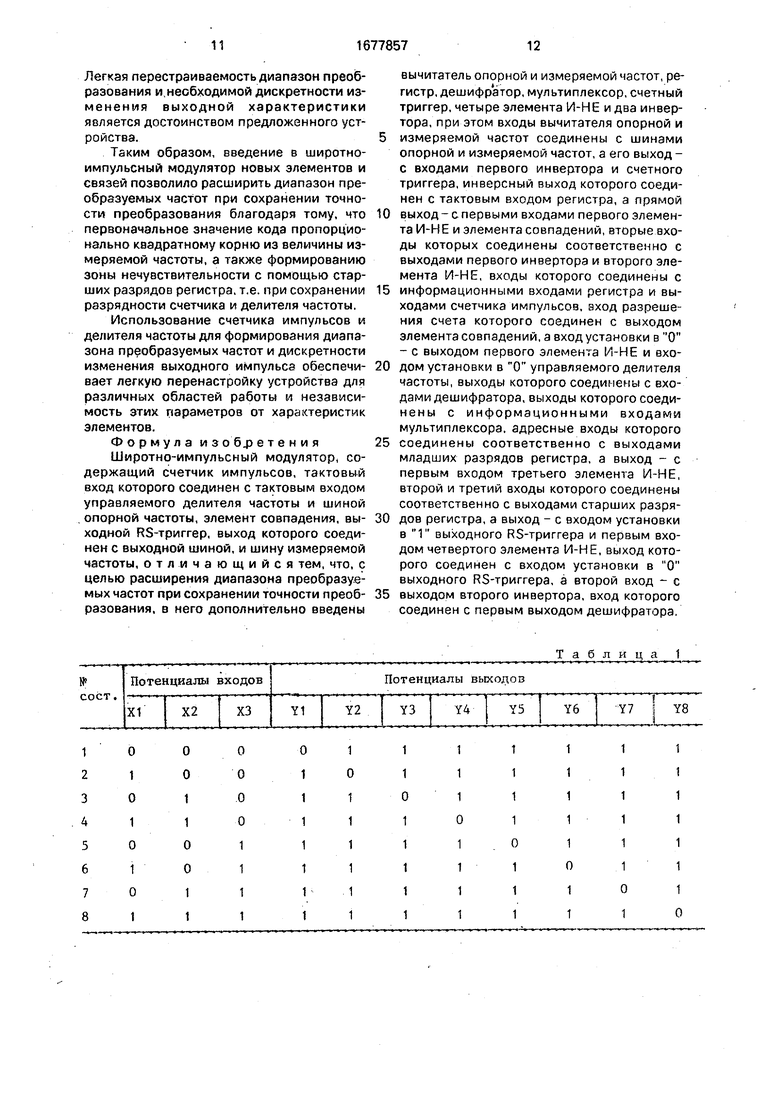

на его входы, поясняется табл. 1, В табл. 1 индексами X обозначены входы дешифратора, индексами Y - его выходы.

В качестве RS-триггера используется триггер, который при подаче О на вход R принимает состояние 0 0, при подаче О на вход S - состояние Q 1, при подаче 1 на входы R и S остается в прежнем состоянии.

Работа мультиплексора 15 заключается в том. что в зависимости от потенциалов по его адресным входам на выходе мультиплексора подключается один из инвертированных сигналов, поступающих на его информационные входы, согласно табл. 2.

Потенциалы на выходах счетчика 1 при поступлении импульсов f0 на тактовый вход Т приведены в табл. 3. Потенциалы приведены в предположении, что счетчик работает в режиме деления частоты при потенциале разрешающего входа V 1.

В табл. 4 приведены потенциалы на выходах триггеров делителя 2 частоты при отсутствии управляющих сигналов по входам R триггеров, т.е. при R 1.

В зависимости от соотношений между значениями частот f0 и fu можно выделить три рабочие области работы устройства:

1)между соседними импульсами вычитателя 8 частоты формируется не более 24 импульсов частоты f0;

2)между соседними импульсами вычитателя 8 частоты формируется от 25 до 31 импульса частоты f0;

3)между соседними импульсами вычитателя 8 частоты формируется 32 и более импульсов частоты f0.

Для первой рабочей области в такт записи счетчик 1 с приходом импульса с потенциалом входы R с выхода элемента 11 переходит в первое состояние согласно табл, 3, делитель 2 частоты - в первое состояние согласно табл. 4. При этом согласно табл. 1 формируется потенциал О на выходе У1 дешифратора 14, который через элементы 16 и 17 поступает на вход R триггера 4 и переводит его в состояние Q4 0.

На выходах триггеров старших разрядов регистра 13 Qi-4 и QI-S формируются потенциалы в состояниях 1-14 согласно табл. 3. Один или оба из них имеют при этом потенциал О, то есть на выходе элемента 18 потенциал всегда будет соответствовать Г, а выходной RS-триггер 4 всегда будет оставаться в состоянии QA - 0. Таким образом, если между соседними импульсами вычитателя 8 частоты формируется не более 0-24 импульса частоты fo, то на выходе устройства формируется постояный сигнал 04 0.

Для второй рабочей области, когда между соседними импульсами вычитателя 8 частоты fo-fu формируется от 25 до 31 импульса частоты f0, на выходах старших разрядов регистра 13 Q-м и Qi-s потенциалы равны 1, поэтому нет внешней блокировки элемента Т8 (по его входам И, запускаемым от регистра 13, поступают потенциалы 1), в этой области существует пропорциональная зависимость между величиной кода и шириной выходного импульса устройства.

Для получения характеристики с изменением относительной длительности импульса от О до 1 с увеличением числа импульсов от 25 до 31 должна пропорционально увеличиваться длительность импульса с состоянием 1.

Проанализируем два крайних случая. Пусть между двумя соседними импульсами вычитателя 8 частоты fo-fu формируется 25 импульсов частоты f0. Этот случай иллюстрируется эпюрами фиг. 2 и характеризуется окончанием такта записи при 25-м состоянии счетчика 1 согласно табл. 3.

Если в промежуток времени Твых 1 -гт- поступает 25 импульсов частоты f0 и

TO и

24 импульса частоты fu, то можно высчитать величину частоты fui начала диапазона регулирования, приняв конкретно величину опорной частоты f0 1000 Гц. Твых.1 25-То 24TMI; fui fo 24/25 960 Гц.

В начале такта считывания по выходам счетчика 1 сформирован сигнал QM 0, Qi-2 0, Qi-з 0, Qi-4 1, Qi-5 1, который согласно табл. 3 соответствует 25-му состоянию счетчика 1. Для статического состояния, при неизменной частоте fu fui. по мере прихода 1-51 импульсов частоты f0 (эпюры фиг. 2) на выходе мультиплексора 15 А1-АЗ подаются сигналы А1 О, А2 О, A3 0. При этом согласно таблице истинность работы мультиплексора 15 (табл. 2) на выход мультиплексора 15 подается инвертированный сигнал с его входа Х1, который соединен с выходом У8 дешифратора 14. Согласно таблице истинности работы дешифратора 14 (табл.1) на выходе У8 формируется потенциал У8 0 при подаче на входы дешифратора 14 потенциала Х1 1, Х2 1, ХЗ 1. Согласно табл. 4 такие потенциалы на выходах триггеров делителя 2 частоты формируются с приходом каждого 8-го импульса по тактовому входу Т делителя 2.

Анализ эпюр фиг. 2 показывает, что при записи на триггерах регистра 13 25-го состояния счетчика 1 согласно табл. 3 на выходе устройства формируются импульсы с длительностью в 1/8 часть периода выходного напряжения (1/8 часть периода с состоянием 1).

Проанализируем ситуацию, когда меж- ду двумя соседними импульсами вычитателя 8 частоты f0-fu поступает 31 импульс частоты f0 и 30 импульсов частоты fu (фиг.З). Вычислим частоту fU2 конца диапазона регулирования при to 1000 Гц,

Твых.2 змо fu2 frf зо/31

967,74 Гц.

Таким образом, при изменении длительности выходного устройства по всему диапазону регулирования изменение изме- 5 ряемой частоты составляет 967,74 - 960 7,74 Гц. Относительное изменение частоты 7.7-100%,

д%

64

;0,8%

составляет величину менее 1 %.

В начале такта считывания (эпюры фиг. 3) по выходам счетчика 1 сформирован сигнал QM 0, Qi-2- Qi-5 1, который согласно табл. 3 соответствует 31-му состоянию счетчика 1. Для статического состояния при неизменной частоте fu fui, по мере прихода 1-70 импульсов частоты f0 на входы мультиплексора 15 А1-АЗ поступают сигналы А1 О, А2 1, A3 1. При этом согласно таблице истинности работы мультиплексора 15

(табл. 5) на выход мультиплексора 15 подается инвертированный сигнал с его входа Х7, который соединен с выходом У2 дешифратора 14. Согласно таблице истинности работы дешифратора 14 (табл. 1) на выходе У2

формируется потенциал У2 0 при подаче на входы дешифратора Х1 1, Х2 О, ХЗ 0. Согласно табл. 4 такие потенциалы на выходах триггеров делителя 2 частоты формируются с приходом каждого второго импульса

по тактовому входу Т делителя 2.

Анализ эпюр фиг. 4 показывает, что при записи на триггерах регистра 13 31-го состояния счетчика 1 согласно табл. 3 на выходе устройства формируются импульсы с длительностью в 7/8 часть периода выходного напряжения.

Для третьей рабочей области, когда между двумя соседними импульсами вычитателя 8 частоты формируются 32 и более

импульсов частоты f0, от 32-го импульса (согласно табл. 3) на выходе элемента 3 формируется потенциал О, который поступает на вход разрешения счета V счетчика 1 и блокирует его работу в 32-м состоянии.

При V 0 счетчик 1 хранит ранее записанную информацию. При подаче нулевого потенциала на вход R счетчика 1 его триггеры переходят в состояние Qi-icr - Qi-5cr 0, то есть Y 1, блокировка снимается. Поэтому в начале каждого такта записи счетчик 1

переходит в 1-е состояние согласно табл. 3. На выходах триггеров регистра 13 записаны потенциалы QM - Ch-s 1 (32-е состояние). На адресных входах мультиплексора 15 при этом А1 - A3 1. Согласно таблице истинности мультиплексора 15 (табл. 2) при этом на его выход подключается инвертированный сигнал с его входа Х8, который соединен с выходом У1 дешифратора 14. Согласно таблице истинности работы дешифратора 14 (табл. 1)на выходеУ1 формируется потенциал У1 0 при подаче на его входы потенциалов Х1 - ХЗ 0. Согласно табл. 4 такие потенциалы на выходах триггеров делителя 2 частоты формируются с приходом каждого 1-го импульса по тактовому сьходу Т делителя 2. Импульс с потенциалом О с выхода элемента 18 поступает на вход элемента 17 и создает на его выходе потенциал 1, тем самым блокируя прохождение сигнала с потенциалом О на вход R триггера 4.

Таким образом, в третьей рабочей области по входу R RS-триггера 4 не формируются потенциалы R 0, по входу S регулярно проходят импульсы с потенциалом О, поэтому триггер 4 постоянно находится в положении .

Исходя из принципа работы устройства, можно написать следующие уравнения, характеризующие его работы:

, T0NU1 Tul(Nui-l); T0(Nui+10) TU2(NU1+10-1)

О)

где То - период импульсов частоты f0;

Tui, TU2 периоды импульсов частоты fu в начале и в конце интервала .регулирования, соответствующие частотам fui и fU2;

NU1, Nui+10 - код входной частоты в начале и конце интервала регулирования.

Уравнения (1) можно переписать следующим образом:

T0Nui TU1 (Nui - 1 ) ,„.

T0(NU1 +10) Tu2(Nui +10 -1 )( При допущении, что fu2 fui+10, уравнение преобразовывается в вид

Nui2 + 9Nui-(fui + 101 0(3)

При допущении, что Nur 9Nui; fui Ю, пол учаем следующее выражение:

Nui ,(4)

Таким образом, первоначальное значение кода пропорционально не текущему значению измеряемой частоты, а корню квадратному из его величины.

В устройстве принят следующий принцип формирования зоны нечувствительности (0 - fui} и получения регулировочной характеристики. Код измеряемой частоты fu рассматривается в виде кода младших разрядов (Ом - Qi-з) и кода старших разрядов

Qt-4. Ch-s). Младшие разряды используются для формирования всех значений регулируемой длительности е пределах (1/8 - 7/8) относительной длительности ШИМ ГцЫх .э

старшие для получения крайних значений О и 1 и блокировки устройства в этих положениях в зонах нечувствительности.

В последней графе габл. 3 приведены значения гвы в функции общего кода регистрз 13. Как следует из анализа работы устройства, при смене 25-31 состояний кода Ni /Ni (25-31)/ относительная длительность выходных импульсов ШИМ меняется в пределах (1 /8-7 - 8).

Анализируя вес состояния младших

разрядов счетчика 1 по табл. 3, видим, что состояния 25-31 младших разрядов повторяются периодически по мере нарастания кода: при значениях кода 1-7, 9-f, 17-23,

25-3 i могли бы формироваться значения регулируемой длительности в пределах (1/8 - У/8).

С помощью старших разрядов формируются состояния О в пределах кода N (0-24) и состояния 1 в пределах кода Ni 32 (если счетчик 1 имеет больше 32 состояний),

При разделении функций старших и младших разрядов регистра 13 нет необходимости в сравнении накопленного кода с кодом одной установки, вычитания кодов с помощью другой установки, что значительно упрощает схему устройства в целом. В предлагаемом устройстве в пределах

зоны регулирования при NJ 0-24 относительная длительность выходного импульса равна 0; при N, 25-31, гвых 1/8-7/8; при NI 32 Гвых 1, т.е. минимальное значение относительной длительности выходного

импульса равно 0, максимальное - 1, полный динамический диапазон преобразования равен eft .

Анализ работы устройства показывает, что разрядность счетчика 1 определяет диапазон преобразования часгэты fu, в пределах которого относительная длительность выходного импульса устройства (выход См триггера 4) изменяется от 0 до 1.

Чем больше триггеров входит в состав

счетчика 1, тем уже диапазон преобразуемых частот fu, тем выше коэффициент преобразования.

Число разрядов делителя 2 частоты определяет дискретность изменения ширины

импульса на выходе устройства. Чем больше триггеров входит в состав делителя 2 частоты, тем большее число уровней изменения длительности импульса выходного напряжения имеется на выходе устройства.

Легкая перестрзиваемость диапазон преобразования и необходимой дискретности изменения выходной характеристики является достоинством предложенного устройства.

Таким образом, введение в широтно- импульсный модулятор новых элементов и связей позволило расширить диапазон преобразуемых частот при сохранении точности преобразования благодаря тому, что первоначальное значение кода пропорционально квадратному корню из величины измеряемой частоты, а также формированию зоны нечувствительности с помощью старших разрядов регистра, т.е. при сохранении разрядности счетчика и делителя частоты.

Использование счетчика импульсов и делителя частоты для формирования диапазона преобразуемых частот и дискретности изменения выходного импульса обеспечивает легкую перенастройку устройства для различных областей работы и независимость этих параметров от характеристик элементов.

Формула изобретения

Широтно-импульсный модулятор, содержащий счетчик импульсов, тактовый вход которого соединен с тактовым входом управляемого делителя частоты и шиной опорной частоты, элемент совпадения, выходной RS-триггер, выход которого соединен с выходной шиной, и шину измеряемой частоты, отличающийся тем, что, с целью расширения диапазона преобразуемых частот при сохранении точности преобразования, в него дополнительно введены

0

вычитатель опорной и измеряемой частот, регистр, дешифратор, мультиплексор, счетный триггер, четыре элемента И-НЕ и два инвертора, при этом входы вычитателя опорной и измеряемой частот соединены с шинами опорной и измеряемой частот, а его выход - с входами первого инвертора и счетного триггера, инверсный выход которого соединен с тактовым входом регистра, а прямой выход - с первыми входами первого элемента И-НЕ и элемента совпадений, вторые входы которых соединены соответственно с выходами первого инвертора и второго элемента И-НЕ, входы которого соединены с 5 информационными входами регистра и выходами счетчика импульсов, вход разрешения счета которого соединен с выходом элемента совпадений,а вход установки в О - с выходом первого элемента И-НЕ и входом установки в О управляемого делителя частоты, выходы которого соединены с входами дешифратора, выходы которого соединены с информационными входами мультиплексора, адресные входы которого соединены соответственно с выходами младших разрядов регистра, а выход - с первым входом третьего элемента И-НЕ, второй и третий входы которого соединены соответственно с выходами старших разрядов регистра, а выход - с входом установки в 1 выходного RS-триггера и первым входом четвертого элемента И-НЕ, выход которого соединен с входом установки в О выходного RS-триггера, а второй вход - с выходом второго инвертора, вход которого соединен с первым выходом дешифратора.

0

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления инвертором | 1987 |

|

SU1617584A1 |

| Устройство для измерения частоты | 1985 |

|

SU1372243A1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Сеточная модель | 1987 |

|

SU1483469A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Устройство для измерения частоты | 1985 |

|

SU1292162A1 |

| Устройство для вычисления показательных функций | 1981 |

|

SU962928A1 |

| Сумматор-вычитатель частотно-импульсных сигналов | 1991 |

|

SU1807483A1 |

Изобретение относится к импульсной технике и может быть использовано в измерительных системах и системах автоматизированного управления. Цель изобретения - расширение диапазона преобразуемых частот при сохранении точности преобразования. Широтно-импульсный модулятор содержит счетчик 1 импульсов.делитель 2 частоты, выходной RS-триггер 4, выходную шину 5, шины 6, 7 опорной и измеряемой частот, элемент 12 совпадений. Введение в модулятор вычитателя 8 опорной и измеряемой частот, регистра 13, дешифратора 14. мультиплексора 15, счетного триггера 9. элементов 3. 11, 17, 18 и инверторов 10. 16 позволяет расширить диапазон преобразуемых частот при сохранении точности преобразования благодаря тому, что первоначальное значение кода пропорционально квадратному корню из величины измеряемой частоты, а также благодаря формированию зоны нечувствительности с помощью старших разрядов регистра, т.е. при сохранении разр ядности счетчика импульсов и делителя частоты. 5 ил. fe

Т а б л и ц а 1

Таблица 2

О О I I I I О О

о о

I о I о

4

о I о I о

01

6

8 L 9 S «7

е г

i

У Л1в }f и и g в аГ

i98U9l

f 1J U U U U U U U U U U U UU U U

U U U U U U Ll U U U LTLTU U UU U LJTJ U LJTJ LI U UU U U U

- 1I

гю оо г-- г to

U LJ L

ииии

3:

д Мф п

JT

fy

/-/,

о

1-2.

О

S-l,

о

т

т

Ґ-1

/9

П

О

и и и и1 и1 и и

/-;

U U LJULJ UU U ииТГиии /-;

Q

$

4

Л CJ4

f-si 5i

| Устройство для измерения частоты | 1985 |

|

SU1292162A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Широтно-импульсный модулятор | 1984 |

|

SU1288904A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-15—Публикация

1989-01-19—Подача