Устройство относится к области автоматики и вычислительной техники и служит для автоматического контроля преобразователей уголкод.1

В известиом устройстве для автоматической проверки преобразователей угол-код по авт. св. № 251959 имеет место низкая надежность, так как появляются сбои распределителя импульсов.

В предлагаемом устройстве для новышения надежности установлен элемент «ИЛИ, выход которого подключен к дополнительным входам делителя частоты и распределителя, первый вход элемента «ИЛИ соедииен с выходом делителя частоты, а второй вход - с выходом первого разряда распределителя.

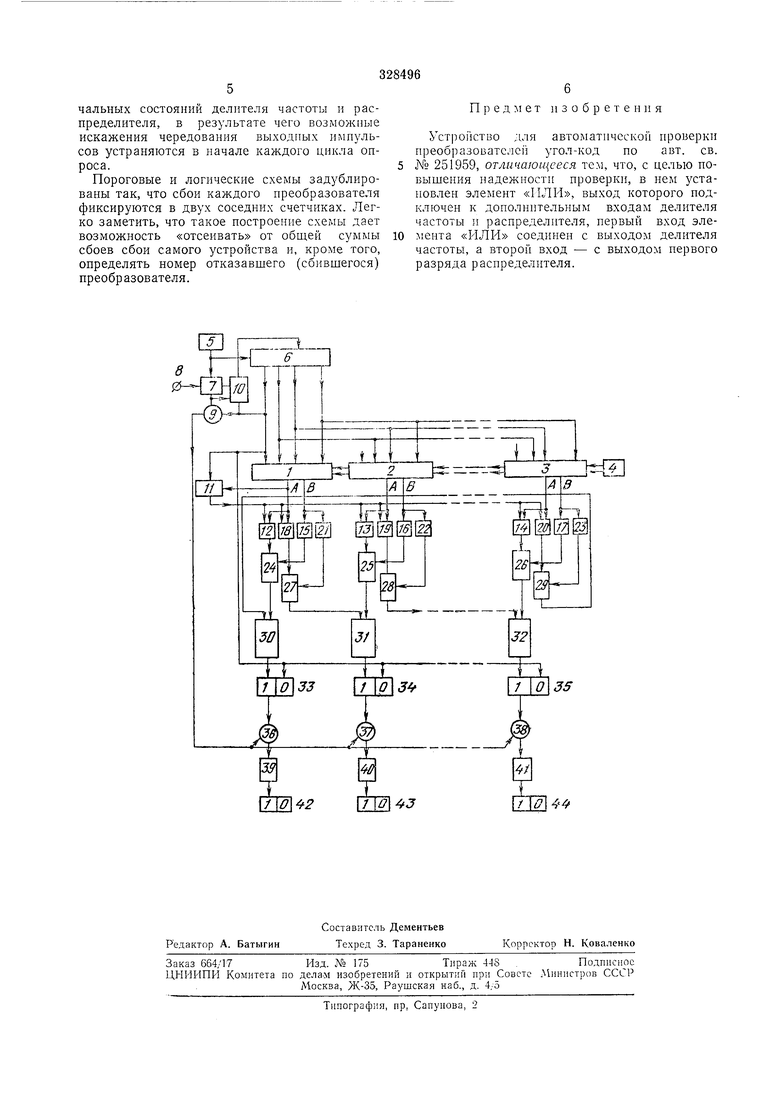

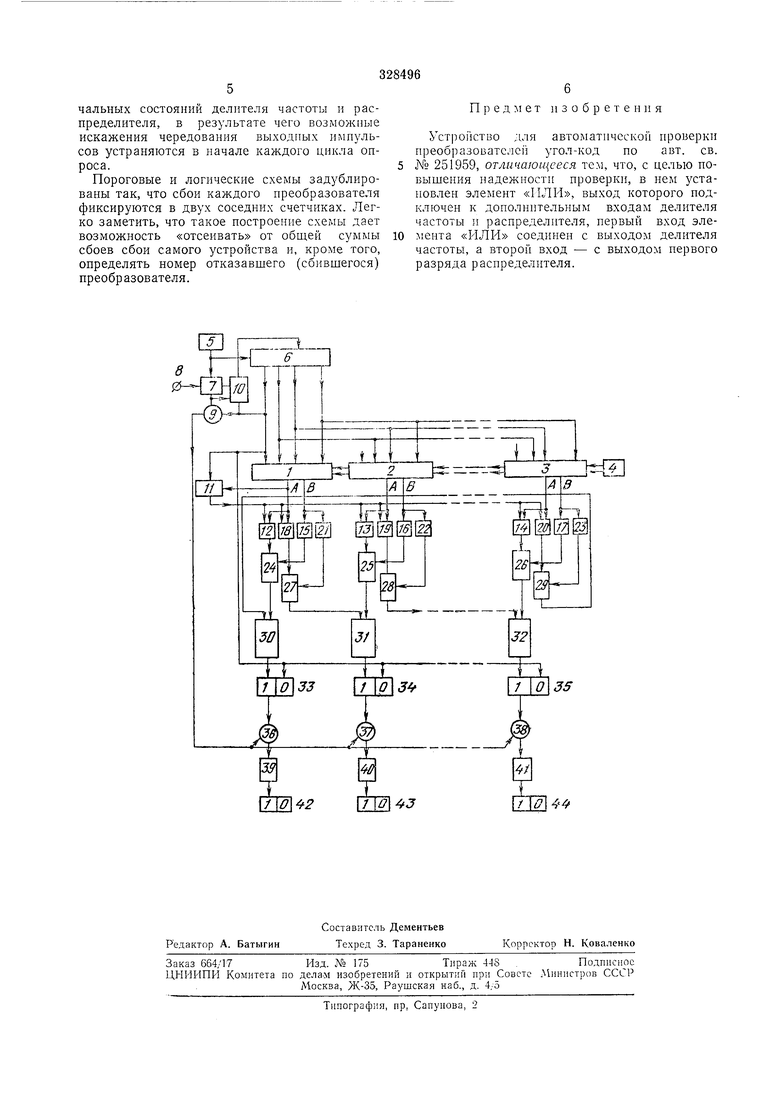

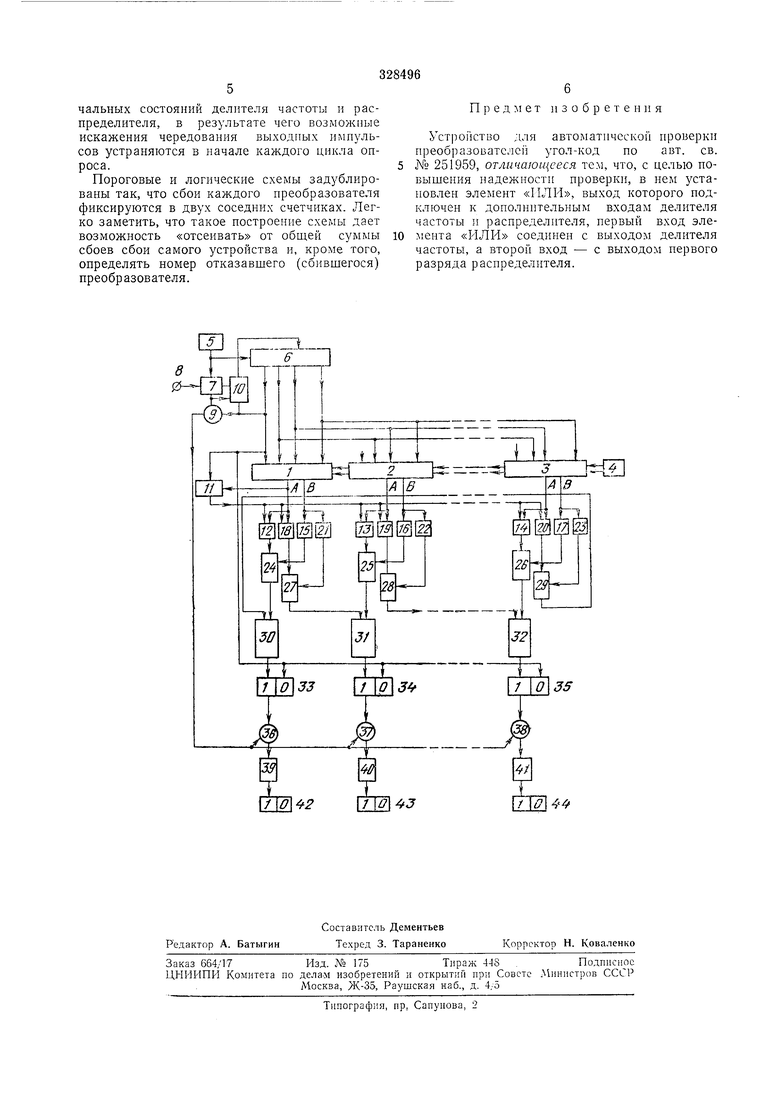

На чертеже представлена функциональная схема устройства.

Схема включает испытываемые преобразователи /, 2, 3 (первый, второй, п-й), посаженные на вал двигателя 4. Генератор имнульсов 5 связан с распределителем 6 и делителем частоты 7, имеющим установочный вход 8. Выход делителя частоты и первый разряд распределителя подключены к элементу совпадения 9 и к элементу «ИЛИ 10, который соединен со входами начальной установки распределителя и делителя частоты.

(за исключением первых разрядов), входами всех преобразователей. Первый разряд распределителя соединен с первым разрядом первого преобразователя и пороговой схемой «И //. На второй вход этой схемы подключен выход Л первого преобразователя. К выходам преобразователей 1, 2, 3 подключены основные пороговые схемы 12, 13, 14 и 15, 16, 17 и резервные пороговые схемы 18, 19, 20 и

21, 22, 23. Кроме того, к дополнительным входам пороговых схем 12, 13, 14 и 18, 19, 20 подведена линия от схемы //. Выходы основных пороговых схем соединены со входами основных логических схем 24, 25, 26, выходы

резервных пороговых схем - с резервными логическими схемами 27, 28, 29.

Все логические схемы связаны с соответствующими схемами несовпадения 30, 31, 32. Связь осуществляется попарно: схемы 24 и 29

соединены со схемой 30, схемы 27 и 25 - со схемой 3, схемы 28 и 26 - со схемой 32.

Схемы песовпадения соединены с единичными входами буфериых триггеров 33, 34, 35. Нулевые входы этих триггеров связаны с первым разрядом распределителя. Выходы схем 30, 31, 32 подключеиы соответственно к вентилям 36, 37, 38, управляющпе входы которых подключены к счетчикам 39, 40, 41. Последние разряды счетчиков нагрул ены на триггеНа каждый из разрядов преобразователей 1, 2, 3 поступают последовательно опрашивающие импульсы от общего распределителя б . Число выходов распределителя равно /С, где Л-разрядпость преобразователей. Продвижение импульсов в распределителе осуществляется генератором 5. Пороговые схемы 12- 23 срабатывают каждый раз, когда выходное напряжение соответствующего преобразователя превышает единичный уровень. Сигналы, прошедшие через пороговые схемы, анализируются логическими схемами 24-29, назначение которых - преобразование 1/-кода в двоичный код. Выходные импульсы каждой соседней пары логических схем принимаются соответствующей схемой несовпадения (например, схема 30 связана со схемой 24 и 29).

Принято считать сбоем несовпадение выходных сигналов любой пары логических схем в данный момент времени. Все преобразователи работают синхронно, с одинаковой начальной установкой, поэтому сигнал на выходе схемы несовпадения указывает на наличие сбоя у одного из нары преобразователей.

Правильность работы схем несовпадения требует полной идентичности кодовых комбинаций па выходе логических схем, для чего необходимо устранить неоднозначность считывания первого разряда любого из преобразователей по отнощению к другим (неоднозначность остальных разрядов устраняется логической схемой). В противном случае кодовые комбинации преобразователей могут различаться на единицу младшего разряда.

С этой целью распределитель опрашивает первый разряд только одного (первого) из испытываемых преобразователей. При этом в качестве выходных сигналов, соответствующих первым разрядам остальных преобразователей, принимается выходной сигнал Л выбранного преобразователя, который поступает па дополнительные входы пороговых схем, связанных с выходами А. Но так как код преобразователя считывается последовательно, необходимо, чтобы связь между выходом А первого преобразователя и входами указанных пороговых схем осуществлялась только па первом такте работы распределителя. Этим требовапиям удовлетворяет включение в устройство схемы «И 11. На управляющий вход этой схемы поступает тактовый импульс от первого разряда распределителя, на пороговый вход - выходные сигналы А первого преобразователя. Схема срабатывает лишь в том случае, если результат считывания первого разряда соответствует 1. Сигналы- других разрядов срабатывания вызвать не могут. Выход схемы связан с упомяпутыми пороговыми схемами А.

Таким образом, на работу устройства не влияет допустимая ошибка младщего разряда преобр азователей.

сбои и других разрядов. По этой причине за один цикл онроса нреобразователя практически невозможно (без неоправданпого усложнения схемы) различить независимые сбои (т. е. сбои, возникщие в различных разрядах преобразователя независимо друг от друга) и зависимые сбои (вызванные сбоями в предыдущих разрядах). Поэтому любое количество сбоев каждой пары преобразователей, отмеченных за один цикл онроса, фиксируется как один сбой этой пары. Фиксация сбоев за один цикл опроса производится буферным триггером (например, триггером 33); фиксацию сбоев каждой пары преобразователей за длительное время осуществляют счетчики 39, 40, 41. О переполнении счетчиков сигнализируют триггеры 42, 43, 44.

Опрос буферных триггеров 33, 34, 35 производится один раз за цикл работы распределителя, при опросе первого разряда (т. е. по 1-му такту). Так как но 1-му такту работы распределителя на все пороговые схемы поступает сигнал (от схемы 11), то схемы несовпадения по 1-му такту не срабатывают.

Поэтому опрос буферных триггеров производится беспрепятственно.

Вентили 36, 37, 38, элемент совпадения 9 и делитель частоты 7 предпазначены для устранения влияния сбоев распределителя 6 па информацию о сбоях преобразователей. Коэффициент пересчета делителя частоты равен /С (число выходов распределителя). В начале работы входом 5 делитель частоты устанавливается Б (/С-1)-е состояние, в результате чего сигнал с выхода делителя частоты появляется па первом такте любого цикла опроса. Таким образом, при правильной работе и делителя частоты и распределителя в начале каждого цикла опроса (на первом импульсе)

элемент совпадения пошлет сигнал к вентилям 36, 37, 38. Тем самым будет разрешен перенос информации из буферных триггеров в счетчики. При сбое раснределителя (или делителя частоты) импульсы на элемент совнадения прпдут разновременно и в итоге на вентили разрешуюший сигнал не поступит.

Очевидно, что одновременный (в одном и том же такте па одном и том же цикле опроса) сбой распределителя и делителя частоты

маловероятен. Следовательно, ошибки, вызванные сбоями распределителя, не будут зафиксированы в счетчиках. Таким образом, достоверность информации, получаемой устройством о сбоях преобразователей, значительно возрастает.

В практических реализациях схемы элемент совпадения соедипяется пе с первым разрядом распределителя, а с разрядом, номер которого определяется количеством тактов,

задерживаемых цепью «преобразователь - выход логической схемы.

чальных состоянии делителя частоты и распределителя, в результате чего возможные искажения чередования выходных имиульсов устраняются в начале каждого цикла онроса.

Пороговые и логические схемы задублированы так, что сбои каждого преобразователя фиксируются в двух соседних счетчиках. Легко заметить, что такое построение схемы дает возможность «отсеивать от общей суммы сбоев сбои самого устройства и, кроме того, определять номер отказавшего (сбившегося) преобразователя.

Предмет изобретения

Устройство для автоматической проверки преобразователей угол-код по авт. св. N° 251959, отличающееся тем, что, с целью повышения надежности проверки, в нем установлен элемент «ПЛИ, выход которого подключен к дополнительным входам делителя частоты и распределителя, первый вход элемента «ПЛИ соединен с выходом делителя частоты, а второй вход - с выходом первого разряда распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИБ-ЧИОТЬНА | 1971 |

|

SU291227A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕЙ УГОЛ — КОД | 1969 |

|

SU251959A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕЙ «УГОЛ — КОД» | 1973 |

|

SU370629A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕЙ УГОЛ —КОД | 1972 |

|

SU360687A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕЙ «УГОЛ —КОД» | 1971 |

|

SU304621A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ РЕГИСТРАЦИИ | 1973 |

|

SU404112A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕЙ УГОЛ - КОД | 1971 |

|

SU291225A1 |

| @СЕСОЮЗН*.Я | 1973 |

|

SU378919A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬBr^irr^f^^.ocitJ и а ^ и»^ ^^- \^ f "^.' -^' S i.' . /I'i.';'^-:; •^;-"'-J ; iXJ'4-'^, | 1972 |

|

SU332567A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

Даты

1972-01-01—Публикация